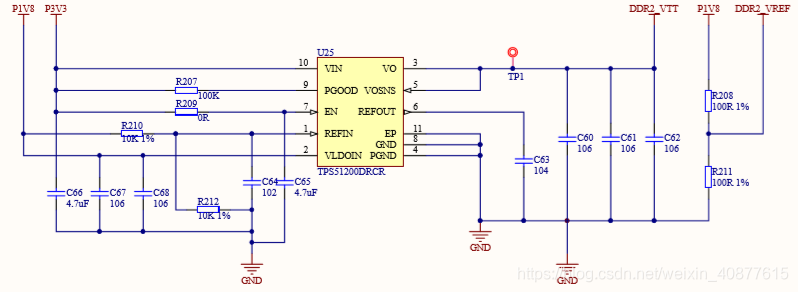

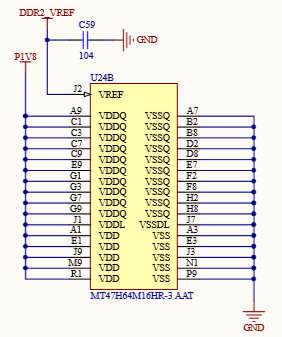

一、DDR电源:DDR一般需要3种电源,分别为:VDDQ、VREF、VTT。其中VTT和VREF的电平是一样的,为VDDQ电平的一半。VREF消耗的电流很小,可以通过分压电阻网络从VDDQ分压得到;而VTT是端接电源,电流会比较大,能达到百毫安级别,如果使用分压电阻功耗消耗过大,因此需要单独的DDR电源调节器芯片来生成VTT。VTT端接电源线的过流能力需要考虑周到,尽量加粗VTT的电源线以增强其载流能力。

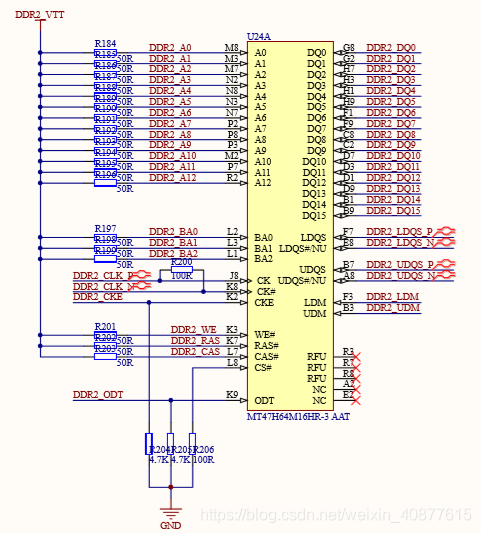

二、DDR终端匹配:ODT为内部核心终结引脚,从DDR2开始内存内部集成了终结电阻器,把原来在主板上的终结电路移植到了内存芯片内部。当内存芯片处于写数据状态时,此时内存颗粒是接收端,需要端接匹配电阻,因此需要打开ODT功能;同理当内存芯片处于读数据状态时,此时内存颗粒是发送端,不需要端接电阻,因此需要关闭ODT功能。正是有了ODT功能,DDR内存在PCB布线的时候数据线不需要进行端接匹配处理,因为内存芯片内部集成了端接电阻。

三、DDR信号线分组:将DDR布线的信号进行分组,可以分为时钟线、地址线、命令控制线、数据线四部分。

(1)、时钟线的布线规则:为高速差分信号线,按照差分布线规则进行布线,而且需要在接收端进行阻抗匹配。

(2)、地址线与命令控制线布线规则:地址和命令信号线要进行端接匹配,通过匹配电阻接端接电源VTT。

(3)、数据线布线规则:数据线由于采用了ODT技术,因此不需要外部进行端接匹配。

另外需要注意的是:对于时钟线、地址线、命令控制线和数据线,对等长布线要求较高,除了每一组信号线内部要求等长布线以外,还要保持时钟线、地址线和数据线等组间信号线尽量保持等长。尽量保持同组信号线保持在同层,避免跨层布线。对于差分信号线,为了避免信号间的串扰,要使用3W原则进行布线。除此之外,为了使DDR电路具备完整的参考地平面和电源平面,因此在DDR保护区内不得出现与DDR无关的信号且信号走线的参考平面不能中断。DDR的PCB单端走线阻抗一般控制为50欧,差分走线阻抗一般控制为100欧。对于多块DDR芯片的布局布线,根据菊花链的拓扑结构进行布置即可。

四、DDR时序同步:作为源同步系统的DDR电路设计来说,时序控制至关重要,共有三组时序设计要求如下:

(1)、DQ和DQS的等长关系:所有数据线DQ参考DQS的差分线等长,DQS差分线误差控制在5mil,所有数据线误差控制在DQS目标长度的15mil。

(2)、时钟CLK和地址线、命令控制线的等长关系:所有地址和命令控制线参考差分时钟线CLK等长,所有地址和命令控制线误差控制在时钟CLK目标长度的50mil。

(3)、时钟CLK和DQS线的等长关系:对于DDR2来说,时钟CLK和DQS线的时序关系是松散的时序关系,它们之间的时序参数为,一般控制在100mil即可,但是在DDR3中,时钟CLK和DQS线的时序没有严格要求。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?