模数转换器(ADC)

C2000 器件支持多个 12 位和/或 16 位模数转换器 (ADC)。每个 ADC 模块均具有单个采样保持 (S/H) 电路,使用多个 ADC 模块可实现同时采样或独立操作(顺序采样)。ADC 模块采用逐次逼近 (SAR) 型 ADC 实现。

差分信号模式

在此模式下,对一对引脚(正输入 ADCINxP 和负输入 ADCINxN)进行采样,施加到转换器的输入是两个引脚之间的差值 (ADCINxP – ADCINxN)。差分信号模式的优势在于能够消除可能引入到两个输入端的噪声。

单端信号模式

在单端模式下,单个引脚(ADCINx)被采样并应用于转换器的输入。

转换开始时间 (SOC)

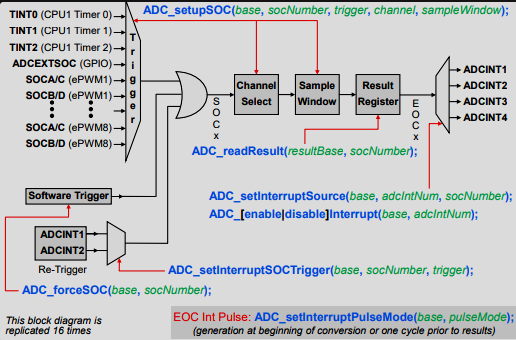

ADC 触发和转换序列由一系列转换开始 (SOCx) 配置寄存器管理。每个 SOCx 寄存器配置一个单通道转换,其中 SOCx 寄存器指定启动转换的触发源、要转换的通道以及采集样本窗口持续时间。可以为同一个触发器、通道和/或采集窗口配置多个 SOCx 寄存器。将多个 SOCx 寄存器配置为使用同一个触发器将导致该触发器执行一系列转换;而为同一个触发器和通道配置多个 SOCx 寄存器则可能会对信号进行过采样。

可用于启动 ADC 转换的各种触发源包括通用定时器、ePWM 模块、外部引脚以及软件触发。此外,ADCINT1 或 ADCINT2 的标志设置可配置为触发源,用于连续转换操作。ADC中断逻辑最多可产生四个中断。 SOC 0至15的结果分别出现在结果寄存器0至15中。

F28004x的ADC触发示意图如下:

上图是一个概念图,突出显示了单个 ADC 转换启动功能流程(从触发到中断生成)。

ADC触发

每个 ADC 模块都有多个触发源可用于启动 ADC 转换。

触发的要点:

- 当 ADC 转换可以采样时,相对于控制环路(尤其是采用 EPWM 触发器 + EPWM 执行方案),其采样粒度和耦合度更佳,这有助于避免噪声并优化响应时间(相位裕度)。

- 并行 ADC 允许真正的同步采样,这对于相关信号(例如电源的电压 + 电流)非常有用。

- 采样率可通过软件配置,因此可以动态调整 ADC 采样以匹配输入信号。

举例:

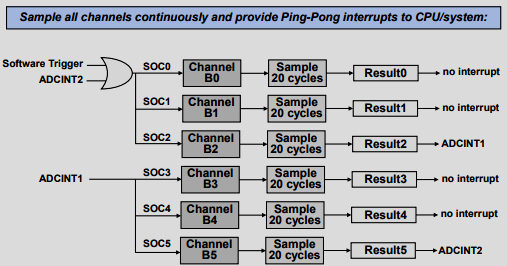

ADC ping-pong 触发示例显示,B0 至 B5 通道正在进行转换,最初由软件触发。B2 通道转换完成后,生成 ADCINT1,并触发 B3 通道。B5 通道转换完成后,生成 ADCINT2,并反馈回来,重新开始转换过程。此外,ADCINT1 和 ADCINT2 用于管理中断服务程序的ping-pong 中断。

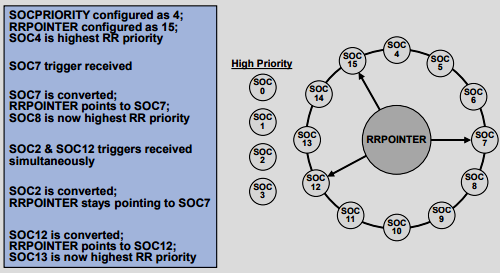

ADC转换优先级

当同时收到多个触发信号时,ADC 转换优先级将决定这些触发信号的转换顺序。

ADC 支持三种不同的优先级模式:

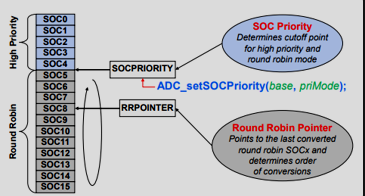

在 ADC 转换优先级功能图中,转换启动优先级控制寄存器包含两个位字段。转换启动优先级位字段确定高优先级和循环模式之间的分界点,而循环指针位字段包含最后转换的循环转换启动指针,该指针决定了转换的顺序。

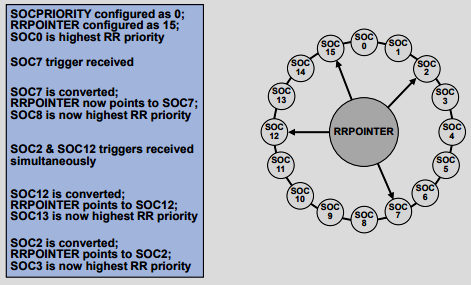

循环优先级(Round Robin Priority)(默认)

- 没有 SOC 开始就比其他 SOC 具有更高的优先级。

- 优先级取决于在循环缓冲区中运行的循环指针。

下图是仅配置了循环模式:

高优先级(High Priority)

- 高优先级 SOC 将在当前转换完成后中断循环轮,并将自身插入到下一个转换中。

- 可以将一个或多个 SOC 指定为“高优先级”。

- 高优先级模式首先分配给编号较低的转换启动触发器,然后按编号递增的顺序分配。

- 如果同时发生两个高优先级转换启动触发器,则数字较低的触发器优先。

- 转换完成后,循环轮将从中断处继续运行。

下图是仅配置了循环模式和高优先级模式:

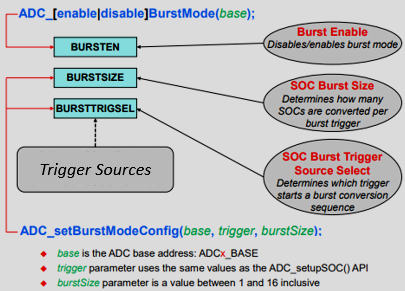

循环突发模式(Round Robin Burst Mode)

允许单个触发器转换循环轮中的一个或多个 SOC,对于所有循环 SOC(非高优先级),使用 BURSTTRIG 而非 TRIGSEL 来选择突发大小和触发源。

循环突发模式利用 ADC 突发控制寄存器来启用突发模式、确定突发大小并选择突发触发源。

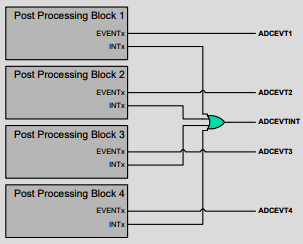

后处理块

为了进一步增强 ADC 的功能,每个 ADC 模块都包含后处理模块 (PPB),每个 PPB 都可以链接到任意 ADC 结果寄存器 (ADCRESULTx)。PPB 可用于失调校正、计算设定点误差、检测限值和过零点,以及触发至采样延迟捕获。

- 失调校正:同时消除可能由外部传感器和信号源引起的与 ADCIN 通道相关的偏移(零开销;节省周期)。

- 计算设定点误差:减去一个参考值,该参考值可用于自动计算设定点或预期值的误差(减少样本到输出的延迟和软件开销)。

- 检测限值和过零点: 自动检查高/低限或零交叉,并可生成 ePWM 跳闸和/或中断(减少样本到 ePWM 的延迟并降低软件开销;基于超出范围的 ADC 转换跳闸 ePWM,无需 CPU 干预),这对于安全谨慎的应用很有用。

- 触发至采样延迟捕获:能够记录 SOC 触发和开始采样之间的延迟(允许软件技术减少延迟误差)。

- 后处理块中断事件:每个 ADC 模块都包含后处理块。每个后处理块可以与 16 个 ADCRESULTx 寄存器中的任意一个关联。

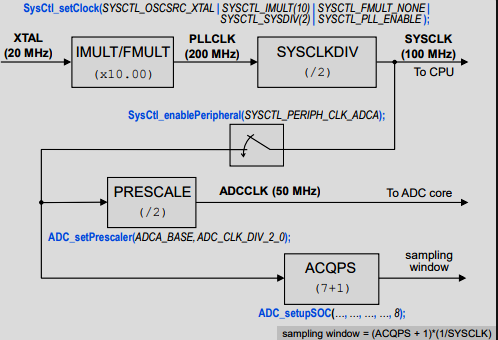

ADC时钟流程

要配置 ADC 模块的时钟,首先需要生成 SYSCLK。该时钟是 CPU 频率,可通过 SysCtl_setClock() 函数进行配置。该函数允许您选择输入时钟源并配置 PLL 设置。设置好 SYSCLK 后,必须使用 SysCtl_enablePeripheral() 函数启用每个 ADC 模块的时钟。启用时钟后,可以通过 ADC_setPrescaler() 函数选择一个预分频器值,该值会降低 SYSCLK 频率以传输至 ADC 核心。请务必查看数据手册中的最大 ADC 频率,该频率低于 SYSCLK。

配置设备时钟设置的示例:

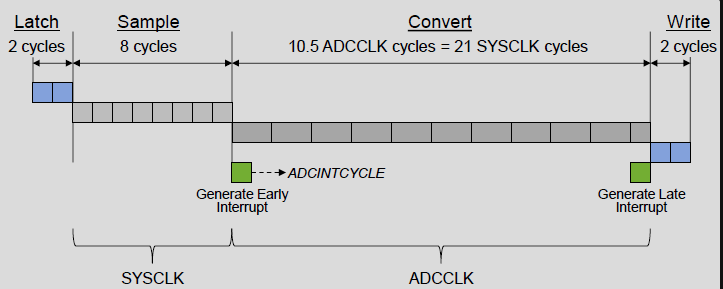

ADC 时序

下面是计算最大采样率的示例。本例中,SYSCLK 为 100MHz(周期 10ns),ADCCLK 为 50MHz(周期 20ns)。

采样 + 保持(采样窗口)时间:8 * 10 ns = 80 ns

转换时间:21 * 10 ns = 210 ns

**采样率:**80 ns + 210 ns = 290 ns ->3.45 MSPS(兆次采样/秒)

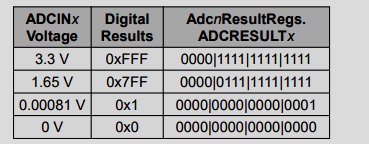

ADC转换结果寄存器

ADC 转换结果存储在 ADCRESULTx 寄存器中。ADC_readResult() 函数可用于根据 ADC 模块和 SOC 编号读取结果。

下面是12位ADC结果对应:

可选 2.5 V 或 3.3 V 内部基准电压源(多核设备不可用),比例式外部基准电压源由 VREFHI/VREFLO 设置

ADC校准和参考

内置校准

TI 保留的 OTP 包含 ADC、内部振荡器和缓冲 DAC 的设备特定校准数据: 引导 ROM 包含一个 Device_cal() 例程,用于将校准数据复制到相应的寄存器。必须运行 Device_cal() 才能满足数据手册中的规范。引导加载程序会自动调用 Device_cal(),因此用户通常无需执行任何操作。如果绕过引导加载程序(例如在开发过程中),则应用程序应调用 Device_cal()。

Device_cal() 函数由 sysctl.h 文件中的 SysCtl_deviceCal() 函数调用,而后者又由 Device_init() 函数调用。Device_init() 函数位于 device.c 文件中。C2000Ware 示例程序正是利用该函数来初始化设备。

手动 ADC 校准

如果数据表中的偏移和增益误差对于你的应用来说是不可接受的,或者还想补偿板级误差(例如传感器或放大器偏移),可以手动校准:

偏移误差(12位模式): 使用 ADCOFFTRIM 寄存器进行模拟补偿,满量程范围不减小,将输入配置为 VREFLO,将 ADCOFFTRIM 设置为最大失调误差,并进行读数,重新调整 ADCOFFTRIM 使结果为零。

增益误差: 软件补偿,满量程范围内有所损失,需要使用第二个 ADC 输入引脚,并在该引脚上设置上限参考电压。

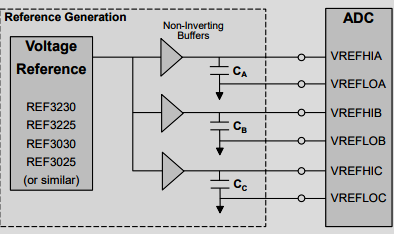

模拟子系统外部参考

下图显示了 F28004x 设备的参考生成方案示例:

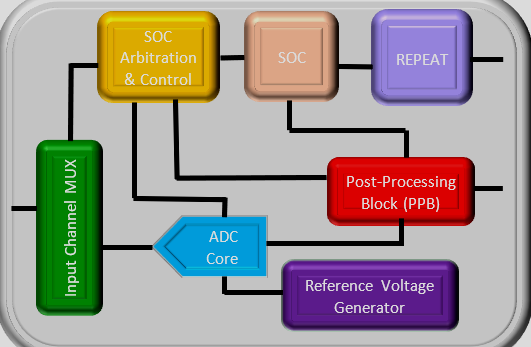

ADC 类型 4

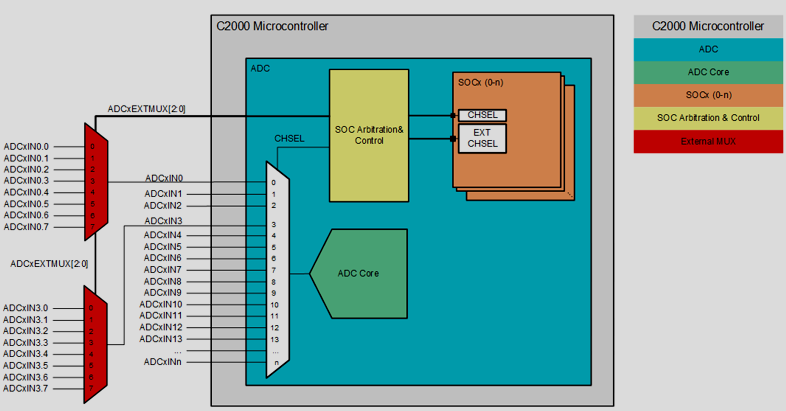

下图为ADC模块的简化图,由输入通道MUX、SOC仲裁、SOC模块、REPEAT模块、后处理模块(PBB)、ADC核心、参考电压发生器组成。

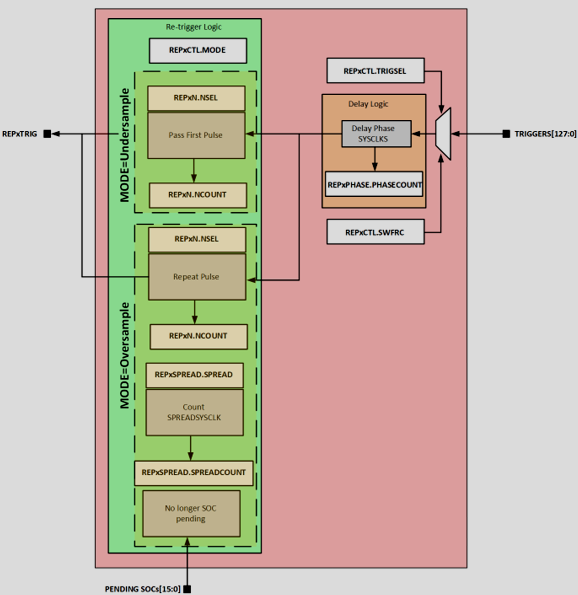

ADC Type-4 模块包含两个重复模块,其中的触发器可从任何常规触发器中选择。选择后,中继器可以根据模块中的其他配置将修改后的输入触发器传递到其输出。从 SOC 的角度来看,中继器触发器的功能与任何其他触发器相同。REPEAT 模块如下所示:

可能的触发器修改有过采样,欠采样等。

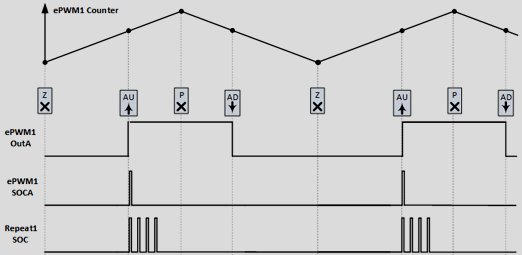

过采样

初始触发信号会传递至模块输出。一旦所有配置为接收触发信号的 SOC 不再处于待处理状态(最后一个采样正在进行中),就会再次发出触发信号。此过程重复进行,直到发出固定且预选数量的触发脉冲(NSEL + 1 个脉冲)。这使得应用程序可以轻松地从单个触发脉冲执行多个连续采样。与 PPB 中的聚合选项结合使用时,可以实现过采样、平均或峰值检测。

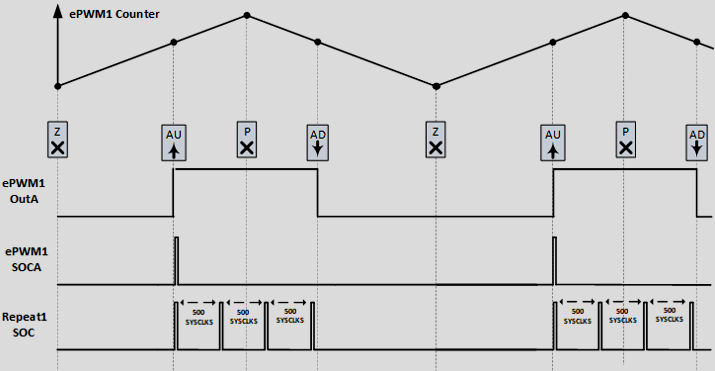

下图显示了过采样 ADC 触发方案的示例。(TRIGGER = ePWM SOCA、NSEL = 3、PHASE = 0、MODE = 过采样、SPREAD = 0):

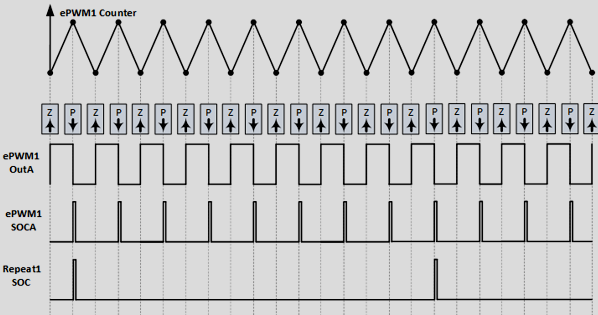

欠采样

初始触发信号会传递至模块输出。后续触发信号会被阻止,直到重复模块接收到固定且预选数量的触发脉冲(NSEL + 1 个总触发信号)。最终结果是,只有 1/N 的触发脉冲会传递至输出。这允许应用降低一个或多个 SOC 的触发频率。这对于电荷共享输入驱动器非常有用,因为这类驱动器的误差会随着通道采样频率而增加。

下图显示了欠采样 ADC 触发方案的示例。(TRIGGER = ePWM PRD、NSEL = 7、PHASE = 0、MODE = 欠采样、SPREAD =(无关))。

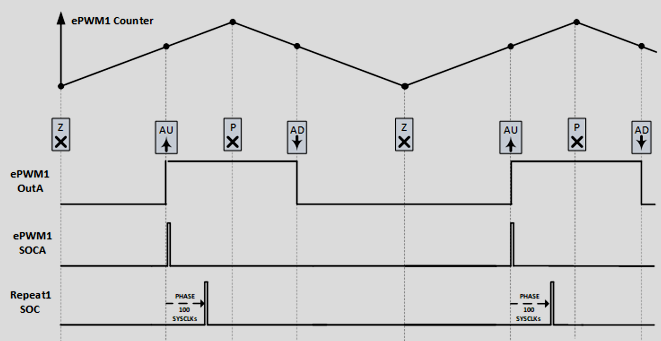

相位延迟

初始触发延迟指定数量的 SYSCLK 周期。这可以与过采样或欠采样触发器结合使用。这使得应用程序可以将触发起始点与 ePWM 中的事件(例如 CMPAU)绑定,而无需触发恰好在事件时间发生。例如,如果事件导致引脚状态发生变化,并且应用程序希望在引脚边沿噪声稳定后稍晚进行采样,则此功能非常有用。如果没有相位延迟,则需要进行额外的比较。

下图显示了具有相位延迟的 ADC 触发器的示例。(TRIGGER = ePWM SOCA,NSEL = 0,PHASE = 100,MODE =(任意),SPREAD =(无关))。

重新触发传播

如果希望采样间有额外的时间,则可以将 SPREAD 设置为等于采样间所需时间的 SYSCLK 周期数。

下图显示了使用样本扩展的 ADC 触发器的示例。(TRIGGER = ePWM SOCA,NSEL = 3,MODE = 过采样,PHASE = 0,SPREAD = 500)。

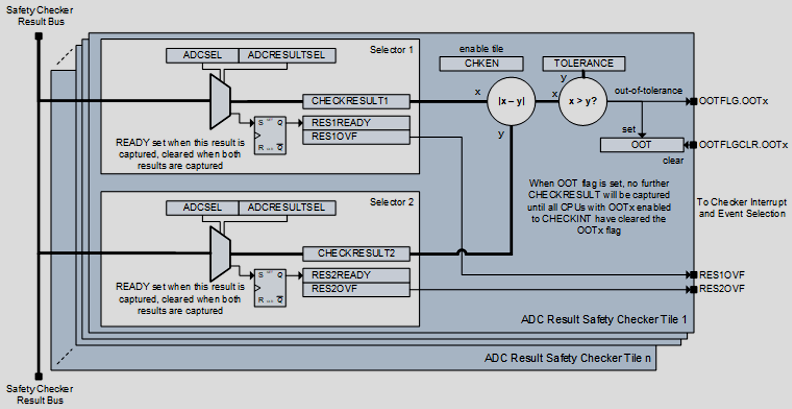

安全检查器

在 ADC 模块中,为了便于对冗余 ADC 结果进行自动硬件安全检查,安全检查器子系统会侦听来自多个 ADC 模块的各种 ADC 结果,比较这些结果,然后检查结果是否在范围内。如果汇总结果超出范围,则会通过 X-BAR 和/或 ISR 触发硬件跳闸。从高层次上讲,ADC 安全检查器由一系列共用 ADC 结果总线的检查块组成。当 ADC 产生结果时,结果会被放置在检查总线上,以便每个检查块都能捕获其相关结果。一旦检查块捕获到两个已配置的 ADC 结果,就会取结果之间差异的绝对值,并将其与预设的容差进行比较。如果差异超出容差,则会为 X-BAR 生成事件或生成中断。

MUX连接

为了控制外部多路复用器,分配了四个通道选择引脚,以便处理通过数字输出引脚连接的更多通道。这使得客户能够灵活地通过外部多路复用器增加每个 SOC 中的 ADC 通道数,同时最大限度地降低软件开销。与其他外设一样,通道选择引脚可以通过映射到 GPIO 多路复用器位置来使用。

在 ADC Type-4 模块上,通过向后处理模块 (PPB) 添加额外的硬件来实现过采样。该硬件支持累加求平均值,以及对一系列样本进行最小/最大值运算,以进行峰值检测和异常值移除。

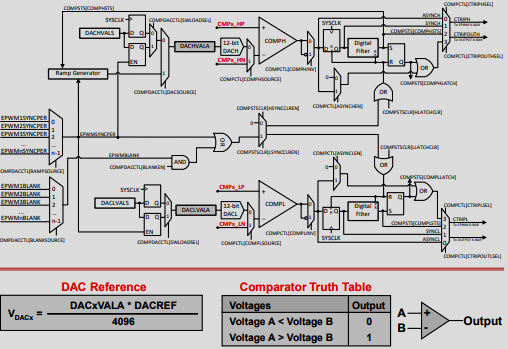

比较器子系统(CMPSS)

比较器子系统 (CMPSS)模块可用于支持峰值电流模式控制、开关电源、功率因数校正和电压跳闸监控等应用。每个 模块都有两个比较器–一个高比较器(COMPH)和一个低比较器(COMPL)。“高 ”和 “低 ”在这里只是指 CMPSS 模块中的位置。

每个 CMPSS 模块都是围绕一对模拟比较器设计的,如果正输入端电压大于负输入端电压,比较器就会产生数字输出。

下图是 F28004x 设备的示意图:

比较器的正输入始终由外部引脚驱动。负输入可由外部引脚或内部可编程 12 位数模转换器 (DAC) 作为基准电压驱动。写入 DAC 的值可立即生效,或与 ePWM 事件同步。可选择使用斜坡发生器来控制模块中一个比较器的内部 DAC 参考值。每个比较器的输出都通过一个可编程数字滤波器馈入,该滤波器可消除杂散跳闸信号。

数模转换器 (DAC)

缓冲式 12 位 DAC 模块可将数字信号转换为模拟电压。它还可用于提供可编程的基准输出电压,并包括一个可驱动外部负载的模拟输出缓冲器。

DAC 特性:

- 12 位 DAC 提供可编程的基准输出电压

- 模拟输出缓冲器能够驱动外部负载

- 可选择的基准电压

- 可用作通用 DAC,生成直流电压和交流波形(如正弦波、方波、三角波等)

- 能够与 EPWMSYNCPER 事件同步

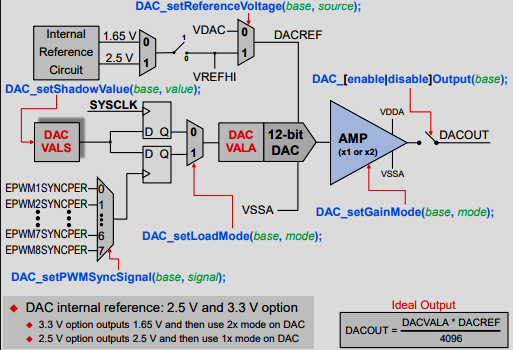

缓冲 DAC 框图

下图显示的是 2 型 DAC。类型 1 的 DAC 不包括内部参考部分(增益选项),输出端有一个下拉电阻。

缓冲 DAC 模块中有两组 DACVAL 寄存器: DACVALA 和 DACVALS:

DACVALA- 只读寄存器,用于主动控制 DAC 值。

DACVALS- 可写影子寄存器,可立即或与下一次 PWMSYNC 事件同步载入 DACVALA。内部 DAC 的理想输出可按上式计算。

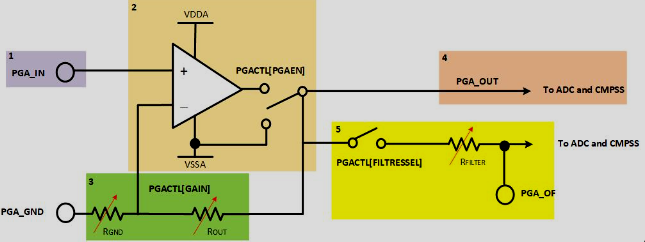

可编程增益放大器 (PGA)

可编程增益放大器 (PGA) 是一个集成模块,用于放大小输入信号,以增加下游 ADC 和 CMPSS 模块的动态范围。放大是通过可编程增益放大器完成的。并非所有 C2000 设备都有 PGA。有关设备支持的模块列表,请参阅外设参考指南。

PGA 模块通常用于放大来自温度传感器、压力传感器和应变仪等模拟传感器的信号。放大后的信号再由模数转换器 (ADC) 模块进行数字化处理。

比如PGA 类型 1:

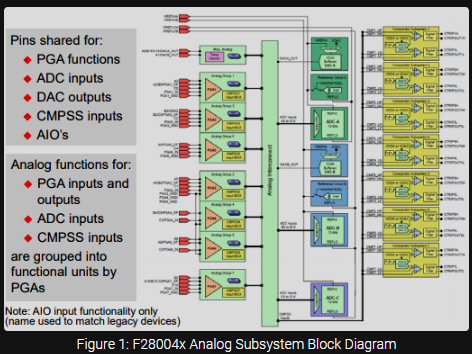

模拟系统互连

模拟子系统互连允许单个引脚将信号传输到多个模拟模块。因此,可以非常灵活地使用引脚,实现更小的器件封装F28x7x 和 F2838x 设备没有模拟子系统互连。

示例: F28004x 模拟子系统互连器件:

DAC 输出、比较器子系统输入、PGA 功能和数字输入与 ADC 输入复用:

821

821

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?