深入浅出地了解STM32中的时钟树

1 本文的目标

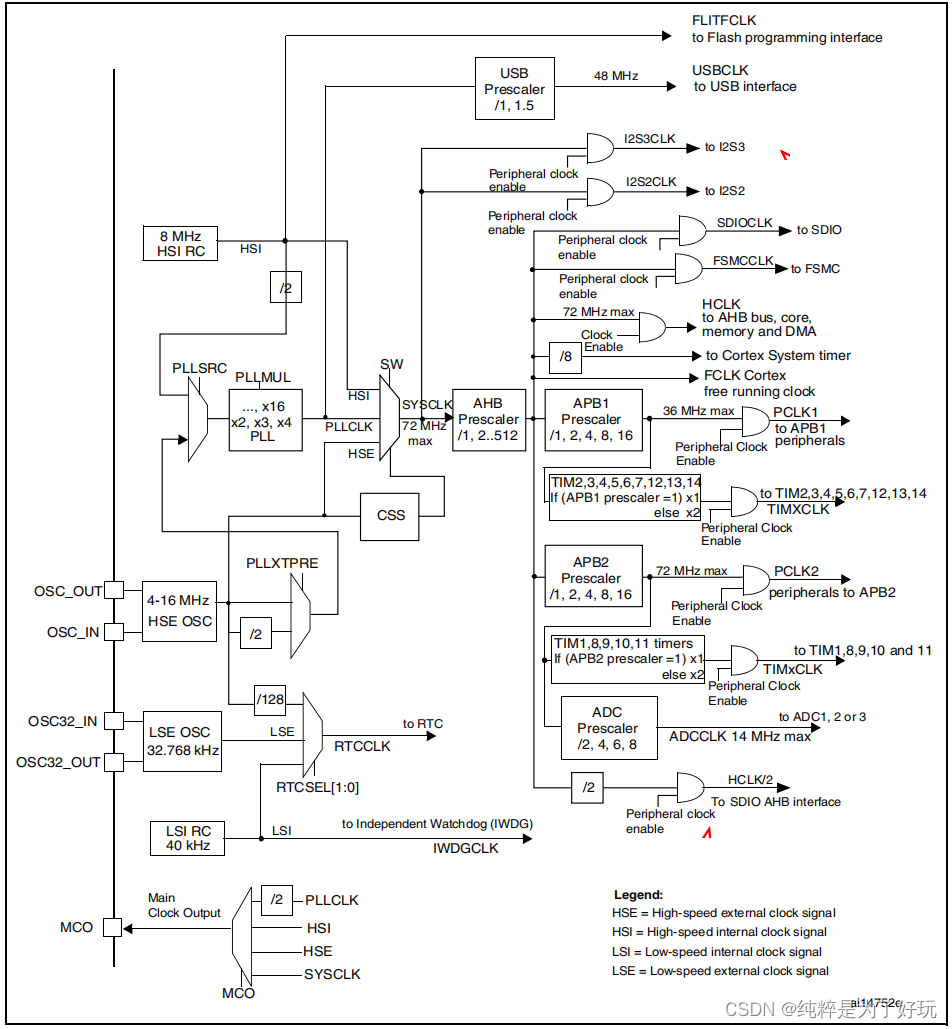

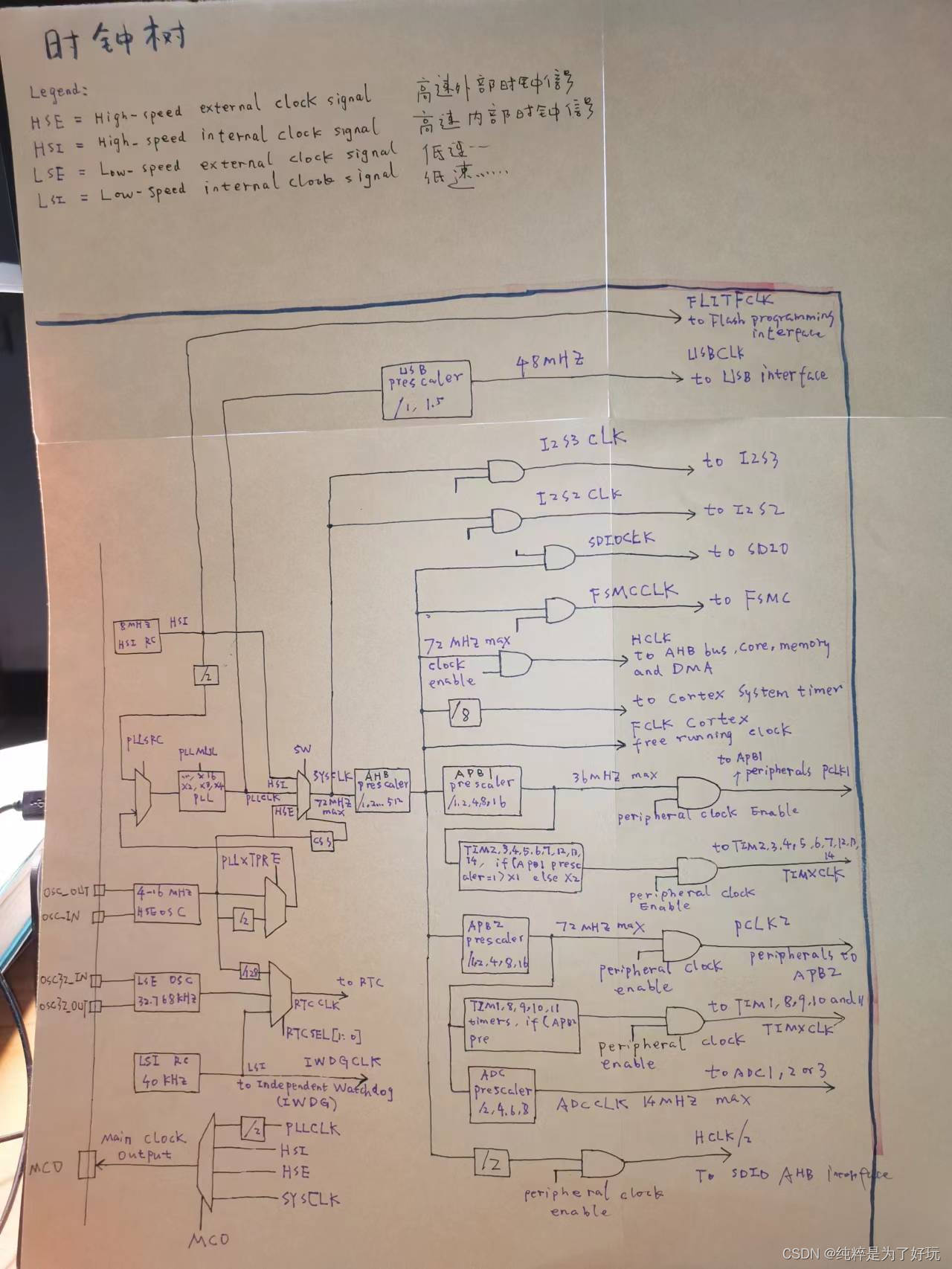

弄明白下面这个图,也就是时钟树

2 到底什么是时钟信号?

可以这么说:

In electronics and especially synchronous digital circuits, a clock signal is a particular type of signal that oscillates between a high and a low state and is utilized like a metronome to coordinate actions of circuits.

时钟信号是一种特殊类型的信号,它在高低状态之间振荡,并像节拍器一样被用来协调电路的动作。

3 时钟信号是怎么产生的?

之前写的这篇文章,略有设计:在 keil 建立基于STM32开发的工程模板–详细步骤

4 时钟信号有几类

STM32Fl03 相关时钟 可以分为以下 3 种:

(1) 输入时钟

(2) 系统时钟

(3) 其他时钟:由系统时钟分频得到

4.1 输入时钟

STM32Fl03 的 输入时钟可以来自不同的时钟源。

从频率和源角度来分,分类如下:

高速时钟为 STM32Fl03 的主时钟提供时钟信号,

低速时钟仅为实时时钟 (Real Time Clock, RTC) 和独立看门狗(Independent Watch Dog, IWDG)提供时钟信号。

从芯片角度来分,可以分为内部时钟(片内时钟)和外部时钟源(片外时钟)。内部时钟由芯片内部 RC振荡器产生,起振较快,因此系统主时钟在芯片刚上电时默认采用内部高速时钟。而外部时钟通常由外部晶振输入,在精度和稳定性上都具有很大的优势。

因此,通常上电之后通过软件配置将主时钟转而采用外部高速时钟信号。

(1)高速外部时钟

高速外部时钟 (High Speed External clock signal, HSE)通常以外部晶振作为时钟源,晶振频 率可取范围为 4 ~ 16MHz, ST 官方推荐选取 8MHz 外接晶振作为

STM32Fl03 微控制器的 HSE。

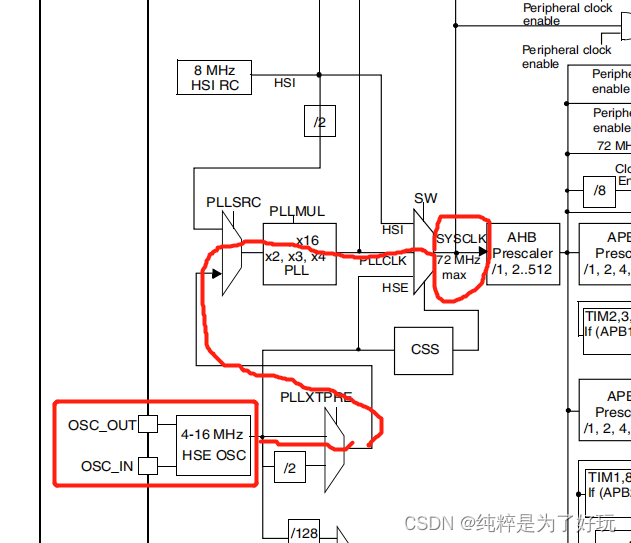

下面即以外接8MHz晶振作为高速外部时钟为例,沿着下图的STM32F103时钟树,介绍STM32F103的时钟系统是如何从高速外部时钟(8MHz晶振)开始一步步得到系统时钟SYSCLK。

OSC_IN 和 OSC_0UT : 从最左端的 osc_IN 和 OSC_ OUT 开 始,

STM32Fl03 的这两个引脚分别连接到 8MHz 外部晶振的两端。

PLLXTPRE: 8M 的 HSE 遇到多路选择器 PLLXTPRE(HSE divider for PLL entry)。 通过编程配置寄存器,可以选择 PLLXTPRE的输出 : 对输入时钟的二分频或不分频。 通常选择不分频,因此,经过 PLLXTPRE 后,输出仍然是 8MHz 的时钟信号。

PLLSRC: 8MHz的HSE遇到多路选择器PLLSRC (PLL entry clock source)。 同

样可以通过配置寄存器,选择PLLSRC 的输出是高速外部时钟HSE或高速内部时钟

HSI。 通常,选择输出为高速外部时钟HSE。

PLL: 8MHz的HSE遇到锁相环CPLL ),经过PLL 后,输出时钟称为PLLCLK。 通

过配置PLL 寄存器,选择倍频系数 PLLMUL (PLL mul tipli cation factor),可以决定

PLLCLK输出频率。 通常,为了使STM32Fl03满频工作,通常将倍频系数设为9。 于是,经过PLL后,原来8MHz的时钟HSE变成了72MHz的时钟PLLCLK。

SW: 72MHz的PLLCLK遇到多路选择器SW。 通过配置寄存器,可以选择SW输

出为PLLCLK、HSE或HSI。 SW输出就是STM32Fl03的系统时钟SYSCLK,通常选

择PLLCLK作为SW输出。 因此,STM32Fl03的系统时钟SYSCLK 为72MHz。

(2) 高速内部时钟

高速内部时钟(High Speed Internal clock signal, HSI)由片内RC振荡器产生,频率

为8MHz,但不稳定。 STM32Fl03从上电开始即采用HSI作为初始的系统时钟。

(3)低速外部时钟

低速外部时钟(Low Speed External clock signal , LSE)通常以外部晶振作为时钟源,

主要提供给实时时钟模块,所以一般采用32. 768 kHz。

(4) 低速内部时钟

低速内部时钟(Low Speed Internal clock signal, LSI)由片内RC振荡器产生,可以

提供给实时时钟模块和看门狗模块,频率为40 kHz。

4.2 系统时钟

从上可知,系统时钟SYSCLK 由多路选择器SW根据用户设置选择PLLCLK、HSE或HSI中的一路输出而得。 SYSCLK的最高频率可达72MHz(通常也工作在72MHz), 是STM32Fl03大部分 部件的时钟来源。

通常,STM32Fl03从上电开始 ,选用HSI作为初始的系统时钟。 在完成初始化后,一般选用更加稳定可靠的HSE作为系统时钟的来源。为了让用户能够实时检测时钟系统是否运行正常,ST 在STM32Fl03 系列微控制器上专门提供了引脚MCO(M ai nC lock Output,主时钟输出)。 用户可以通过软件编程,选择SYSCLK、PLLCLK、HSE或HSI中的一路在MCO上输出。

4.3 其他时钟

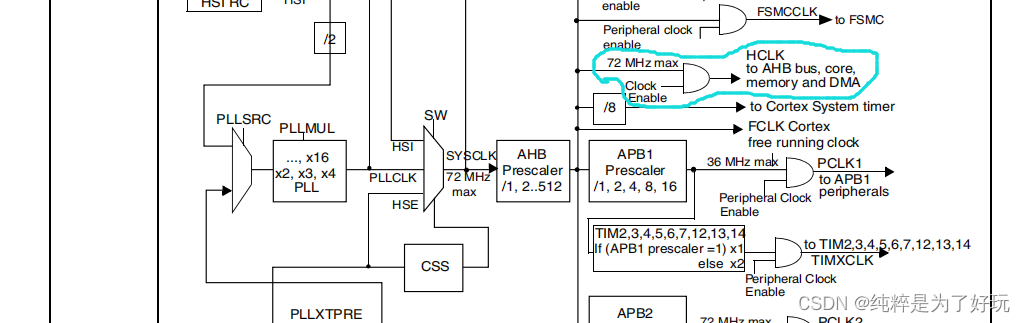

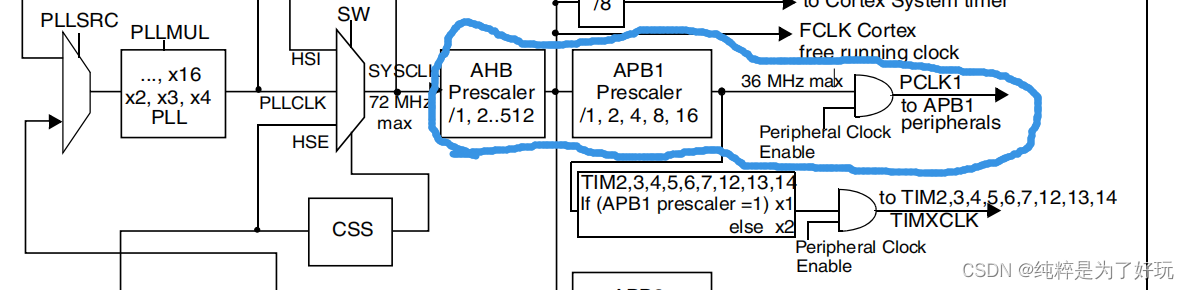

系统时钟SYSCLK 经过AHB预分频器输出到STM32Fl03的各个部件:

(1)HCLK: 高速总线AHB的时钟,由系统时钟SYSCLK 经AHB预分频器后直接得到。 通常, 将AHB预分频系数设置为1,HCLK即 为72MHz,最高 也为72MHz。 HCLK为Cortex-M3内核存储器和DMA提供时钟信号。 它 是Cortex-M3内核的运行时钟。 由此可见, CPU主频就是这个时钟信号。 通常情况下 CPU运行于 高 , STM32Fl03的频率72MHz。

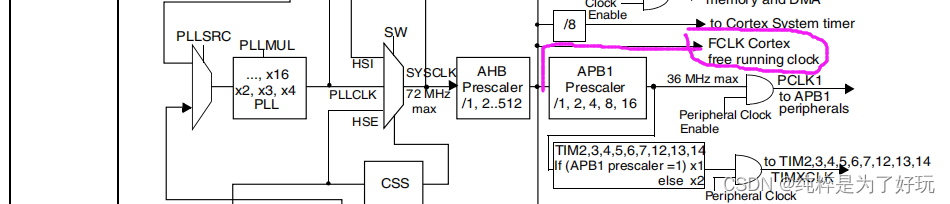

(2)FCLK: Cortex-M3内核的 “自由运行” 时钟,同样由系统时钟SYSCLK经AHB预分频器后直接得到。 它与HCLK互相同步,最大 也 是72MHz。 所谓的不来自 HCLK 。 因 此在HCLK停止时FCLK仍能继续运行。 这样 ,可以保证即使在Cortex-M3内核睡眠时也能采样到中断和跟踪休眠事件。

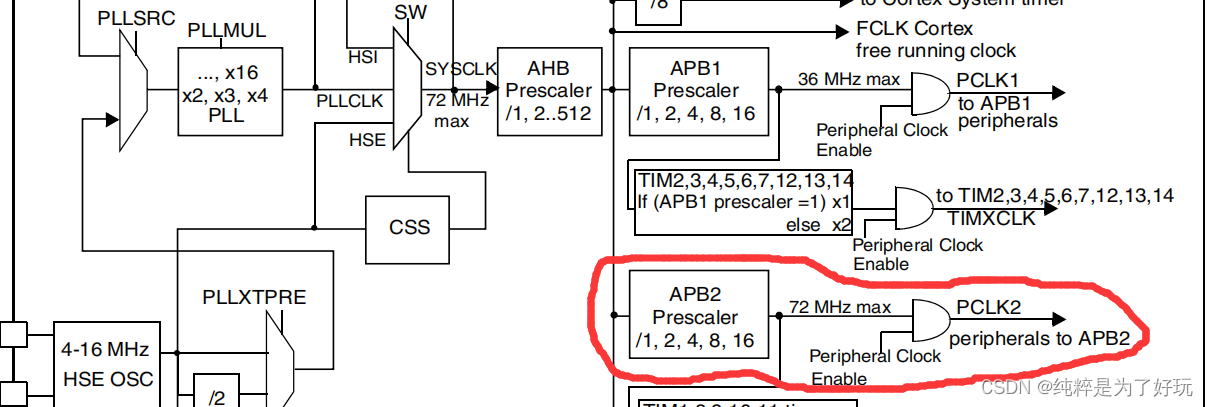

(3)PCLK1: 外设时钟,由系统时钟SYSCLK经AHB预分频器,再经APBl预分频器后得到。 通常情况下,将AHB的预分频系数设置为1,将APB1 的预分频系数设置为2, PCLK1 即为36MHz,它的最大频率也为36MH 。 PCLK1为挂载在APB1 总线上的外设提供时钟信号,如USART2、USART3、UART4、UART5、SPI2/I2S、SPI3/I2S、I2C1、I2C2、USB、RTC、CAN、DAC、PWR、BKP、IWDG、WWDG等。类似地,如需使用以上挂载在APB2总线上的外设,必须先开启APB2总线上该外设的时钟。

(4)PCLK2: 外设时钟,由系统时钟SYSCLK经AHB预分频器,再经APB2预分频器后得到。 通常情况下 ,将AHB预分频系数和APB2的预分频系数都设置为1,PCLK2即为72MHz,它的最大频率也为72MH 。PCLK2为挂载在APB2总线上的外设提供时钟信号,如GPIOA、GPIOB、GPIOC、GPIOD、GPIOE、GPIOF、GPIOG、USART1、SPI1、EXTI、AFIO等。 尤其需要注意的 是,如需使用以上 挂载在APB2总线上的外设 ,必须先开启APB2总线上该外设的时钟。

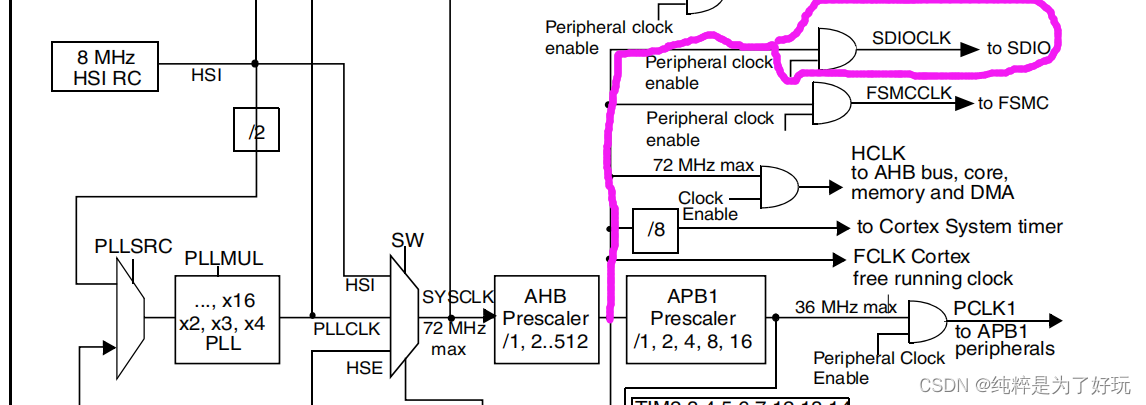

(5)SDIOCLK: SDIO外设的时钟,由系统时钟SYSCLK经AHB预分频器后直接得

SDI 到。 类似地,如需使用SDIO外设,必须先开启SDIOCLK 。

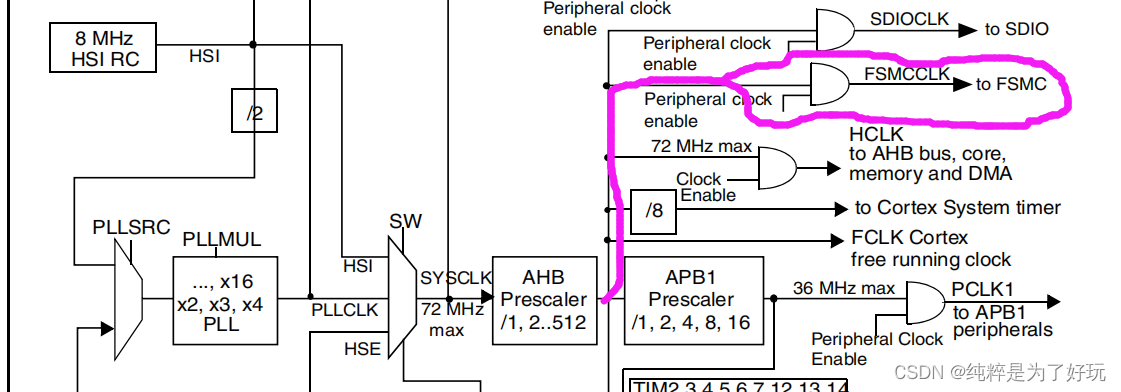

(6)FSMCCLK: 可变静态存储控制器的时钟,由系统时钟SYSCLK经AHB预分频器

后直接得到。类似地 ,如需使用 FSMC外接存储器,必须先开启FSMCCLK 。

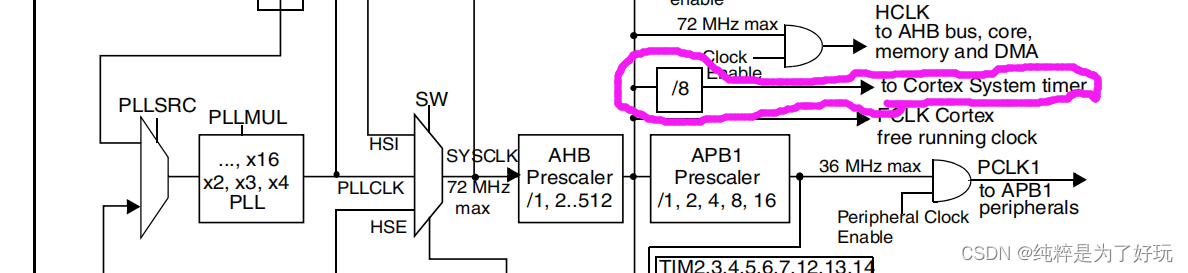

(7)STCLK: 系统定时器 SYSTICK的外部时钟源,由系统时钟SYSCLK 经 AHB 预分频器,再经过 8分频后得到, 等千HCLK/8。除了外部时钟源 STCLK , 系 统定时器SYSTICK还可以将FCLK作为内部时钟源 。

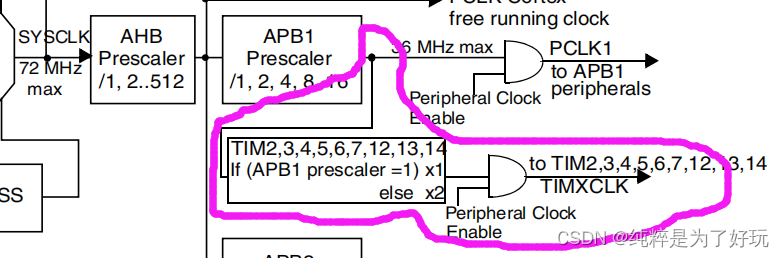

(8)TIMXCLK: 定时器 2到定时器 7的内部时钟源,由APBl总线上的时钟PCLK1 经

过倍频后得到。 类似地,如需使用定时器 2到定时器 7 中的任意一个或多个,必须先开

启APB2总线上对应的定时器时钟。

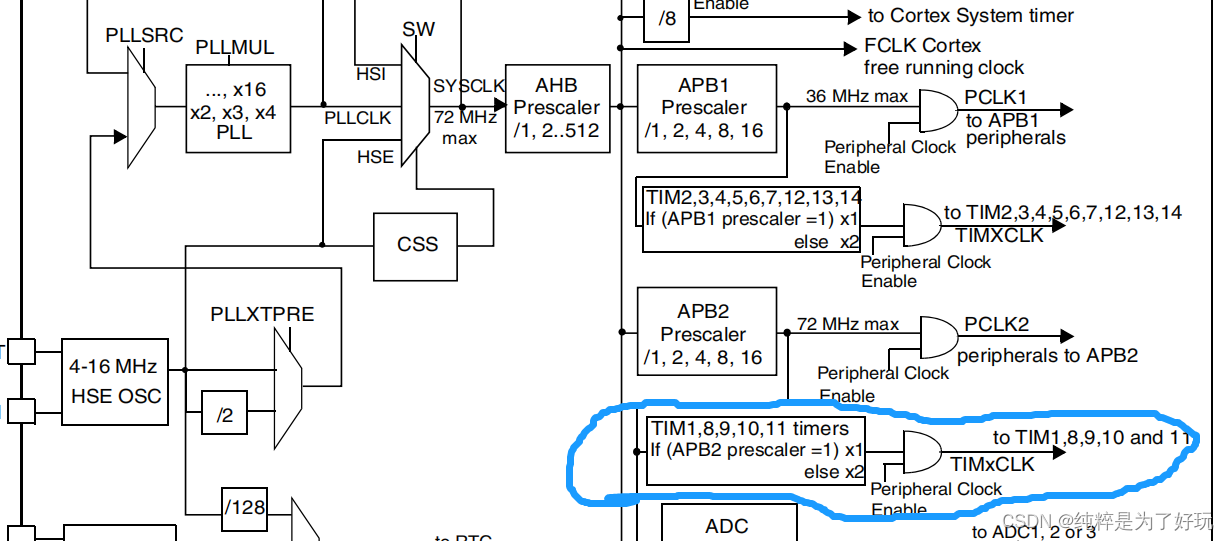

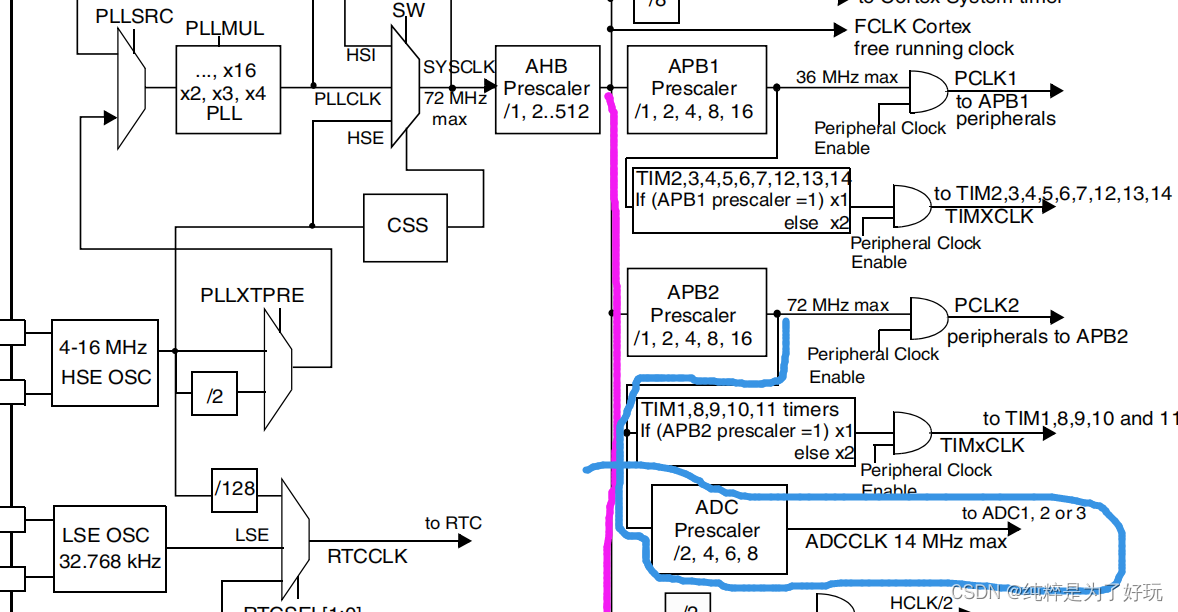

(9)TIMxCLK: 定时器 1和定时器8的内部时钟源,由APB2总线上的时钟PCLK2经

过倍频后得到。 类似地,如需使用定时器1或定时器8 ,必须先开启APBl总线上定时器

1或定时器8的时钟。

(10)ADCCLK : ADC1、ADC2、ADC3的时钟, 由APB2总线上的时钟 PCLK2 经 ADC 预分频器得到。 ADCCLK最大为14MHz。

5 why so complication?

最后,为什么STM32Fl03的时钟系统 会显得如此复杂呢?因为有倍频、分频和一系列外设时钟的开关。 首先,倍频是考虑到电磁兼容性,如果直接外接一个 72MHz的晶振, 过高的振荡频率会给制作电路板带来难度。

其次,分频是因为STM32Fl03各个片上外设的工作频率不尽相同,既有高速外设又有 低速外设, 需要把高速外设和低速外设分开管理。

最后,每个 STM32F103外设都配备了时钟开关。 当使用某个外设时, 一定要打开该外设的时钟;而当不使用某个外设时,可以把这个外设时钟关闭,从而降低STM32的整体功耗。

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?