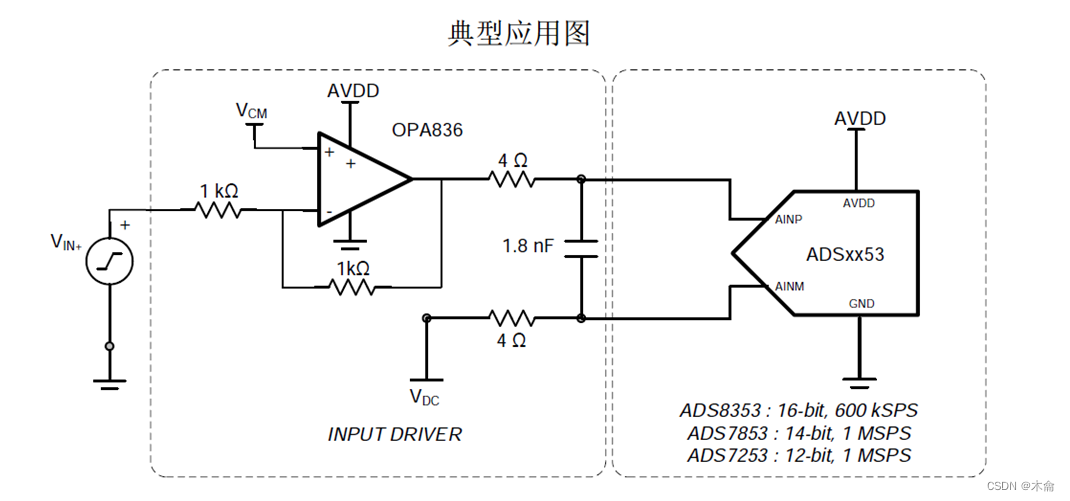

双路高速同步采样模数转换器(适用ADS8353, ADS7853, ADS7253)

- 双通道同步采样

- 支持单端和伪差分输入

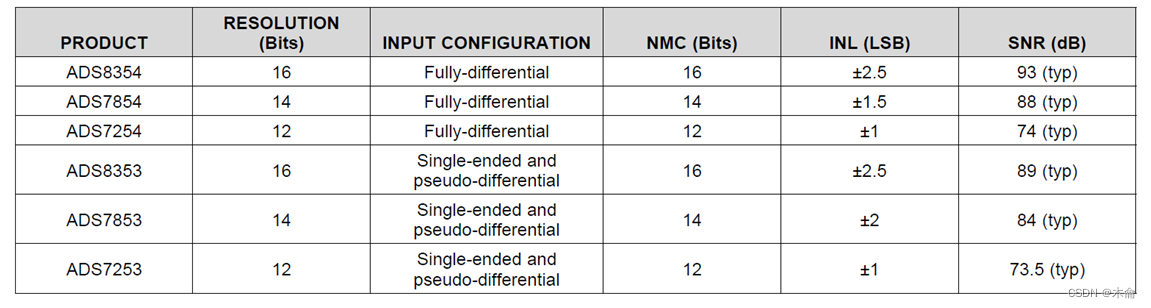

- 高速:16bit,600KSPS

Device Comparison Table

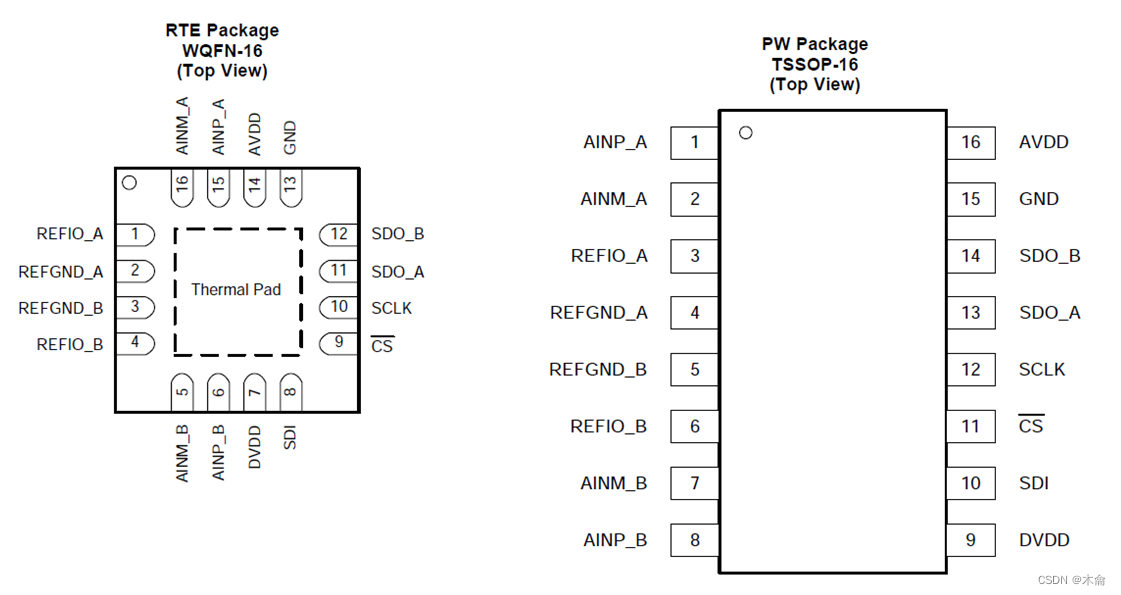

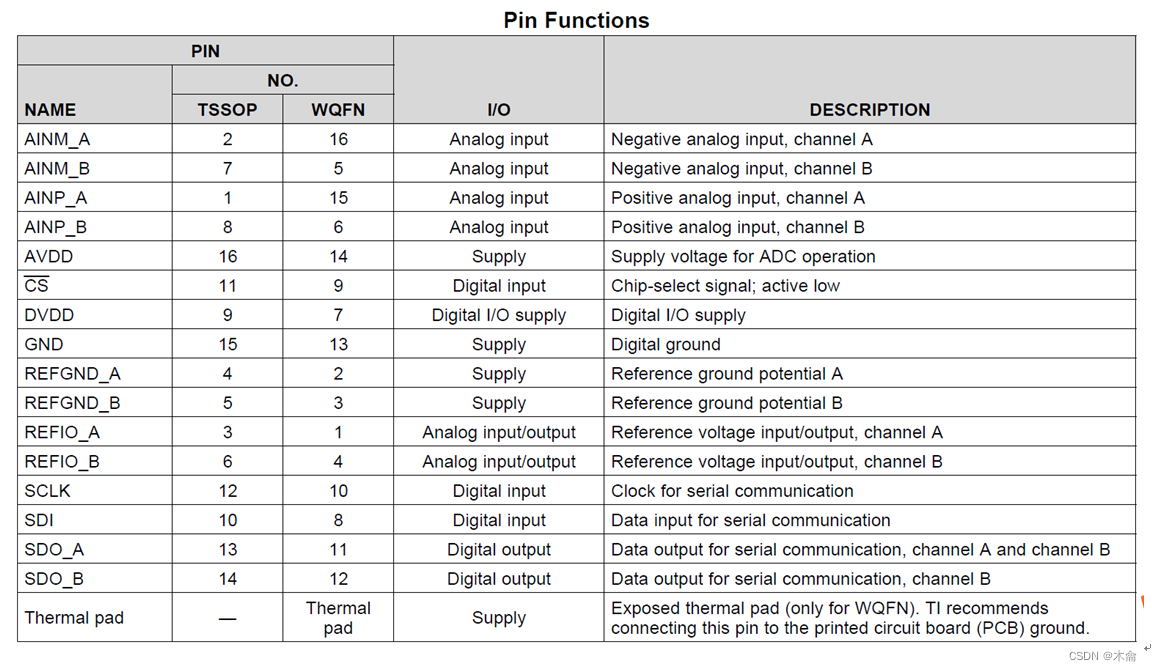

Pin Configurations and Functions

Detailed Description

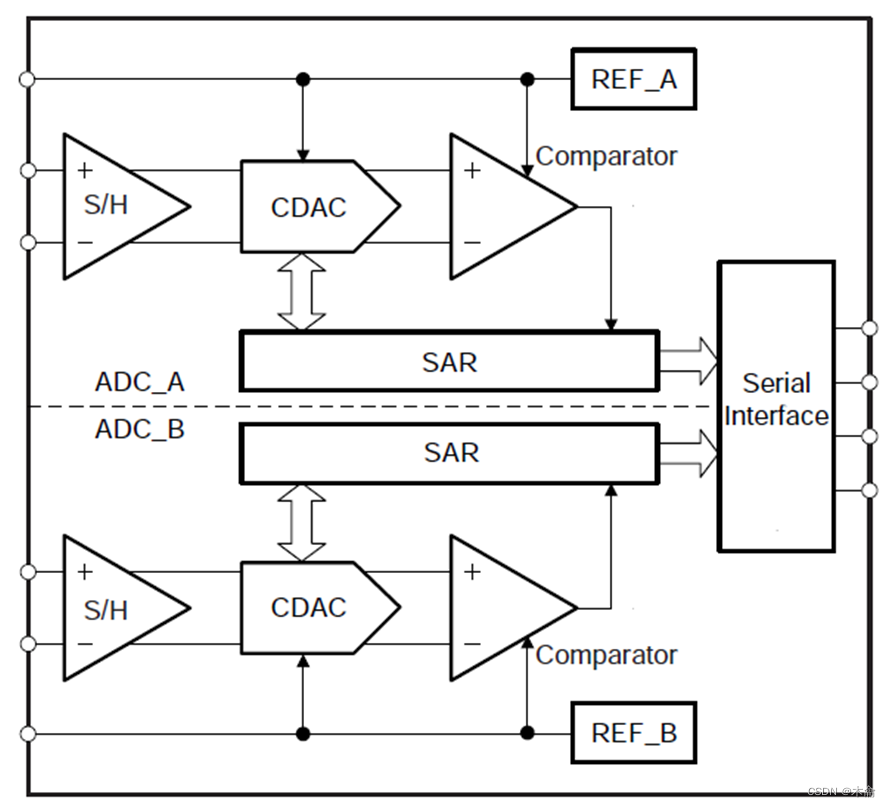

这些器件属于引脚兼容、双高速、同时采样、模数转换器(adc)系列。ADS8353、ADS7853和ADS7253支持单端和伪差分输入信号。该设备为主控制器提供了一个简单的串行接口,并在广泛的模拟和数字电源上运行。这些器件有两个独立的可编程内部参考,以实现系统级增益误差校正。“功能框图”展示了设备的功能框图。

原理框图:

特点描述

Reference

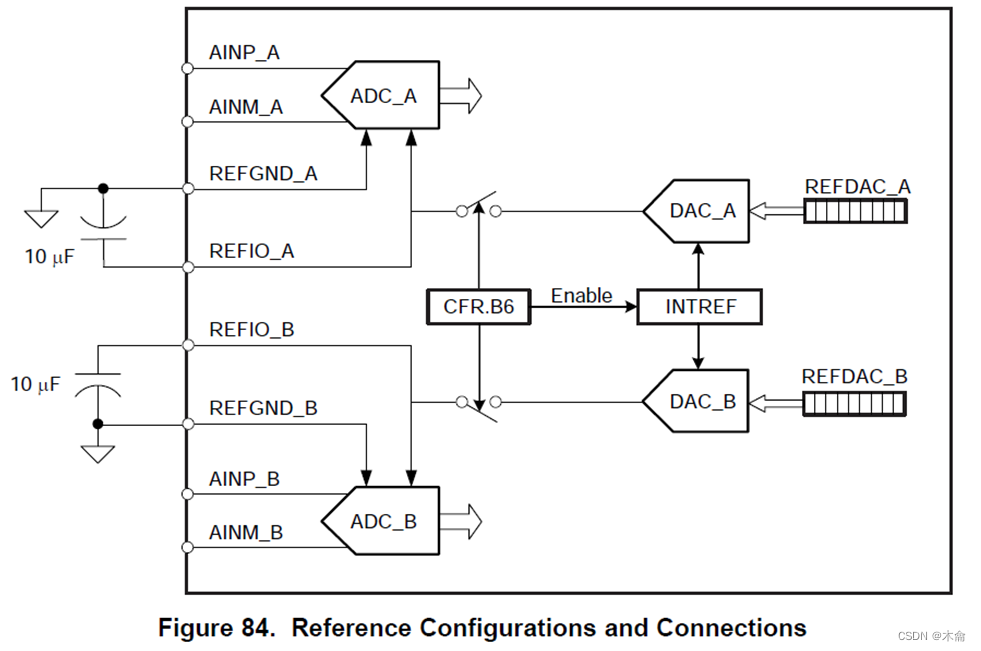

该器件有两个同时采样adc (ADC_A和ADC_B)。ADC_A和ADC_B分别与REFIO_A和REFIO_B引脚上的参考电压VREF_A和VREF_B一起工作。REFIO_A和REFIO_B引脚应分别与REFGND_A和REFGND_B引脚去耦,使用10μf去耦电容。该设备支持使用内部或外部引用源进行操作,如图84所示。参考电压源由配置寄存器(CFR.B6)的第6位设置确定。注意,这个位对于ADC_A和ADC_B是通用的。

当CFR.B6为0时,设备关闭内部参考源(INTREF), ADC_A和ADC_B分别作用于用户在REFIO_A和REFIO_B引脚上提供的外部参考电压。

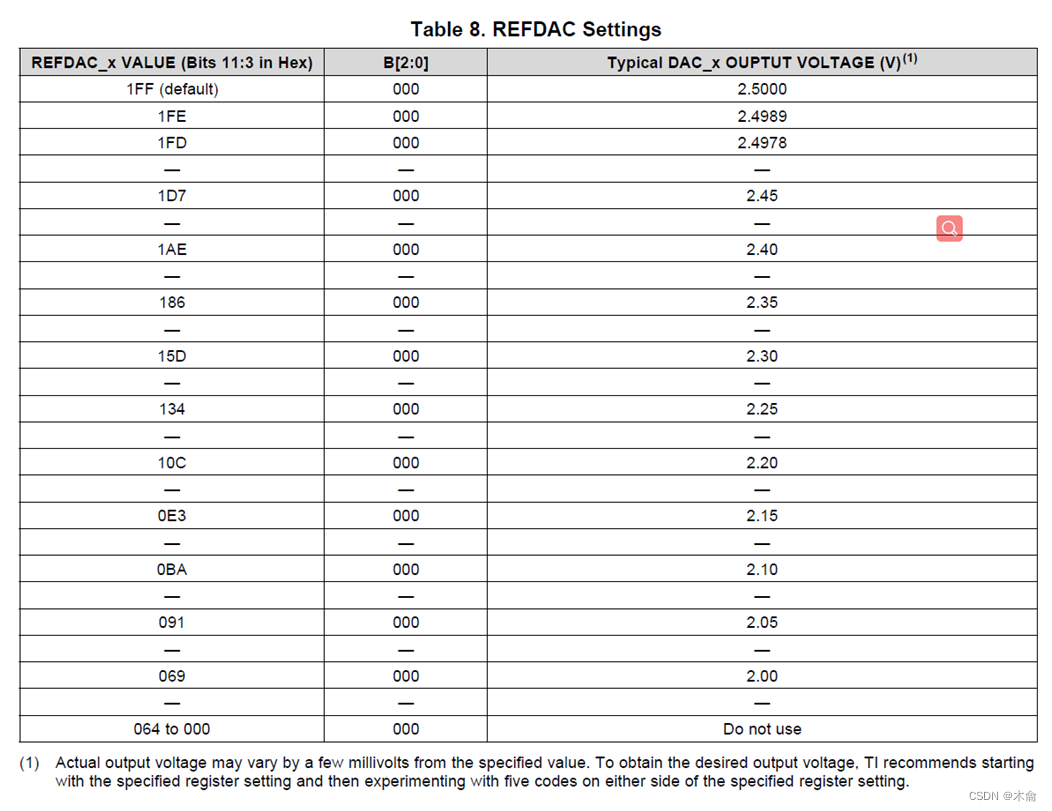

当CFR.B6为1时,设备使用内部参考源(INTREF)运行分别通过DAC_A和DAC_B连接到REFIO_A和REFIO_B。在这个配置中,VREF_A和VREF_B可以通过分别写入各自的用户可编程寄存器REFDAC_A和REFDAC_B来独立更改。有关更多详细信息,请参阅REFDAC寄存器(REFDAC_A和REFDAC_B)部分。

Analog Inputs

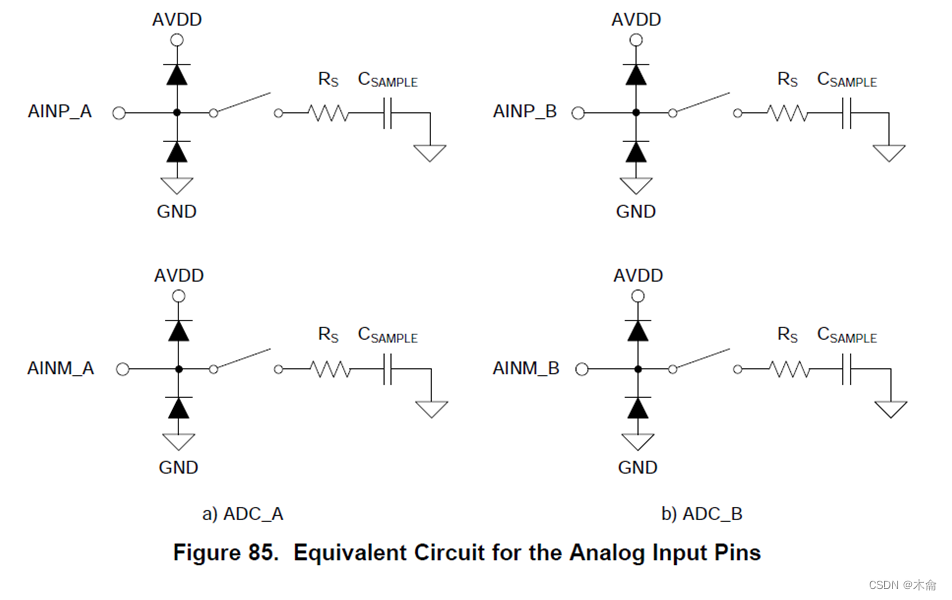

ADS8353、ADS7853和ADS7253在两个ADC通道上支持单端或伪差分模拟输入。这些输入由两个adc ADC_A和ADC_B同时采样和转换。ADC_A采样和转换(VAINP_A - VAINM_A), ADC_B采样和转换(VAINP_B - VAINM_B)。

图85a和图85b分别显示了ADC_A和ADC_B模拟输入引脚的等效电路。串联电阻,RS,代表通路采样开关电阻(通常是50 Ω), CSAMPLE是器件采样电容(通常是40 pF)。

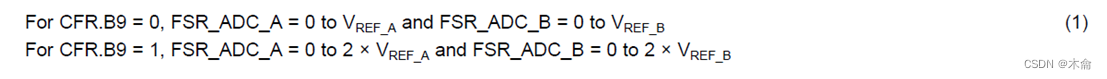

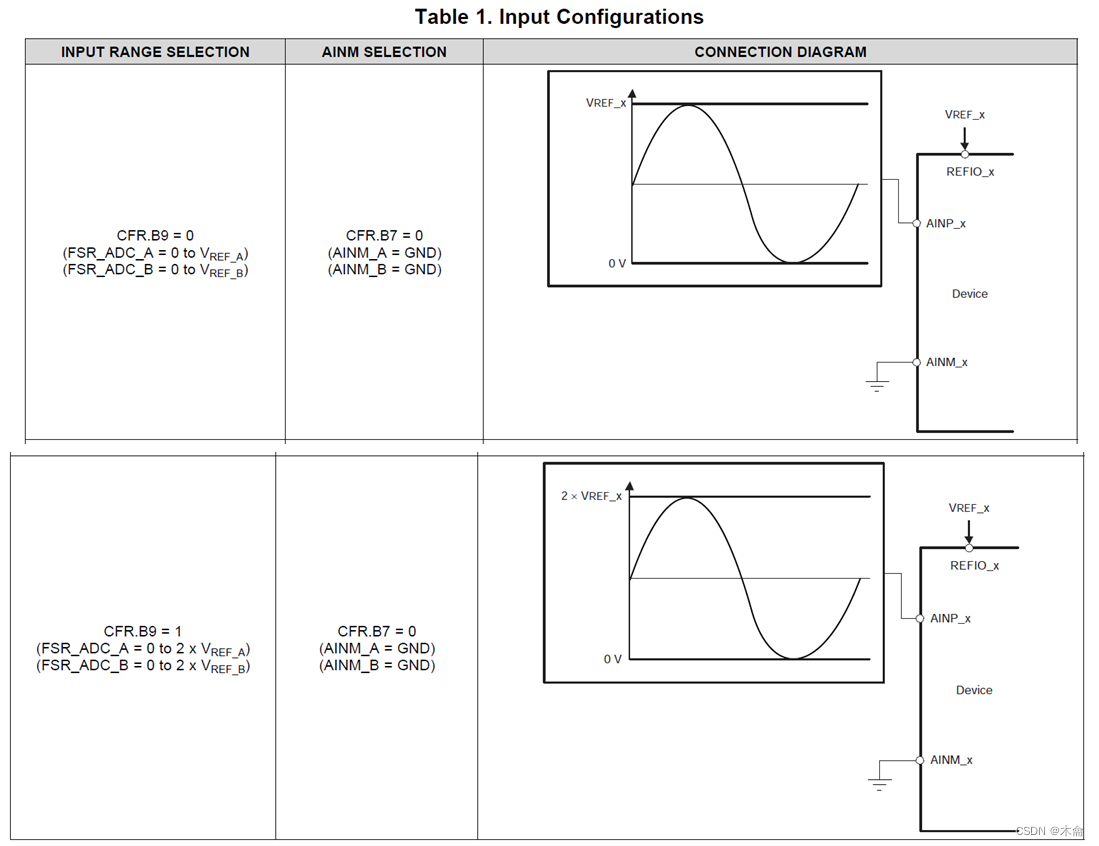

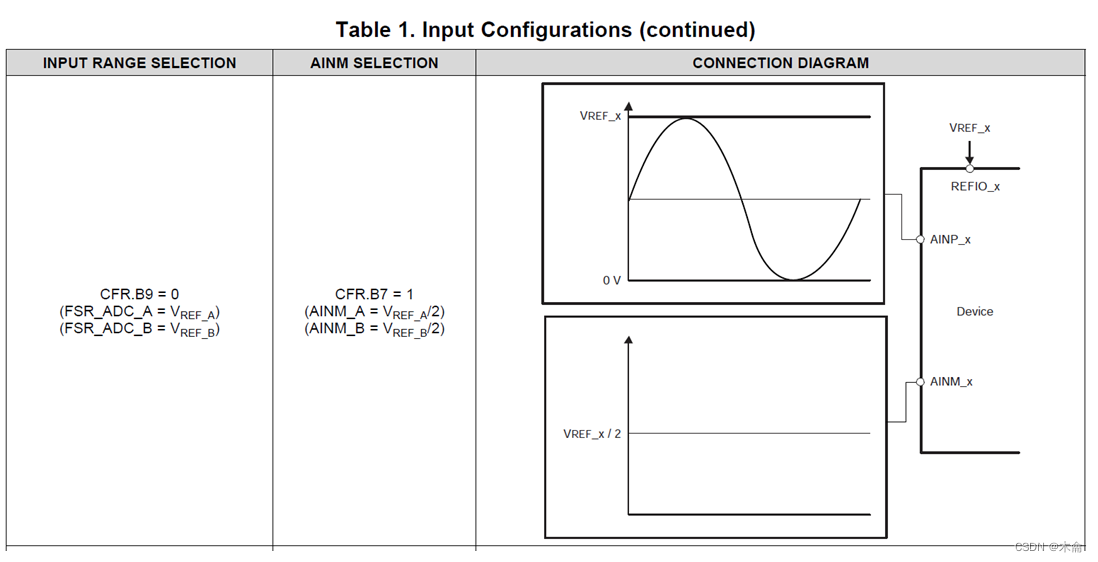

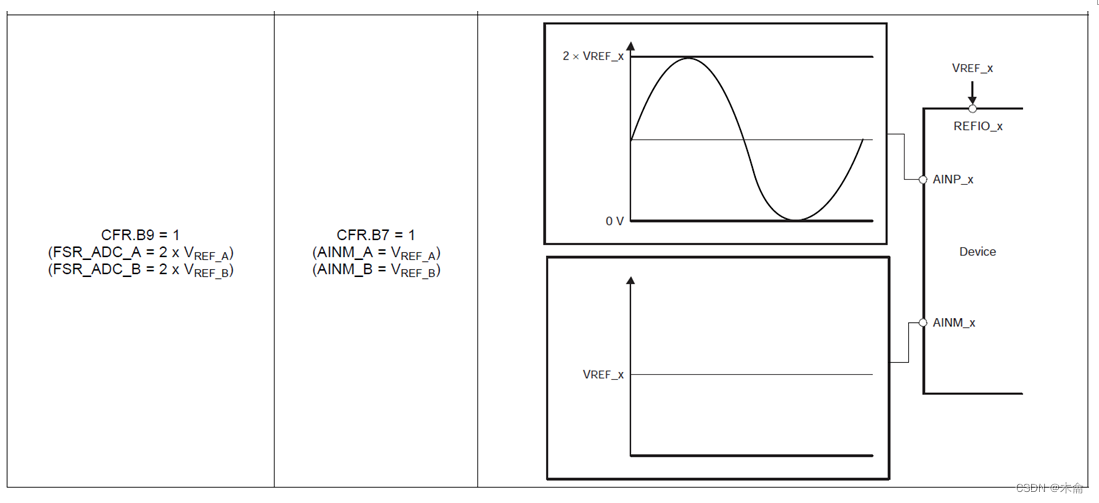

Analog Input: Full-Scale Range Selection

器件模拟输入支持的全量程范围(FSR)可通过配置寄存器(CFR.B9)的位B9进行编程。这个位对于adc (ADC_A和ADC_B)都是通用的。FSR由式(1)、式(2)给出:

VREF_A和VREF_B分别是连到ADC_A和ADC_B的参考电压。

因此,通过适当地设置REFDAC_A和REFDAC_B寄存器,CFR.B7和CFR.B9,可以使用ADC的最大动态范围。

注意,在使用CFR.B9设置为1时,必须小心,以使ADC模拟电源(AVDD)在式(3)、式(4)范围

模拟输入:单端和伪差分配置

ADS8353、ADS7853和ADS7253可以支持单端或伪差分输入配置。

为了支持单端输入,配置寄存器(CFR.B7)中的B7必须设置为0 (CFR. B7 = 0),以及

AINM_A和AINM_B必须外接GND。

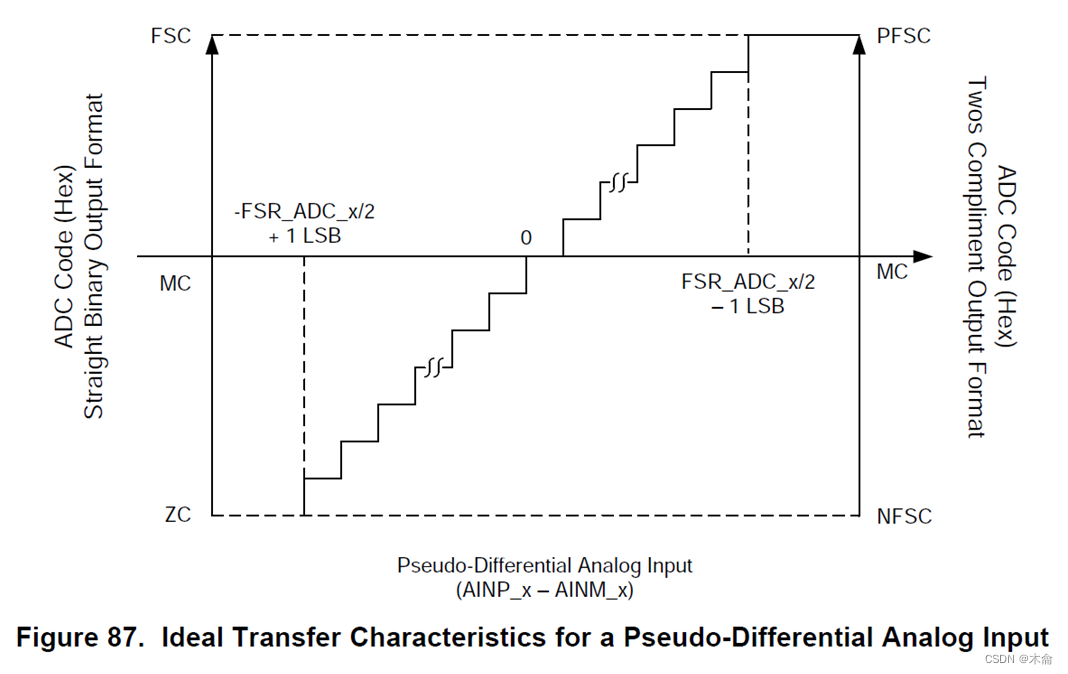

用于支持伪差分输入,CFR.B7必须设置为1 (CFR.B7 = 1), AINM_A和AINM_B必须分别对外连接到FSR_ADC_A / 2和FSR_ADC_B / 2。注意CFR.B7对两个adc都是通用的。

CFR.B9和CFR.B7设置可以组合以选择所需的输入配置,如图表1。

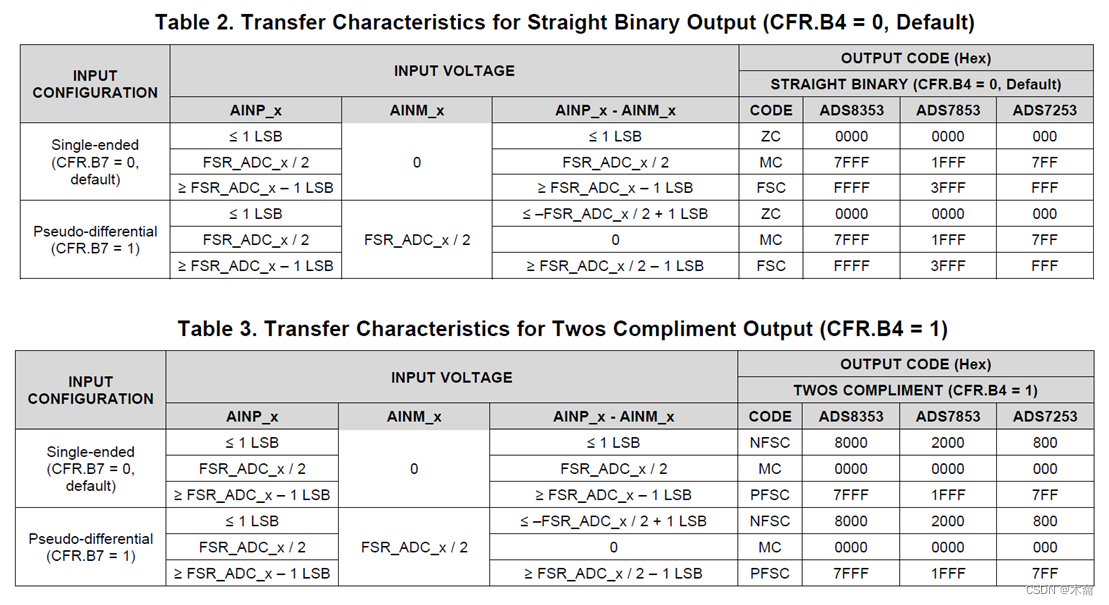

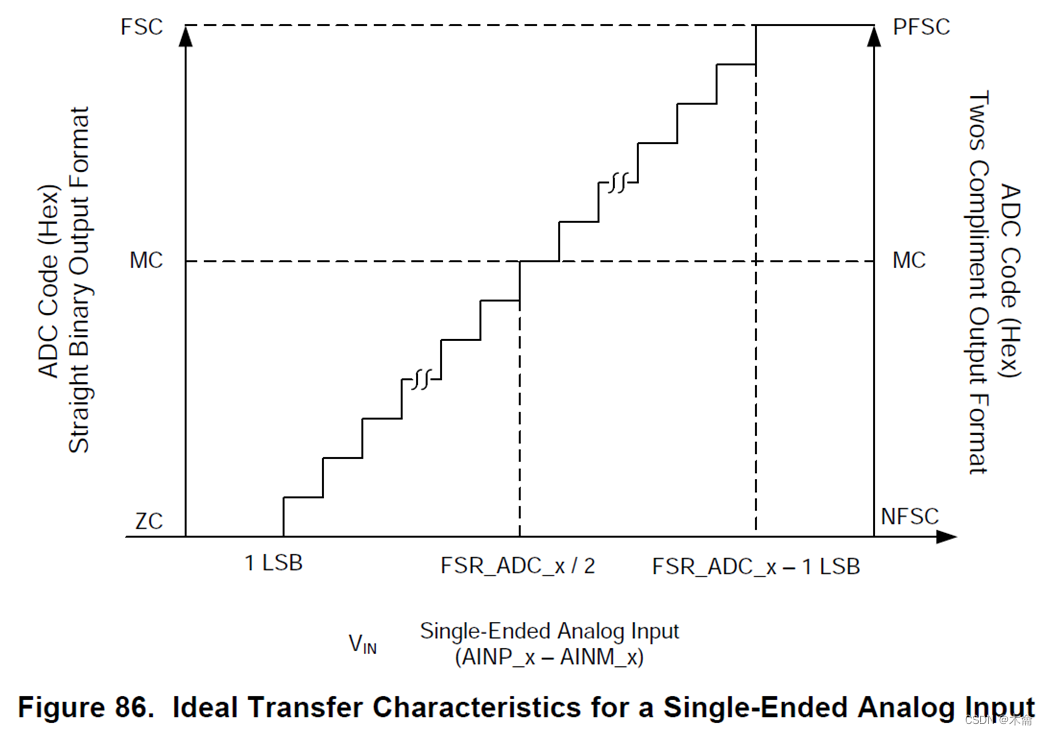

Transfer Function

设备支持两种输入配置:

- Single-ended inputs, CFR.B7 = 0 (default), or

- Pseudo-differential inputs, CFR.B7 = 1.

设备还支持两种输出数据格式:

- Straight binary output, CFR.B4 = 0 (default), or

- Twos compliment output, CFR.B4 = 1.

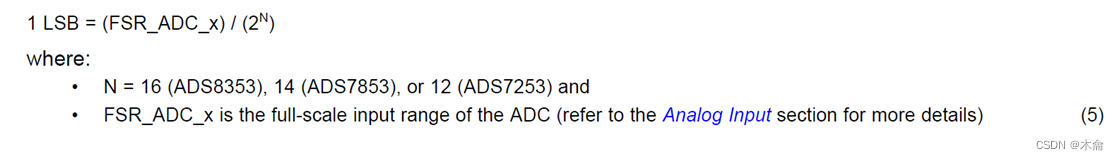

器件分辨率由式5计算:

Device Functional Modes

该设备提供三种用户可编程的寄存器:配置寄存器(CFR)、REFDAC_A寄存器和REFDAC_B寄存器。这些寄存器支持写入(请参阅写入到用户可编程寄存器部分)和读回(请参阅读取用户可编程寄存器部分)操作,并允许用户根据特定的应用需求自定义ADC行为。

该设备支持四种接口模式(请参阅转换数据读取部分),两种低功耗模式(请参阅低功耗模式部分),以及短循环/重新转换功能(请参阅帧中止,重新转换,或短循环部分)。

Register Maps and Serial Interface

- Serial Interface

设备使用串行时钟(SCLK)来同步进出设备的数据传输。

CS信号定义了一个转换和串行传输帧。框架以CS下降边开始,以CS上升边结束。在帧的开始和结束之间,必须提供至少N个SCLK下降边来验证读或写操作。如表4所示,N取决于用于读取转换结果的接口模式。当提供N个SCLK下降边时,在帧中尝试的写操作被验证,并且在随后的CS上升边上更新内部用户可编程寄存器。这个CS上升边缘也结束了这帧。如果在提供N个SCLK下降边之前CS被调高,在帧中尝试的写操作是无效的。

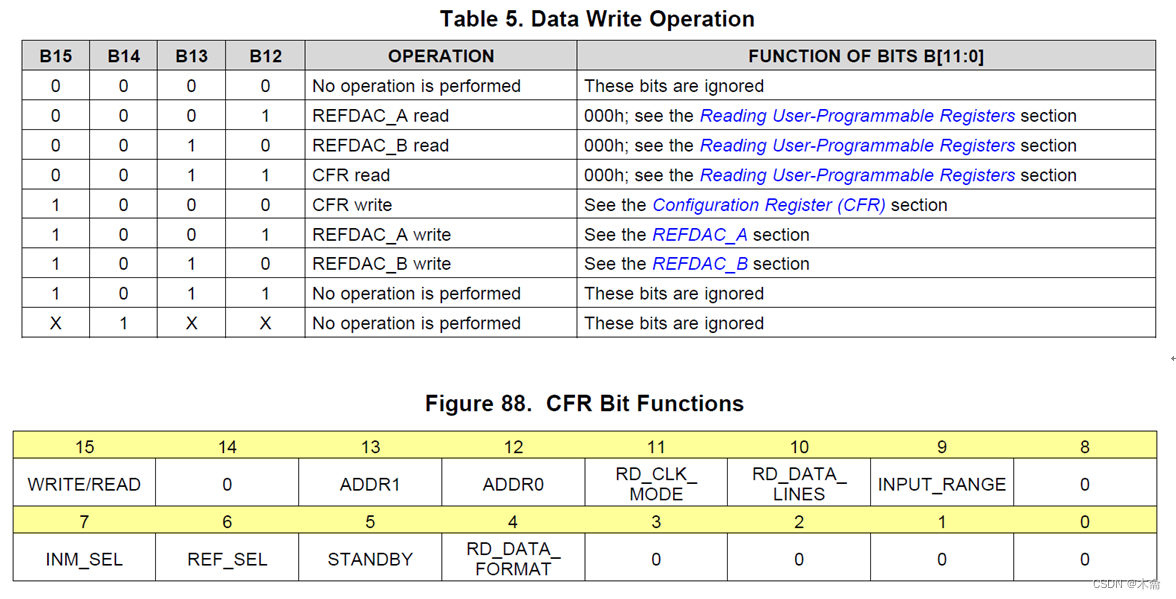

- Write to User Programmable Registers

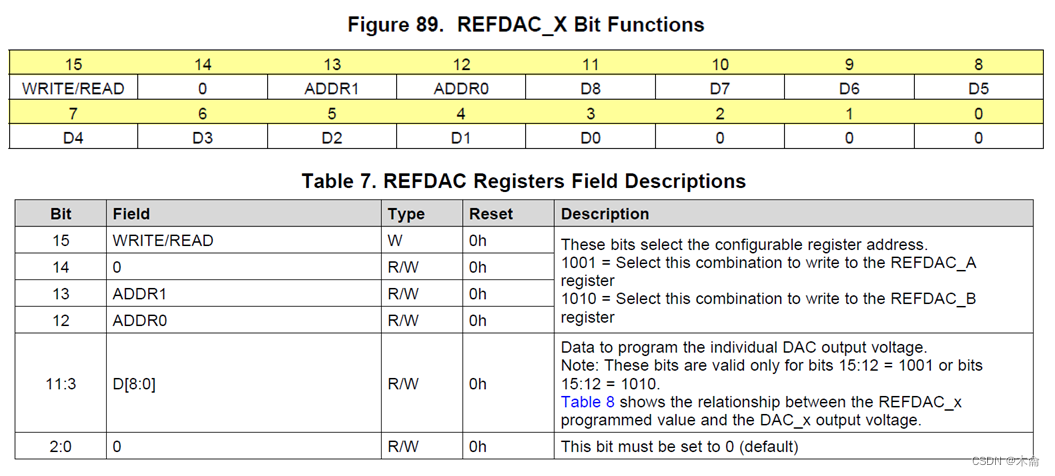

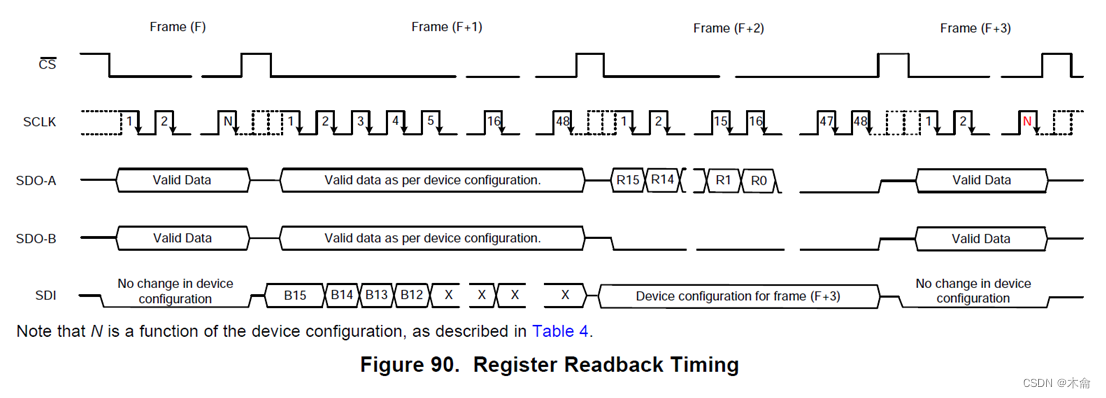

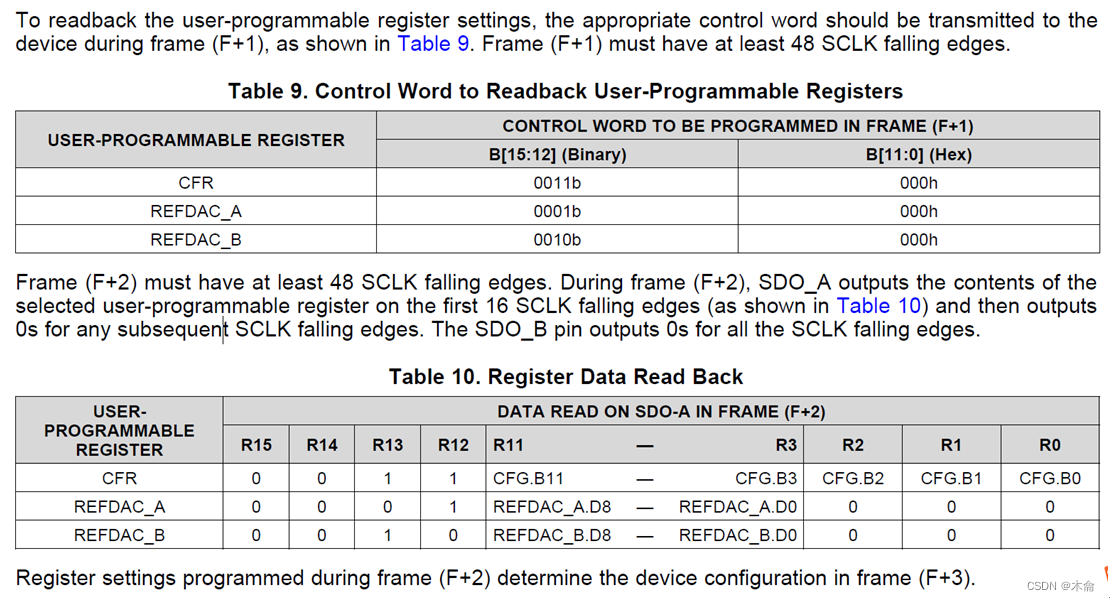

该设备具有三个用户可编程寄存器:配置寄存器(CFR)、REFDAC_A寄存器和REFDAC_B寄存器。这些寄存器可以用器件SDI引脚写入。SDI上的前16位数据在前16个SCLK下降边上锁存到设备中。但是,只有当读写操作验证后,新的配置才生效。如果不需要更新这些寄存器,则SDI必须在相应的帧期间保持低值。前四个SDI数据位(B[15:12])决定执行什么操作(即读或写操作或不操作),该操作使用哪个寄存器地址,以及接下来12个SDI数据位(B[11:0])的功能。表5列出了B[15:12]支持的各种组合。

设备操作配置由配置寄存器CFR (configuration register)状态控制。在有效帧(F)中写入数据到CFR中,在帧(F+1)中确认设备的配置数据。位函数概述于图88。上电时,CFR中的所有位默认为0。

数据读取操作

该设备支持两种类型的读取操作:读取用户可编程寄存器和读取转换结果。

- 读取用户可编程寄存器

- 转换数据读取

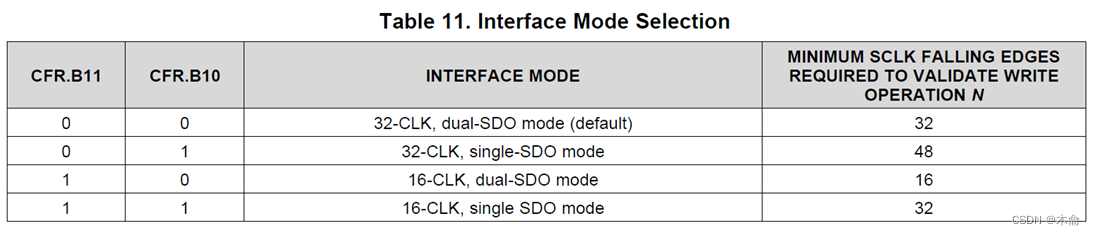

设备提供四种不同的界面模式供用户读取转换结果。这些模式提供了灵活的硬件连接和固件编程。表11显示了如何从四种接口模式中选择一种。

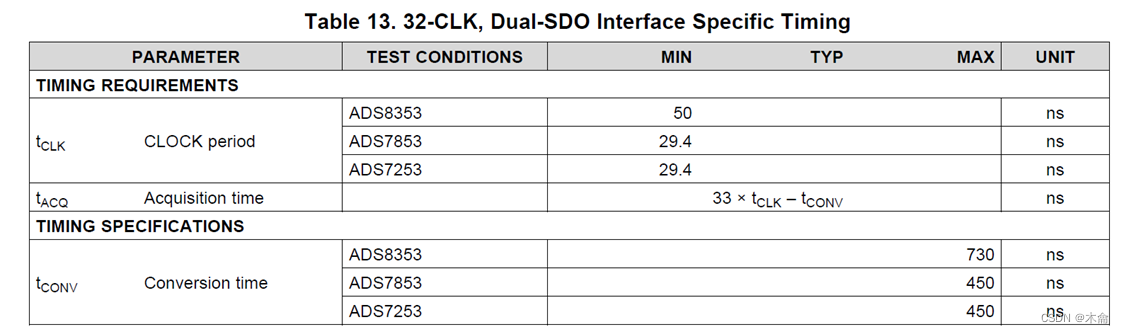

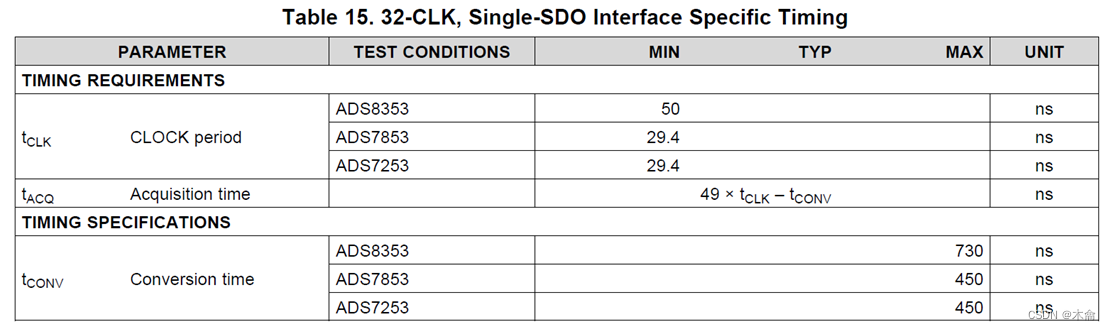

在32-CLK接口模式下,器件使用内部时钟来转换采样的模拟信号。转换在SCLK的前16个周期内完成,转换结果可在后续的SCLK下降边上读取。所有系列设备(ADS8353、ADS7853和ADS7253)都支持32-CLK接口模式。

ADS7853和ADS7253除支持32-CLK接口模式外,还支持16-CLK接口模式。通过使用16-CLK接口模式,可以在低得多的SCLK速度下实现相同的吞吐量。

下面将详细介绍设备支持的各种接口模式。

-

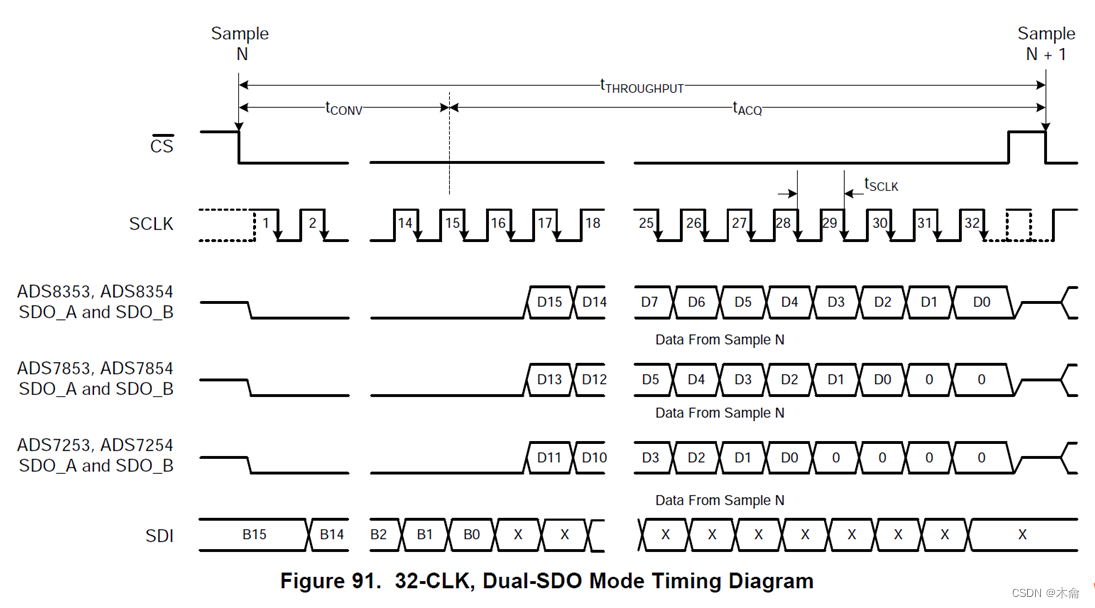

32-CLK, Dual-SDO Mode (CFR.B11 = 0, CFR.B10 = 0, Default)

32-CLK, Dual-SDO Mode是所有设备默认支持的模式。这种模式也可以通过写入CFR来选择。

在这种模式下,SDO_A脚输出ADC_A转换结果,SDO_B脚输出ADC_B转换结果。图91显示了该模式的详细计时图。

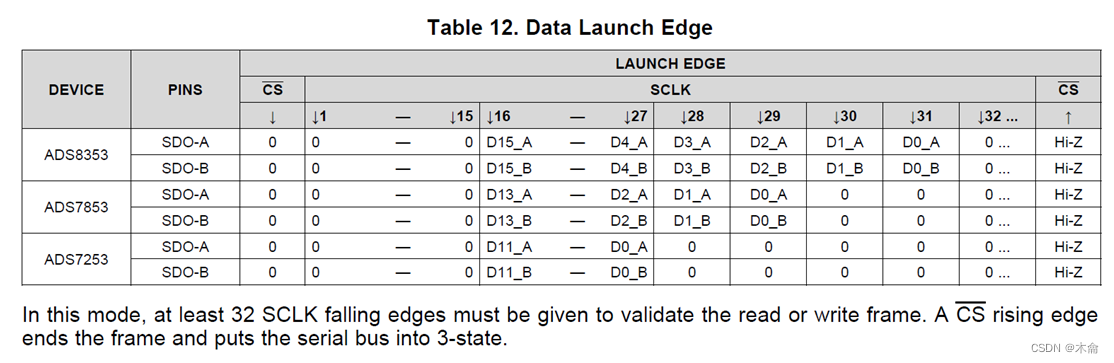

CS下降沿使串行数据总线脱离3-state(高阻态),并在SDO_A和SDO_B引脚上输出0。该设备在转换时间(tCONV)内转换采样的模拟输入。SDO_A和SDO_B在此期间读0。在完成转换过程后,采样-保持电路返回到采样模式。设备于第16个 SCLK下降边缘分别在SDO_A引脚和SDO_B引脚上输出ADC_A和ADC_B的MSB位。后续的SCLK下降边用于移出转换结果的其余位,如表12所示。

在这种模式下,必须给出至少32个SCLK下降边来验证读或写帧。CS上升边结束帧并将串行总线置于3-state(高阻态)。

-

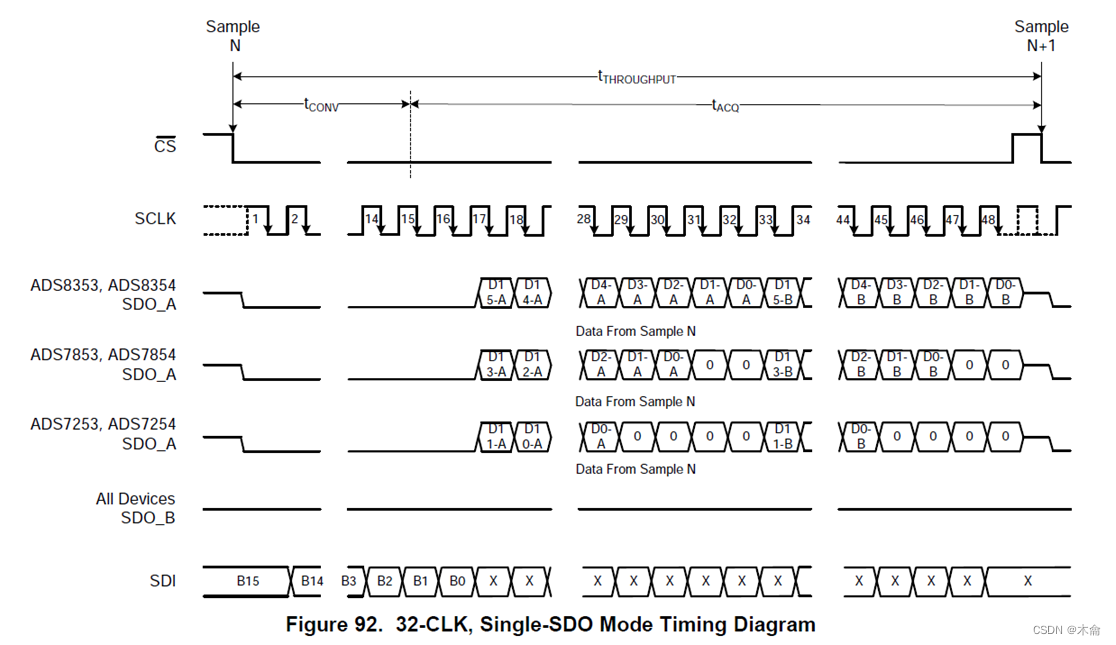

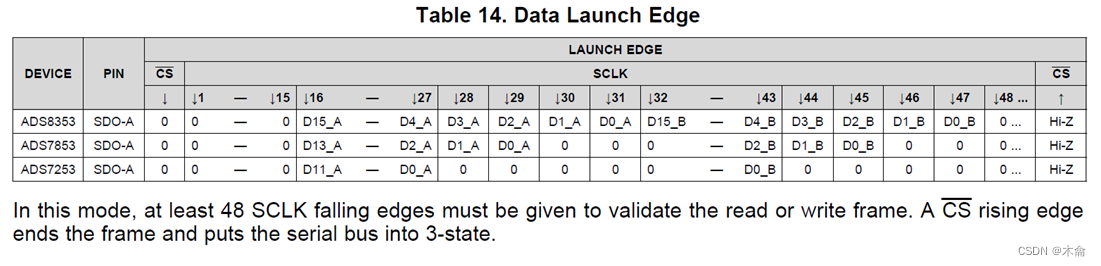

32-CLK, Single-SDO Mode (CFR.B11 = 0, CFR.B10 = 1)

32-CLK, Single-SDO Mode提供了仅使用一个SDO引脚(SDO_A)从两个adc (ADC_A和ADC_B)读取转换结果的选项。SDO_B仍然处于3-state(高阻态),可以视为无连接(NC)脚。

CS下降沿使串行数据总线脱离3-state(高阻态),并在SDO_A引脚上输出0。该设备在转换时间(tCONV)内转换采样的模拟输入。在完成转换过程后,采样和保持电路回到采样模式。器件在第16个SCLK下降边沿SDO_A引脚输出ADC_A的MSB位。后续的SCLK降边用于移出SDO_A引脚上ADC_A的转换结果,然后是ADC_B的转换结果,如表14所示。

在这种模式下,必须给出至少48条SCLK下降边来验证读或写帧。CS上升边结束帧并将串行总线置于3-state(高阻态)。

-

16-CLK, Dual-SDO Mode (CFR.B11 = 1, CFR.B10 = 0)

16-CLK, Dual-SDO Mode设计用于在较低的SCLK频率下支持最大吞吐量。ADS8353不支持此接口模式。 -

16-CLK, Single-SDO Mode (CFR.B11 = 1, CFR.B10 = 1)

16-CLK, Single-SDO Mode提供了仅使用一个SDO引脚(SDO_A)和一个低速时钟来读取两个adc的转换结果的选项。ADS8353不支持此接口模式。

Low-Power Modes

在正常的操作模式下,设备的所有内部电路总是处于通电状态,并且设备总是准备好开始新的转换。该模式使设备能够支持额定吞吐量。设备还支持两种低功耗模式:(STANDBY

mode and software power-down (SPD) mode)待机模式和软件下休眠模式(SPD),以优化低吞吐量下的功耗。

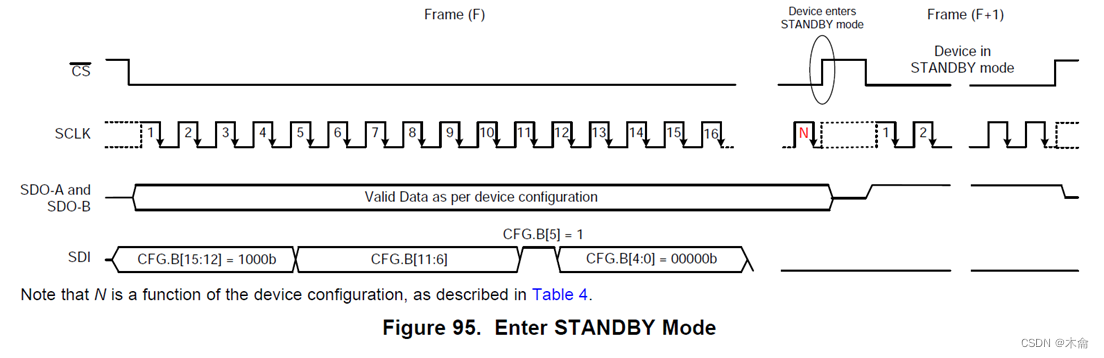

- STANDBY Mode

该设备支持一种待机模式的操作,其中设备的一些内部电路是掉电的。如果配置寄存器的第6位设置为1 (CFR.B6 = 1),则内部参考源不会断电,并且保留REFDAC_A和REFDAC_B寄存器的内容,以便更快地上电到正常操作模式。

如图95所示,帧(F)中一个有效的写入操作,将配置寄存器B5设置为1(CFR.B5 = 1)将在下面的CS上升边设备置于待机模式运行。而在待机模式下,SDO_A和SDO_B在CS低时输出全1, CS高时输出高阻态。为了保持在待机模式,SDI必须在后续帧中保持低。

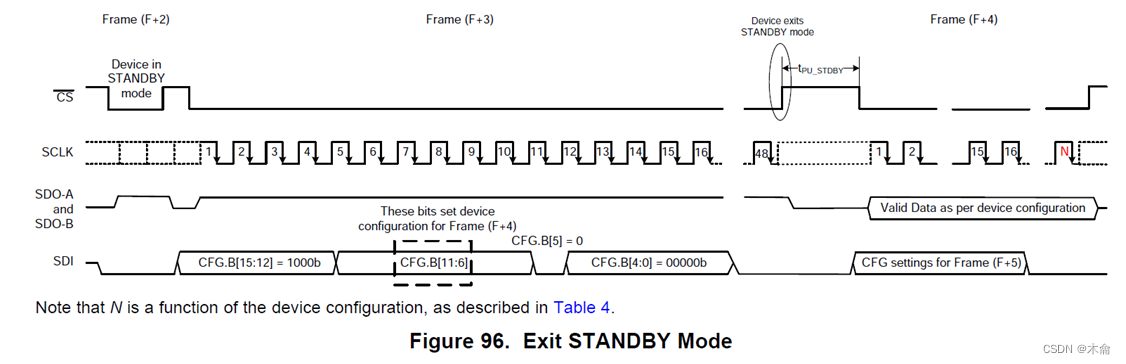

如图96所示,在帧(F+3)中通过将配置寄存器B5设置为0来写入一个有效的写入操作(CFR .B5 = 0)在下面的CS上升沿使设备脱离待机模式。帧(F+3)必须有至少48个SCLK下降边。

退出待机模式后,内部电路必须经过tPU_STDBY延时才能完全上电并在帧(F+4)中恢复正常工作。帧的设备配置(F+4)由帧的状态决定CFR .B[11:6]位在帧(F+3)期间编程。

- Software Power-Down (SPD) Mode

在SPD (software power down)模式下,所有内部电路(包括内部参考电路)都下电。但是,REFDAC_A和REFDAC_B寄存器的内容将被保留。

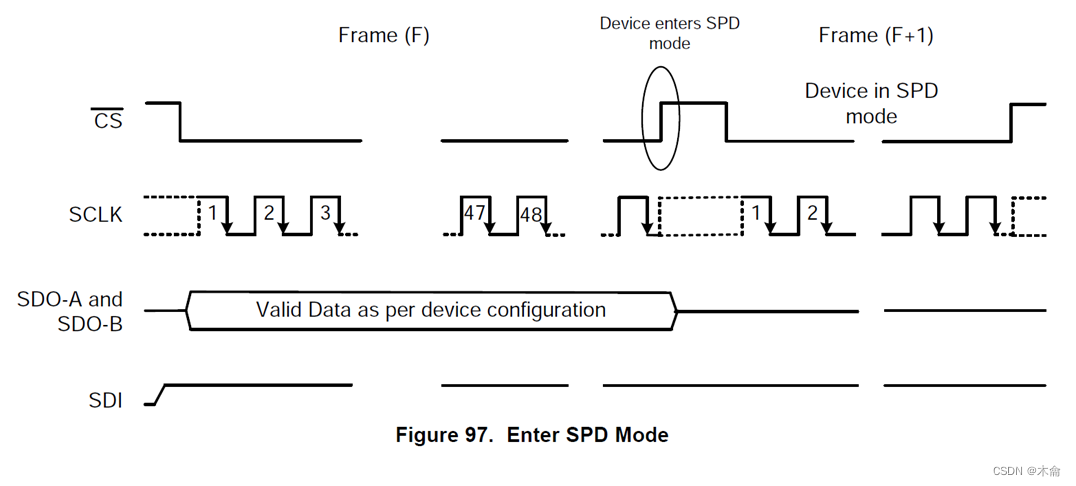

如图97所示,要进入SPD模式,必须在帧(F)中选择器件(将CS调低),并且SDI必须保持高值至少48个SCLK循环。在帧(F)后,器件在CS上升沿上进入SPD。在SPD模式下,无论CS信号状态如何,SDO_A和SDO_B都进入高阻态。

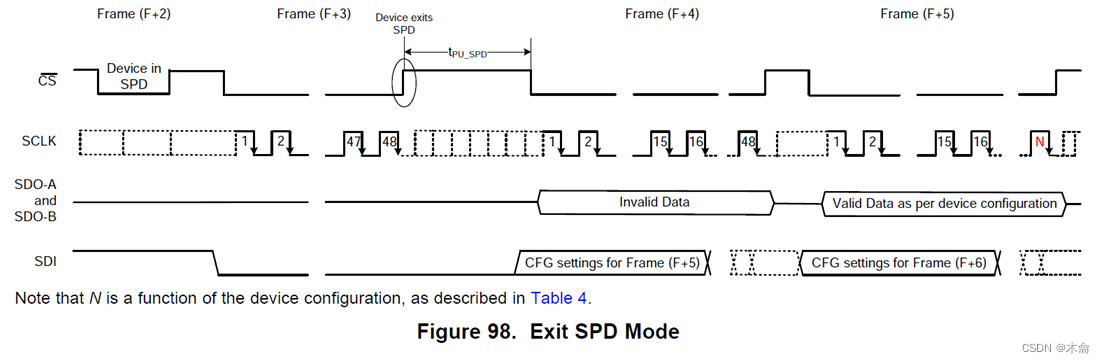

如图98所示,要退出SPD模式,必须选择器件(通过CS置低),并且SDI必须在帧(F+3)期间至少保持48个SCLK周期低电平。设备在CS上升沿帧(F+3)开始上电。帧(F+3)后,在对配置寄存器编程之前,必须经过tPU_SPD的延迟。

在帧(F+4)中通过有效的写入操作来设置设备配置帧(F+5)。帧(F+4)必须有至少48个SCLK下降边。帧(F+4)中的输出数据应该被丢弃。

Frame Abort, Reconversion, or Short-Cycling

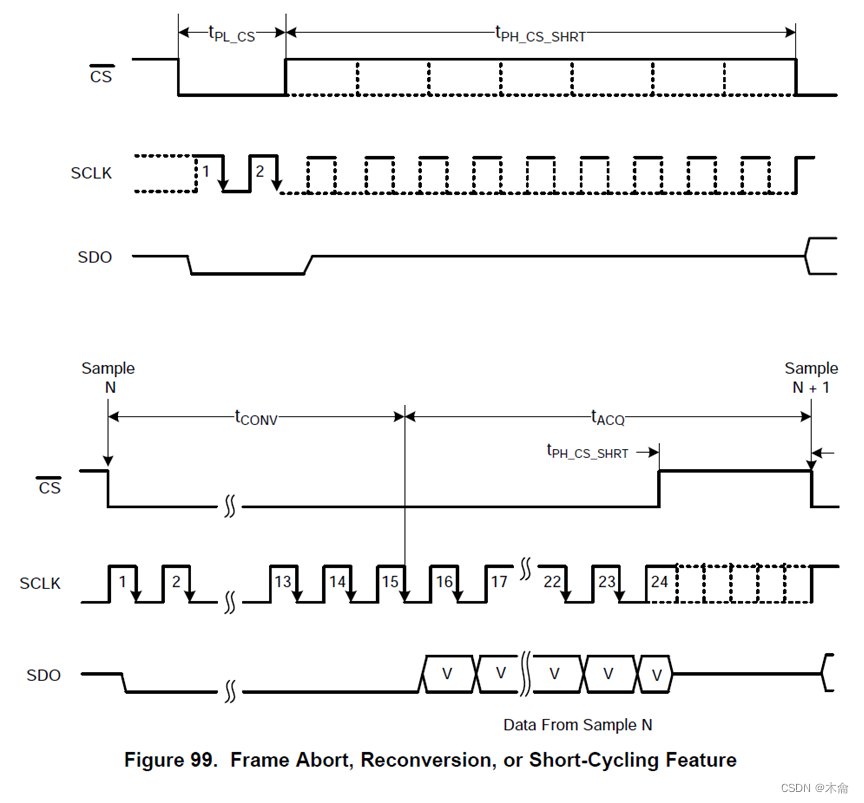

如图99所示,帧的开始和结束之间必须提供的SCLK下降边的最小数目(N)取决于串行接口模式。SCLK降边(N)对器件进行编程并检索转换结果。如果在提供预期的SCLK下降边数量之前CS被带高,当前帧被中止,设备开始对新的模拟输入信号采样。

如果帧(F)被中止,那么在帧(F)中尝试的寄存器写操作被认为是无效的,内部寄存器不会被更新。从帧(F)到帧(F+1),设备继续具有相同的配置。

CS上升边之前锁存的输出数据位仍然是有效数据,对应于样本N。

关于ADS8353的介绍就到这里,下面将进行ADS8353驱动代码的讲解。

代码讲解

驱动ADS8353来读取采样结果就留到下一章讲解吧。

这些器件如ADS8353是双高速同步采样模数转换器,支持单端和伪差分输入,具备16位精度和600KSPS的采样率。设备包含可编程内部参考,可以选择内部或外部参考电压,并且能通过串行接口与主控制器通信。模拟输入可以选择全尺度范围,并且可以配置为单端或伪差分模式。此外,设备还支持多种接口模式和低功耗模式,适应不同应用场景的需求。

这些器件如ADS8353是双高速同步采样模数转换器,支持单端和伪差分输入,具备16位精度和600KSPS的采样率。设备包含可编程内部参考,可以选择内部或外部参考电压,并且能通过串行接口与主控制器通信。模拟输入可以选择全尺度范围,并且可以配置为单端或伪差分模式。此外,设备还支持多种接口模式和低功耗模式,适应不同应用场景的需求。

8016

8016

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?