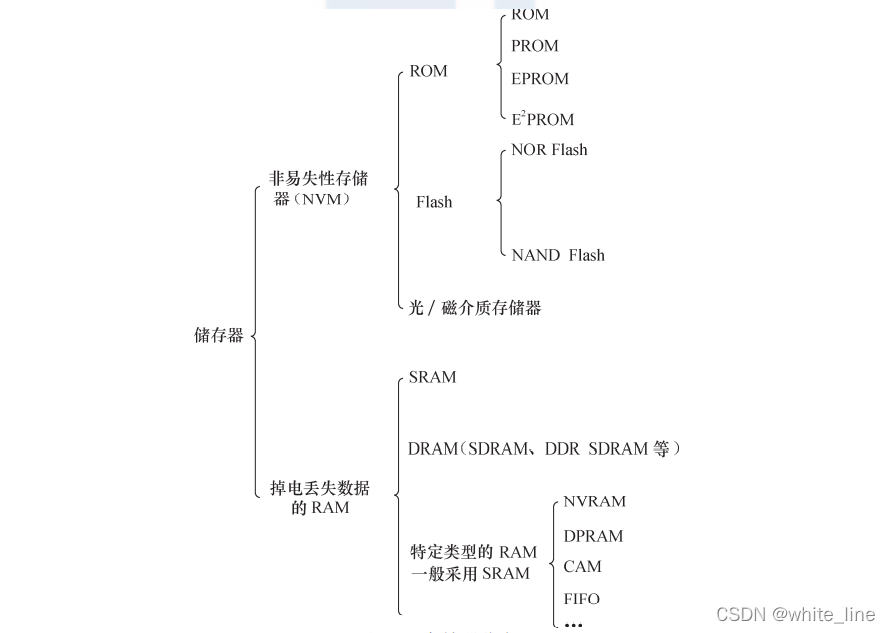

存储器

存储器主要可分类为只读储存器(ROM)、闪存(Flash)、随机存取存储器(RAM)、光 /磁介质储存器。

ROM 还可再细分为不可编程 ROM、可编程 ROM(PROM)、 可 擦 除 可 编 程 ROM(EPROM)和电可擦除可编程 ROM(E2PROM),E2PROM 完全可以用软件来擦写,已经非常方便了。

NOR(或非)和 NAND(与非)是市场上两种主要的 Flash 闪存技术。

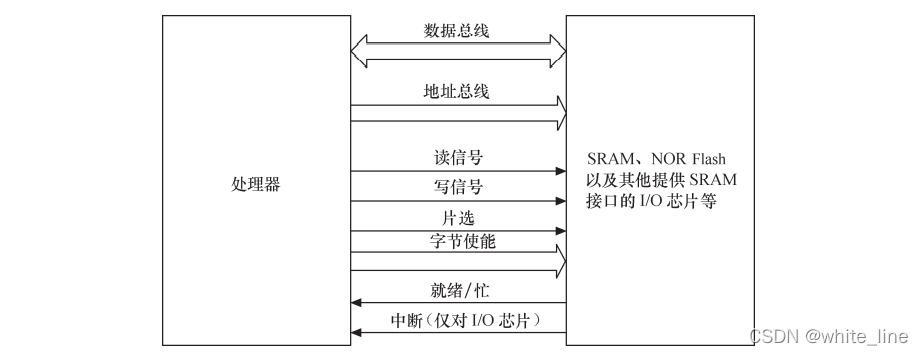

NOR Flash 和 CPU 的接口属于典型的类 SRAM 接口(如下图所示),不需要增加额外的控制电路。NOR Flash 的特点是可芯片内执行(eXecute In Place,XIP),程序可以直接在NOR 内运行。而 NAND Flash 和 CPU 的接口必须由相应的控制电路进行转换,当然也可以通过地址线或 GPIO 产生 NAND Flash 接口的信号。NAND Flash 以块方式进行访问,不支持芯片内执行

公共闪存接口(Common Flash Interface, CFI)是一个从 NOR Flash 器件中读取数据的公

开、标准接口。它可以使系统软件查询已安装的 Flash 器件的各种参数,包括器件阵列结构

参数、电气和时间参数以及器件支持的功能等。如果芯片不支持 CFI,就需使用 JEDEC(Joint

Electron Device Engineering Council,电子电器设备联合会)了。JEDEC 规范的 NOR 则无法

直接通过命令来读出容量等信息,需要读出制造商 ID 和设备 ID,以确定 Flash 的大小。

与 NOR Flash 的类 SRAM 接口不同,一个 NAND Flash 的接口主要包含如下信号。

I/O 总线:地址、指令和数据通过这组总线传输,一般为 8 位或 16 位。

● 芯片使能(Chip Enable,CE#):如果没有检测到 CE 信号,NAND 器件就保持待机

模式,不对任何控制信号做出响应。

● 写使能(Write Enable,WE#):WE# 负责将数据、地址或指令写入 NAND 之中。

● 读使能(Read Enable,RE#):RE# 允许数据输出。

● 指令锁存使能(Command Latch Enable,CLE):当 CLE 为高电平时,在 WE# 信号的

上升沿,指令将被锁存到 NAND 指令寄存器中。

● 地址锁存使能(Address Latch Enable,ALE):当 ALE 为高电平时,在 WE# 信号的上

升沿,地址将被锁存到 NAND 地址寄存器中。

● 就绪 / 忙(Ready/Busy,R/B#):如果 NAND 器件忙,R/B# 信号将变为低电平。该信

号是漏极开路,需要采用上拉电阻。

NAND Flash 较 NOR Flash 容量大,价格低;NAND Flash 中每个块的最大擦写次数是 100

万次,而 NOR 的擦写次数是 10 万次;NAND Flash 的擦除、编程速度远超过 NOR Flash。

由于 Flash 固有的电器特性,在读写数据过程中,偶然会产生 1 位或几位数据错误,即

位反转,NAND Flash 发生位反转的概率要远大于 NOR Flash。位反转无法避免,因此,使用

NAND Flash 的同时,应采用错误探测 / 错误更正(EDC/ECC)算法。

Flash 的编程原理都是只能将 1 写为 0,而不能将 0 写为 1。因此在 Flash 编程之前,必

须将对应的块擦除,而擦除的过程就是把所有位都写为 1 的过程,块内的所有字节变为

0xFF。另外,Flash 还存在一个负载均衡的问题,不能老是在同一块位置进行擦除和写的动

作,这样容易导致坏块。

值得一提的是,目前 NOR Flash 可以使用 SPI 接口进行访问以节省引脚。相对于传统的

并行 NOR Flash 而言,SPI NOR Flash 只需要 6 个引脚就能够实现单 I/O、双 I/O 和 4 个 I/O

口的接口通信,有的 SPI NOR Flash 还支持 DDR 模式,能进一步提高访问速度到 80MB/s。

IDE(Integrated Drive Electronics)接口可连接硬盘控制器或光驱,IDE 接口的信号与

SRAM 类似。人们通常也把 IDE 接口称为 ATA(Advanced Technology Attachment)接口,不

过,从技术角度而言,这并不准确。其实,ATA 接口发展至今,已经经历了 ATA-1(IDE)、

ATA-2(Enhanced IDE/Fast ATA,EIDE)、ATA-3(FastATA-2)、Ultra ATA、Ultra ATA/33、

Ultra ATA/66、Ultra ATA/100 及 Serial ATA(SATA)的发展过程。

很多 SoC 集成了一个 eFuse 电编程熔丝作为 OTP(One-Time Programmable,一次性可编

程)存储器。eFuse 可以通过计算机对芯片内部的参数和功能进行配置,这一般是在芯片出厂

的时候已经设置好了

以上所述的各种 ROM、Flash 和磁介质存储器都属于非易失性存储器(NVM)的范畴,掉电时信息不会丢失,而 RAM 则与此相反。

RAM 也可再分为静态 RAM(SRAM)和动态 RAM(DRAM)。DRAM 以电荷形式进

行存储,数据存储在电容器中。由于电容器会因漏电而出现电荷丢失,所以 DRAM 器件需

要定期刷新。SRAM 是静态的,只要供电它就会保持一个值,SRAM 没有刷新周期。每个

SRAM 存储单元由 6 个晶体管组成,而 DRAM 存储单元由1 个晶体管和 1 个电容器组成。

通常所说的 SDRAM、DDR SDRAM 皆属于 DRAM 的范畴,它们采用与 CPU 外存控制

器同步的时钟工作(注意,不是与 CPU 的工作频率一致)。与 SDRAM 相比,DDR SDRAM

同时利用了时钟脉冲的上升沿和下降沿传输数据,因此在时钟频率不变的情况下,数据传

输频率加倍。此外,还存在使用 RSL(Rambus Signaling Level,Rambus 发信电平)技术的

RDRAM(Rambus DRAM)和 Direct RDRAM

-

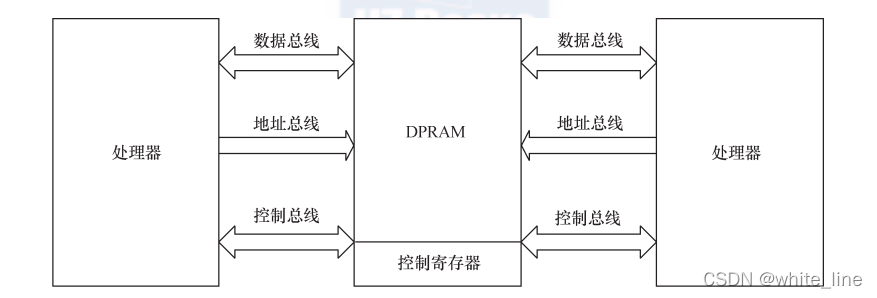

DPRAM:双端口 RAM

DPRAM 的特点是可以通过两个端口同时访问,具有两套完全独立的数据总线、地址总

线和读写控制线,通常用于两个处理器之间交互数据,如下图所示。当一端被写入数据后,

另一端可以通过轮询或中断获知,并读取其写入的数据。由于双 CPU 同时访问 DPRAM 时

的仲裁逻辑电路集成在 DPRAM 内部,所以需要硬件工程师设计的电路原理比较简单。

DPRAM 的优点是通信速度快、实时性强、接口简单,而且两边处理器都可主动进行数

据传输。除了双端口 RAM 以外,目前 IDT 等芯片厂商还推出了多端口 RAM,可以供 3 个

以上的处理器互通数据。 -

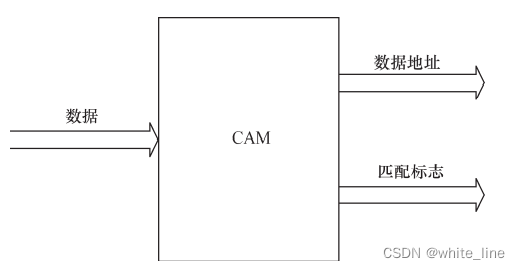

CAM:内容寻址 RAM

CAM 是以内容进行寻址的存储器,是一种特殊的存储阵列 RAM,它的主要工作机制就

是同时将一个输入数据项与存储在 CAM 中的所有数据项自动进行比较,判别该输入数据项

与 CAM 中存储的数据项是否相匹配,并输出该数据项对应的匹配信息。

如下图所示,在 CAM 中,输入的是所要查询的数据,输出的是数据地址和匹配标志。若匹配(即搜寻到数据),则输出数据地址。CAM 用于数据检索的优势是软件无法比拟的,它可以极大地提高系统性能。

- FIFO:先进先出队列

FIFO 存储器的特点是先进先出,进 出 有 序,FIFO 多用于数据缓冲。

FIFO 和 DPRAM 类似,具有两个访问端口,但是 FIFO 两边的端口并不对等,某一时刻只能设置为一边作为输入,一边作为输出。如果 FIFO 的区域共有 n 个字节,我们只能通过循环 n 次读取同一个地址才能将该片区域读出,不能指定偏移地址。对于有 n 个数据的 FIFO,当循环读取 m 次之后,下一次读时

会自动读取到第 m + 1 个数据,这是由 FIFO 本身的特性决定的。

上文摘抄自《Linux设备驱动开发详解:基于最新的Linux 4.0内核》

732

732

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?