写在前面,Modelsim仿真Ip核在网上看见很多方法,也都一一去试了,用quartus自带的altera-modelsim去仿真是不需要担心库没添加的问题的,但这种方法在修改代码后很费时间,还有一种就是将quartus的库全部装到Modelsim中,等需要添加库的时候就添加。这个方法确实不错,搞了一天最后才知道正确的操作步骤。

感谢七水添加链如何用ModelsimSE仿真IP核-以PLL为例接描述按照七水的步骤完成了安装quartus的操作,另外说一句第七步在Modelsim SE 10.4版本里,modelsim.ini文件的库的物理路径是顺斜杠或反斜杠都可以。

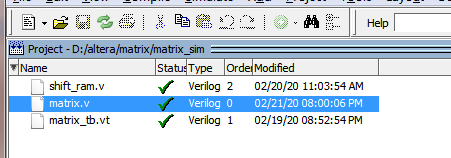

第一个失误点在于新建仿真工程的时候没有将Ip核生成的 .v 文件加入工程,出现** Error: D:/altera/hellow/matrix.v(59): Module ‘shift_ram’ is not defined.# Optimization failed

shift_ram IP核模块未定义

添加进去后再编译一下就可以了

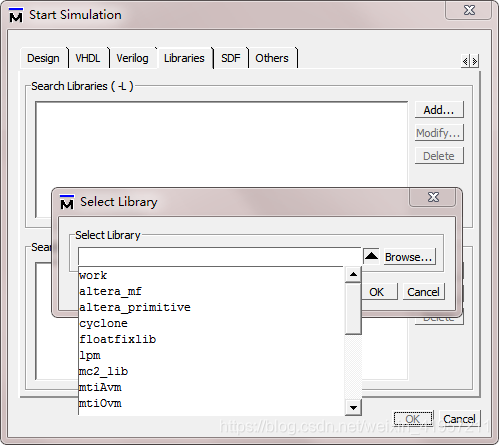

第二个失误点在点击 Simulate>start simulation 后没有在Libraries 页面添加库,天真以为Modelsim能够自动添加你已经添加的库。我是把安照七水的步骤添加的4个库全部添加了的,

在这里插入图片描述

在这里插入图片描述

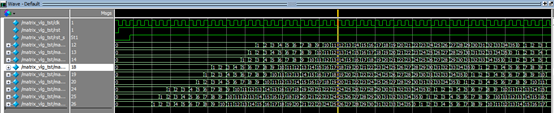

之后就可以正常仿真了

如果修改了源文件,可以在Modelsim仿真页面 project 右键重新编译

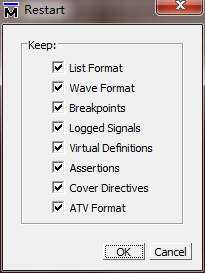

编译好后点击 Restart

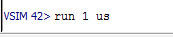

从新开始仿真

2777

2777

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?