VCS仿真步骤

两步法:

范围:

只支持Verilog和systemVerilog语言编写的工程,不支持带vhdl语言的工程编译

步骤:

1. 编译(Compilation):vcs,编译是仿真的第一步,此时VCS构建实例层次结构并生成一个二进制可执行的simv,之后用于仿真。

2. 仿真(Simulation):simv,在编译过程中,VCS生成一个二进制可执行文件simv,使用simv来运行仿真。根据编译的方式,可用两种模式运行仿真:

- Interactive mode:在初始阶段以交互模式(调试模式)编译design。在这个阶段,可以使用GUI或通过命令行调试design问题。通过GUI进行调试可以使用Verdi,通过命令行进行调试可以使用UCLI (Unified command line interface),注:需要在Elaboration 时使用-debug_access

- batch mode:当大多数design问题解决后,可以使用批处理模式(优化模式)编译design。在这个阶段,可以以最小的debug性能来换取更好的性能来运行回归。注:此模式下使用-debug_access选项会降低运行性能

三步法:

范围:

支持VHDL、Verilog和混合HDL编译

步骤:

1. Analysis:分析vhdl、verilog、SystemVerilog和OpenVera 文件,做语法检查。vhdlan对应VHDL,vlogan对应Verilog

- Analyzing your VHDL files:

vhdlan [vhdlan_options] file1.vhd file2.vhd

- Analyzing your Verilog files:

vlogan [vlogan_options] file1.v file2.v

- Analyzing your SystemVerilog files:

vlogan -sverilog [vlogan_options] file1.sv file2.sv file3.

- Analyzing your OpenVera files:

vlogan -ntb [vlogan_options] file1.vr file2.vr file3.v

- Analyzing your SystemVerilog and OpenVera files:

vlogan -sverilog -ntb [vlogan_options] file1.sv file2.vr file3.v

2. Elaboration:编译每个instance,并建立hierarchy关系,生成可执行simv 文件。可选择优化模式或调试模式来细化design

3. Simulation:执行前面生成的simv文件,进行动态仿真

VCS选项:

vlogan选项:

| 选项 | 含义 |

| -h | 显示vlogan的使用信息 |

| -sverilog | 启用SystemVerilog源代码分析 |

| -kdb | 使能生成verdi KDB 数据库 |

| -full64 | 使用64位模式编译和仿真 |

| +v2k | 启用Verilog 2001架构 |

| -timescale=time_unit/time_precision | 仿真时间单位和精度d'd'd |

| -l <filename> | 指定VCS记录编译消息和运行时消息的日志文件,即vlogan.log |

| -f <filename> | 指定包含源文件路径名列表和所需分析选项的文件,即filelist |

| -q | 屏蔽所有vlogan信息 |

| +error+count | 设置 VCS 详细说明错误计数限制 |

| -top | 用于指定描述顶层配置或设计模块 |

| -V | 启用警告消息并显示每个命令使用的时间 |

| -v <filename> | 指定verilog库文件 |

| -y <library_directory> | 指定Verilog库路径。将此选项与+libext+扩展名一起使用+ |

| +libext+<扩展名> | 指定VCS仅在具有指定扩展名的Verilog库目录中搜索源文件。可以指定多个扩展名,并用+分隔每个扩展名 |

| +incdir+directory+ | 指定VCS搜索包含文件的directory目录,可以使用加号(+)字符指定多个目录 |

| +vcs+lic+wait | 等License |

| error=noMPD | 编译重复定义文件,在允许覆盖的情况下,消除并不报error |

vcs选项:

注:-的一般是编译时用的,编译工具自带的。+的是插件,环境,验证语言,等等可扩展的

| 选项 | 含义 |

| -h | 列出最常用的VCS编译和运行时选项的描述 |

| -R | 编译后立刻自动仿真 |

| -V | verbose模式,“啰嗦模式”,打印出仿真真正用的选项 |

| -q | “安静模式”,屏蔽VCS的编译信息 |

| -notice | 显示诊断消息 |

| +define+<macro_name>=<value> | 命令行进行宏定义,在代码中使用了`ifdef 编译指令 |

| -l <filename> | vcs编译时产生的信息写到文件中,即vcs.log 如果还有-R选项,VCS将在同一个文件中记录编译和仿真的消息 |

| -o <name> | 指定编译生成的可执行文件的名称,默认是simv |

| -gui | 仿真时打开DVE gui界面 |

| +vcs+lic+wait | 等License |

| -full64 | 使用64位模式编译和仿真 |

| -kdb | 使能生成verdi KDB 数据库 |

| +vcs+lic+wait | 等License |

| -lca | Limited Customer Availability,客户定制化特性 |

| -Mupdate | 增量编译,节省编译时间 |

| -partcomp | 分布编译 |

| -fastpartcomp=j<number_of_processes> | 多核分布编译 |

| -j<number_of_processes> | 设定并行编译的进程数,“j”后面没有空格 |

| -xlrm | 使能VHDL特性 |

| -ntb | 使能ntb(Native TestBench),支持OpenVera验证平台语言结构 |

| -timescale=time_unit/time_precision | 在前面且又没有`timescale的源文件指定timescale |

| -override_timescale=time_unit/time_precision | 统一复写掉所有的timescale |

| xprop {-is_active [inst_name] | 不加入-xprop选项时默认的仿真行为是vmerge 从X态传播的严重程度来看,xmerge>tmerge>vmerge |

| +error+< count > | 设置 VCS 详细说明错误计数限制 |

| +vcs+loopreport+<number> | 使能循环检测 |

| +vcs+dumpvars+xxx.fsdb | dump波形为xxx.fsdb,替代代码里$dumpvars |

| -debug_access+<option> | 编译时对代码的控制权限: +w是写 +r是读。+f是force +l 是支持ucli的单步调试。 |

| -debug_region=<option>+<option> | debug应用于代码所需部分: cell+lib:单元库 encrypt:加密模块 tb:testbench dut:非testbench部分 |

| -assert <option> | enable_hier: enable_diag: filter_past:忽略$past中的子序列 |

| -cm line+cond+fsm+branch+tgl+assert | 打开覆盖率分析:行+条件+状态机+分支+翻转+断言 |

| -cm_name <file_name> | 设置保存覆盖率结果的文件名称 |

| -cm_dir <dir_name> | 设置覆盖率文件的路径名 |

| -cm_hier <file_name> | 设置统计覆盖率的范围 |

| -cm_log <filename> | 设置仿真过程中记录覆盖率的log文件名 |

| -cm_count | 在统计是否覆盖的基础上,进一步统计覆盖的次数 |

| -cm_cond | 条件覆盖率: basic:只有逻辑条件,没有多个条件 |

| -cm_cond nocasedef | 在统计case语句的条件覆盖率时,不考虑default条件未达到的情况 |

| -deraceclockdata | 使用时钟数据分辨率可确保始终对数据的先前值进行采样 |

| +optconfigfile | 指定配置文件应用于设计上 |

| +vcs+initreg+0|1|x|z +vcs+initreg+config+<file> | 初始化无复位寄存器的值 |

| +nospecify | 不做反标( 此选项可以适度提高仿真性能) |

| +no_notifier | 屏蔽一些时序检查系统任务中定义的notifier寄存器的翻转(toggling),即notifier寄存器违例后不会x态输出 |

| +notimingcheck | 不做时序检查( 此选项可以适度提高仿真性能) |

| +maxdelays/mindelays/typdelays | 使用SDF文件中的max值/min值/typ值 |

| -sdfretain | IOPATH dalay上会有被反标一段retain路径,到retain时间时,输出会有一段x态一直到iopath_delay结束 -sdfretain=warning:如果retain路径小于delay值,则会列出警告信息 -xlrm alt_retain:只有当信号有变化时sdf retain才表现出来 |

| -negdelay | 使能sdf中的负延时,如不加该选项则所有负延时更改为0 |

| +neg_tchk | 使能负沿时检查 |

| +sdfverbose | 显示打印所有sdf反标warning和error |

| -diag=sdf | 输出统计反标率文件 |

| +delay_mode_zero | 模块的延时使用0 延时 |

simv选项:

| 选项 | 含义 |

| +vcs+lic+wait | 等License |

| -l <filename> | simv编译时产生的信息写到文件中,即simv.log |

| +vcs+stop+time | 指定停止仿真的时间,时间值不大于2**32 |

| +vcs+finish+time | 指定结束仿真的时间,时间值不大于2**32 |

| +vcs+nostdout | 仅对设计的Verilog部分禁用VCS的所有文本输出,包括来自monitor和display的消息和文本以及其他系统任务。如果包含-l选项,VCS仍会将此输出写入日志文件 |

| +vcs+loopreport+<number> | 检查循环次数 |

| -ucli | 使能UCLI命令 |

| +ntb_random_seed | 设置随机种子 |

| -assert <keyword> | 编译时需-assert enable_diag才能用的选项:

编译时需-assert enable_hier才能用的选项:

|

| +fsdb+<option> | +fsdb+glitch=num:控制glitch(毛刺)的dump数量,num取值0~254,0代表将所有的毛刺dump下来 +fsdb+sequential:记录同一时刻下,信号变化的先后顺序 +fsdb+region:记录信号的Event Regions(Active、Inactive、NBA...)信息 |

| +fsdb+delta | dump毛刺,等同于打开上行所有开关 |

| +fsdb+mda | dump多维数组 |

| +fsdb+force | dump force信息 |

| +no_notifier | 不做时序为例后的X态输出 |

| +notimingcheck | 不做时序检查 |

dump波形:

- 首先编译时需加:-simv -fsdb

- 如果想要用verdi打开波形并对照design debug,则需要在vcs 编译时加入 选项 -kdb -lca; 否则生成出来的simv.dair 用verdi打不开,因为里面没有kdb.elab++ database

- Dump波形系统函数:

initial begin $fsdbDumpfile(file_name,file_size(MB)) $fsdbAutoSwitchDumpfile(File_size(MB), File_name, number_of_file) $fsdbDumpMDA(); //dump 二维数组,vcs编译时需加上-debug_access+all $fsdbDumpSVA(depth, instance);//dump assertion,vcs编译时需加上-sverilog -debug_pp $fsdbDumpvars(depth, instance, options); //depth:0 : all signals in all scopes; //depth:n : all signals in the current scope and all scopes n-1 levels below //options:+all:Dump all signals including memory, MDA, packed array, structure, union, power-related, and packed structure //options:+mda:Dump all memory and MDA signals #0 $fsdbDumpon; //开始dump时间 #500000 $fsdbDumpoff; //结束dump时间 ,如果没有开始和结束时间默认从仿真开始到结束 end - 打开波形指令:

$ verdi -sv -f file_list.f -ssf test.fsdb - 打开覆盖率指令:

$ verdi -cov -covdir xxx.vdb

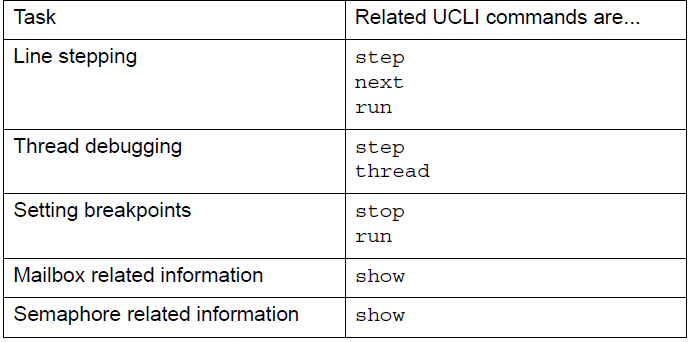

UCLI命令

基本介绍

UCLI,Unified Command Line Interface,提供了与VCS交互仿真的控制命令,即与VCS的命令行输入接口,其命令是基于Tcl脚本语言,主要实现:

- 控制仿真进程

- dump fsdb或者vpd波形文件

- 保存或恢复仿真状态

- force或release某个信号

- 使用breakpoints或scope以及内建宏等信息对设计进行调试

命令

启动方式

simv -ucli -i xxx.tcl编译选项对应的UCLI权限

| vcs选项 | UCLI命令权限 |

| no -debug_access option | run,quit |

| -debug_access | run,quit,dump |

| -debug_access+r -debug_access+all | all UCLI commands |

UCLI常用命令

| 命令 | 描述 |

| run | 运行仿真直到遇到$stop或者设置的断点 run $time:控制UCL的仿真时间 run -posedge xx:运行到信号xx的上升沿停止 |

| stop | 显示已经设置的断点 stop -posedge xx:在信号的上升沿设置断点 stop -delete xx:删除断点xx,xx为断点数字编号 |

| next/step | 仿真运行前进一行代码 |

| finish | 结束进程 |

| scope | 显示当前的顶层 |

| show | 显示当前模块的信号及子模块 |

| force | force信号值 |

| release | release被force的信号 |

| dump | 指定波形文件dump的信息(如文件、层次范围及深度,使能控制,变量等) |

| call | 一个可以调用Verilog或VHDL的接口命令 |

| memory | 从文件中load内存类型值或将内存值write到文件中 eg:memory -write <signal> -file <output_file> |

1335

1335

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?