PRBS是Pseudo Random Binary Sequence的缩写,即“伪随机二进制序列”的意思。PRBS码具有“随机”特性,是因为在PRBS码流中,二进制数“0”和“1”是随机出现的,但是它又和真正意义上的随机码不同,这种 “随机”特性只是局部的,即在周期内部,“0”和“1”是随机出现的(码流生成函数与初始码确定后,码流的顺序也是固定的),但各个周期中的码流却是完全相同的,所以我们称其为“伪”随机码。

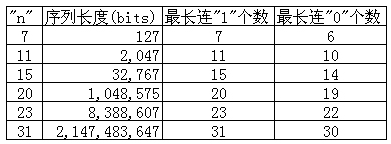

PRBS码的周期长度与其阶数有关,常用的阶数有7、9、11、15、20、23、31,也就是我们常说的PRBS7、PRBS9、PRBS11、PRBS15、PRBS20、PRBS23、PRBS31。

对于n阶PRBS码,每个周期的序列长度为2n-1,在每个周期内,“0”和“1”是随机分布的,并“0”和“1”的个数相等,连“1”的最大数目为n,连“0”的最大数目为n-1(反转后就是n-1个连“1”和n个连“0”)。下图是常用阶数码流参数统计表:

在对高速信号链路进行误码测试时,基本上都是利用PRBS码流来模拟真实的线网码流环境,因为在线网中,所有的数据都是随机出现的,没有任何规律可言,而PRBS码流在一定程度上具有这种“随机数据”特性,二进制“0”和“1”随机出现,其频谱特征与白噪声非常接近。PRBS码流的阶数越高,其包含的码型就越丰富,就越接近真实的线网环境,测试的结果就越准确。

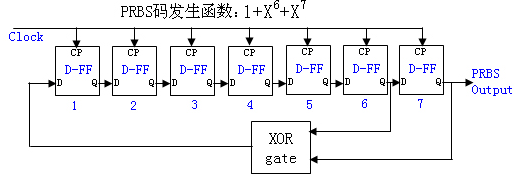

PRBS码型发生器由移位寄存器和异或门(XOR)组成,如下图所示:

如下是一个用PRBS-7 产生伪乱数二进制数列的C语言例程:

#include <stdio.h>

#include <stdint.h>

#include <stdlib.h>

int main ( int argc , char * argv []) {

uint8_t start = 0x02 ;

uint8_t a = start ;

int i ; for ( i = 1 ;; i ++ ) {

int newbit = ((( a >> 6 ) ^ ( a >> 5 )) & 1 );

a = (( a << 1 ) | newbit ) & 0x7f ;

printf ( "%x \n " , a );

if ( a == start ) {

printf ( "repetition period is %d \n " , i );

break ;

}

}

}

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?