上一节讲过FIFO类似一个上下游中间用于缓冲的储水池,因此FIFO的设计对调节上下游的吞吐量平衡具有非常重要的作用,是多bit数据流跨时钟域传输解决方法之一。

https://zhuanlan.zhihu.com/p/344089790zhuanlan.zhihu.com

一、多bit数据流同步策略_异步FIFO

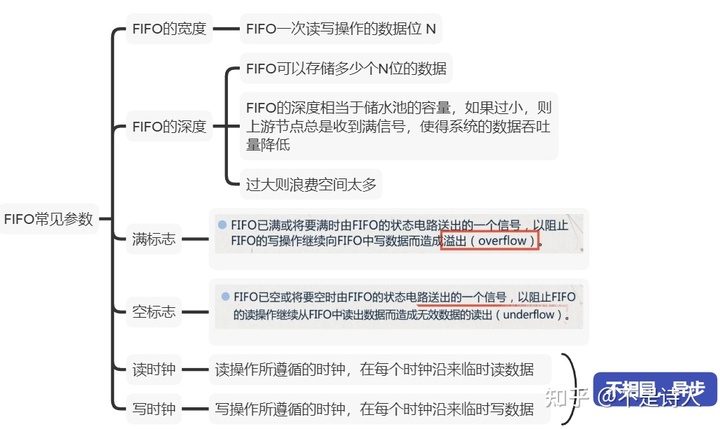

1、异步FIFO常见参数

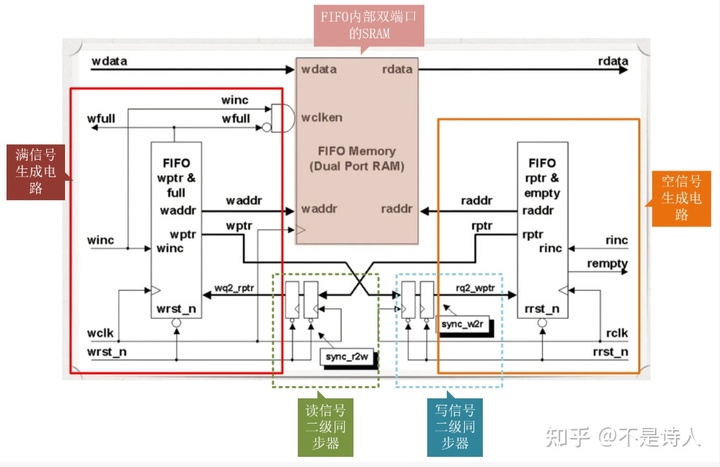

2、异步FIFO的总体结构

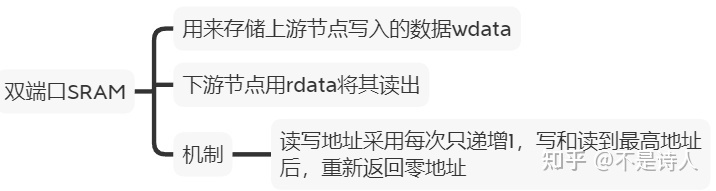

- 双端口SRAM:

- 满信号生成电路

通过判断写时钟域下,写指针和读指针的关系,然后实时生成满信号wfull以通知上游节点停止写操作

- 空信号生成电路

通过判断读时钟域下,写指针和读指针的关系,然后实时生成空信号wfull以通知下游节点停止读操作

- 空/满信号生成前提

- 满信号:将读指针传递到写时钟

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

288

288

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?