辛苦经营公众号到现在,注入了很多感情。

有时候我也会在想:如果有一天,这个号不在了的话,那大家是否会记起曾经还有这么一个公众号陪伴过你。

至少对于我来说,那会是很深一个遗憾。

所以,我就决定,创立一个备用公众号【Office学习社】:

你与selena只差

一个关注

在这个新的公众号里,我也会更多给大家分享Excel、Word和PPT的办公实用技能。

如果你希望一直跟着selena来学习。你可以关注它。如果你觉得没有必要,那么请忽略。

PPT中的技巧,在以前的推文中,都在不断给大家介绍。但是,不得不感叹,PPT真的是太Power了,非常非常多的技巧,总是越用越

一键跳转到指定幻灯片

在做PPT汇报的时候,当我们全屏播放后,有时会想跳转到某一页幻灯片,来回顾某个图或者某个要点。

这时候就不需要按Esc退出放映,然后再去翻到那一页。

高手是这样装13的:

按下 编号+Enter,即可在放映状态下跳转到指定幻灯片。

如果你记不住你想跳转的那一页幻灯片具体的页数怎么办?

很简单,在全屏放映状态下,右键选择【查看所有幻灯片。】

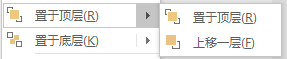

置于顶层或底层

在做PP的时候,经常需要将某一个对象置于顶层,或者置于底层。

通常的操作是:

选中对象,然后鼠标右键选择

那其实是有快捷键,可以帮助我们更高效地实现:

置于顶层:鼠标右键+R+R

置于底层:鼠标右键+K+K

提醒:先点下鼠标右键,弹出右键菜单指令后,再按两下R或K文本快速对齐

选中需要对其的文本,然后我们便可以通过快捷键进行快速对齐:

左对齐:Ctrl+L

居中对齐:Ctrl+E

右对齐:Ctrl+R

当然也适用于,多个文本框,进行对齐。只需把这多个文本框选中,然后再通过上述快捷键进行快速对齐。

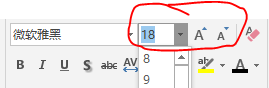

文本快速调节

在做PP的时候,经常我们会根据一个页面里内容的多少而去调整文字大小。

调文字大小,我们一般的方法是:

通过调整字号,或者增大字号、减小字号。

改变文本字号的快捷方法:

放大字号:Ctrl+Shift+>

缩小字号:Ctrl+Shift+<

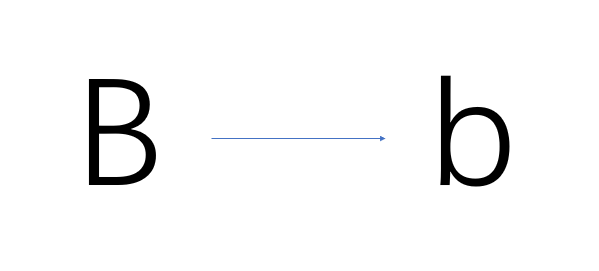

这里补充说下,如何将字母的大小写,进行快速切换:

按 Shift+F3 键即可。

更多PPT小技巧,大家可以翻看以前的一些教程:

有你想看的精彩这几个PPT中的冷门技巧,我敢堵90%的人不知道

这三个PPT小技巧,减少你的烦恼

黑科技| 这几个PPT中的小技巧你应该要学会

告诉你两个少为人知的PPT小技巧

本文分享了PPT中的实用技巧,包括在全屏播放时一键跳转到指定幻灯片、使用快捷键将对象置于顶层或底层以及快速文本对齐和调整字号的方法,帮助提升PPT制作效率。

本文分享了PPT中的实用技巧,包括在全屏播放时一键跳转到指定幻灯片、使用快捷键将对象置于顶层或底层以及快速文本对齐和调整字号的方法,帮助提升PPT制作效率。

605

605

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?