文章目录

1. Feature List

- 收集安全机构产生的每一个alarm信号

- Alarm标志存储在诊断寄存器中,该寄存器仅由上电复位复位,以实现故障诊断和可能的恢复。

- 提供软件模拟硬件alarm的功能,即使用软件去触发一个硬件alarm。

- 提供access protection(先往KEY寄存器写0xBC)和safety ENDINIT来保护配置寄存器。

- 提供FSP(Fault Signaling Protocol)协议,向外部环境报告内部故障。FSP支持以下三种配置方式:

- 使用ErrorPin输出状态(SMU_FSP0推挽输出)

- 在ErrorPins(SMU_FSP0和SMU_FSP1)上使用Timed dual rail coding编码输出

- 在ErrorPin上使用Single-bit timed protocol编码输出

- 微控制器驱动的FSP值可以通过FSP状态寄存器观察到,当故障上报时,可以使用监视器检查FSP协议的定时和状态属性。

- 上电复位后,FSP被禁用。软件需要使用Port寄存器PCSR寄存器将GPIO控制权修改为SMU控制器。

- 每个alarm都可以激活FSP。

- 两个SMU实例:一个SMU_core位于核心域中,另一个SMU_stdby位于的备用域中

- SMU_core中处理的Alarm可以配置来触发以下内部动作之一:

- 生成一个中断请求到任何一个CPU,可以配置中断到多个CPU

- 生成NMI请求到系统控制单元

- 生成复位请求到系统控制单元

- 激活Port紧急停止功能,控制端口输出到安全状态

- 生成CPU复位请求

- SMU_core和SMU_stdby以不同的方式处理所有与电源和温度相关的Alarm。

- 如果SMU_core没有触发配置的反应,则发出SMU Alive告警。

- 复位后,除看门狗超时报警外,所有报警反应都被禁用。。

- 提供锁机制保护SMU配置寄存器(例如在写SMU的配置寄存器时,需要先解锁,即向SMU的KEY寄存器写入固定的值0xBC才会允许写SMU配置寄存器的操作)

- 实现内部看门狗超时预警功能。

- 实现recovery timer的内部看门狗来监视关键软件错误处理程序的执行。看门狗根据Alarm事件由硬件自动启动。

2. 概述

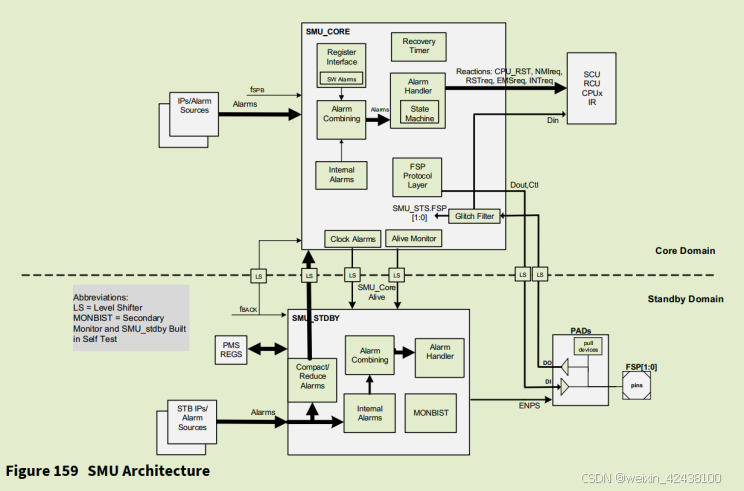

SMU是安全架构的核心组件,提供通用接口来管理故障情况下微控制器的行为。SMU集中了所有与不同硬件和软件安全机制相关的Alarm信号。每个Alarm都可以单独配置为触发内部动作或通过FSP通知外部发生故障。每个报警的严重程度应根据安全应用的需要进行配置:默认情况下,除看门狗超时报警外,每个报警反应都是禁用的。提供一种特殊的测试模式,可以对SMU本身进行测试,从而检测潜在故障。除了寄存器访问保护外,SMU还实现了配置锁定机制。此外,为了减少潜在的共因故障,SMU被划分为两部分:

- SMU_core:位于core域

- SMU_stdby:位于备用域

SMU_core和SMU_stdby在设计方式和时间上各不相同。SMU的两个部分之间存在物理隔离。它们位于不同的时钟和电源域。这允许SMU处理任何传入的Alarm,而不管用于产生该Alarm的时钟频率。同时,在fSPB(或衍生)上产生的Alarm事件由SMU_core处理,在fBACK上产生的Alarm事件由SMU_stdby处理。这样,所有的Clock Alive Monitor Alarm在产生时都在同一个时钟域中进行处理。此外,与电源和温度相关的Alarm以不同的方式处理,因为它们由SMU_core和SMU_stdby处理。可以在SMU_core或SMU_stdby中配置一个或多个反应。

此外,为了检测SMU_core中的错误,smu_core_alive Alarm会从SMU_core发送到SMU_stdby。对这些警报的响应在两个域中都是可配置的。但是对于SMU_stdby,只能配置无响应或ErrorPins作为Alarm响应。SMU与嵌入式安全机制相结合,能够在容错时间间隔内检测和报告微控制器99%以上的关键故障模式。SMU可以配置容错时间间隔的定时特性。

SMU架构图如下:

3. SMU_core

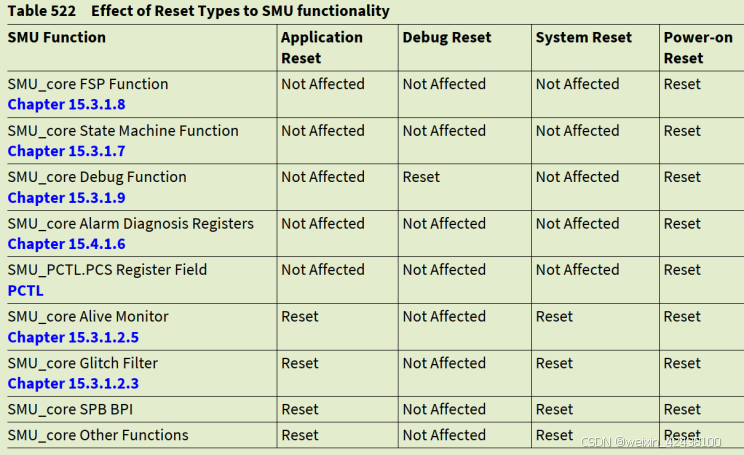

3.1 复位类型

SMU_core需要多种重置类型。复位类型在系统控制单元中完全指定。SMU_core需要的重置类型有:

- Power-on Reset

- System Reset

- Debug Reset

- Application Reset

下表为SMU_core控制配置和逻辑指定了每种复位类型的范围。

3.2 接口介绍

3.2.1 Interfaces to SCU

由报警事件引起的与SCU相连的内部动作。接口信号有:

- Emergency Stop Request

- Reset Request

- NMI Request

- CPU Reset Request

3.2.2 Interfaces to the Interrupt Router

由连接到IR的报警事件引起的内部动作。接口信号有:

- SMU Interrupt Service Request 0

- SMU Interrupt Service Request 1

- SMU Interrupt Service Request 2

SMU中断服务请求到中断路由器(IR)中断节点的映射可以在中断路由器章节(SRC_SMUy, y=0…2)中找到。

IGCSx, x={0,1,2}寄存器字段提供软件接口来控制SMU如何触发中断请求到中断路由器。

每个IGCSx是一个3位的位域,相应位置1后,触发对应通道的中断请求:

- IGCSx[0]设置为“1”触发SMU中断服务请求0

- IGCSx[1]应设置为“1”以触发SMU中断服务请求1

- IGCSx[2]应设置为“1”以触发SMU中断服务请求2

三个IGCSx位域的使用在“Alarm Configuration”章节中定义;

3.2.3 Interface to the Ports (ErrorPin)

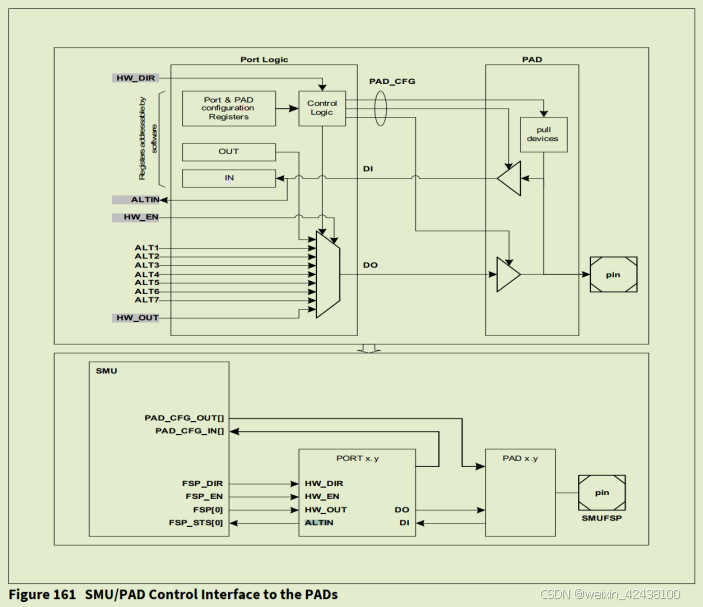

端口引脚可以通过ALTx输出线连接到外设。这是端口上电复位后的默认状态。SMU_core通过HW_DIR、ALTIN、HW_EN、HW_OUT信号与接口相连。当HW_EN端口输入由SMU_core激活时,SMU_core获得对端口的完全控制,绕过与ALTx输入使用相关的任何其他软件配置。

图161提供了端口结构的更详细概述,并突出显示了SMU_core连接中涉及的信号。

SMU_FSP0(图161中的FSP[0])由硬件控制。同样适用SMU_FSP1。FSP_DIR和FSP_EN由软件控制如下:

- FSP_DIR输出直接由PCTL.HWDIR驱动

- FSP_EN输出直接由PCTL.HWEN驱动

PCTL提供了一个PCS位域,结合P33_PCSR.SEL(选择Pin控制器),PCTL,HWDIR,HWEN和PCS,使软件能够改变FSP[0]并控制PAD(完全由SMU硬件控制)。

PCTL寄存器的内容由KEYS寄存器锁定,只有在上电重置时才会重置,因此即使在应用程序或系统重置的情况下,PAD配置也会保持不变。此外,PCTL寄存器使用safety flip-flops安全机制来实现,该机制可以在运行时检测由随机硬件故障引起的任何位变化。

Glitch Filter (not available in TC39x A-Step)

在开漏模式下使用ErrorPin的系统中,故障滤波器可以抑制高达1.2 us的故障。Open Drain模式的情况下,ErrorPin有两个相关的路径:

- ErrorPin to FSP[0],对于这个路径,过滤器可以在GFSTS_EN中打开/关闭

- ErrorPin到ES模块使用,对于这个路径,过滤器可以在GFSCU_EN中打开/关闭。

3.2.4 Interface to SMU_stdby

如果发生故障,SMU_core会向SMU_stdby生成一个信号smu_core_alive。下列条件均会产生该信号:

- 当SMU_core处于RUN或FAULT状态时发生Alarm事件,SMU_core Alive Monitor(SCAM)检测到SMU_core没有生成反应。

- 当SMU_core处于START状态时,发生看门狗或恢复定时器Alarm事件,并且SCAM检测到SMU_core没有生成反应。

- 发送SMU_ActivateFSP或SMU_ActivatePES命令,但SMU_core没有生成相应的响应。

- alarm处理过程中,alarm配置发生变化

smu_core_alive信号可以通过SMU_AliveTest命令进行测试。发送SMU_AliveTest命令会触发SCAM注入故障,并将smu_core_alive Alarm转发给SMU_stdby。无论SMU_stdby是否启用,smu_core_alive Alarm标志可以在AG2i_STDBY(i=1)中读取。可以通过发送带有不同参数的SMU_AliveTest命令来禁用SCAM错误注入(参见表531)。当smu_core_alive Alarm是由实际故障产生时,SMU_AliveTest命令不能清除该Alarm。清除smu_core_alive Alarm至少需要应用复位(系统和上电复位也可以)。

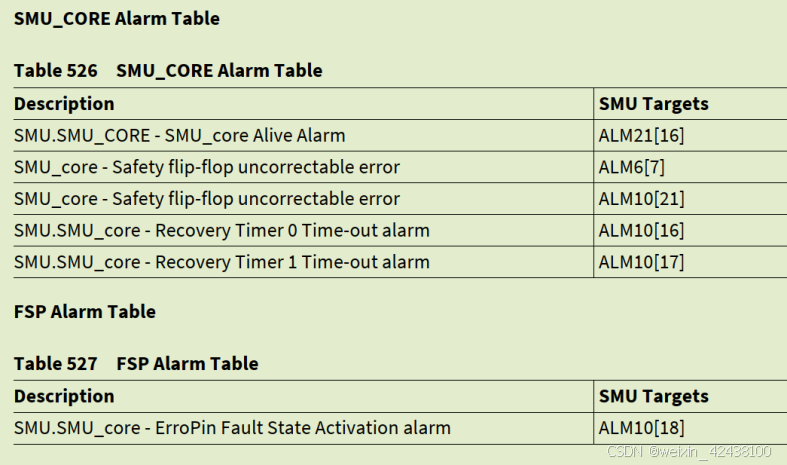

3.3 Alarm Mapping

见‘TC37x A-step User Manual Appendix V2.0.pdf’文档SMU部分。

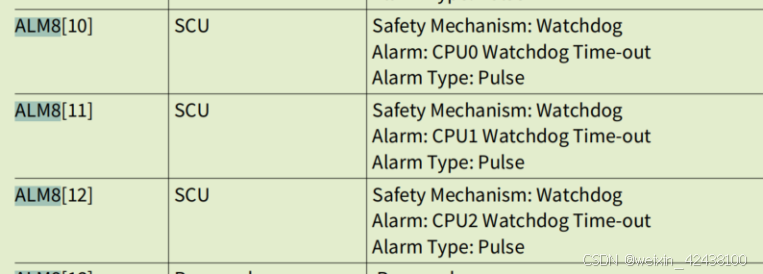

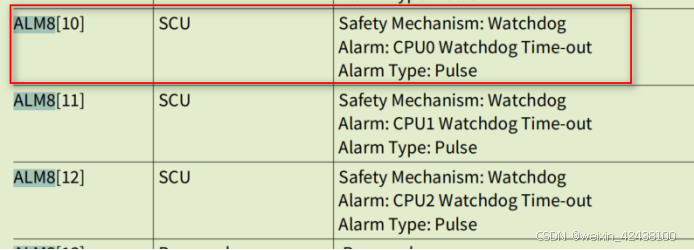

EG:ALM8[10 : 12]分别对应CPU0~CPU2 Watchdog的Timeout Alarm事件。

SMU_core Internal Alarms

3.4 Alarm Handling

3.4.1 Alarm protocol

每个安全机制都应使用预定义的协议与SMU_core接口。该协议允许以可靠的方式跨时钟域。协议的运行对软件层没有影响。

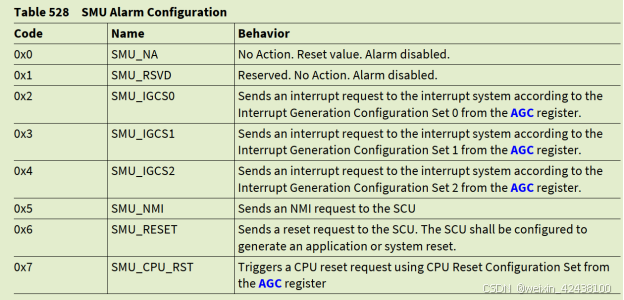

3.4.2 Alarm Configuration

接收到Alarm事件后,SMU_core解码要执行的操作。动作可以分为内部行为和外部行为。可以为每个Alarm配置内部和外部行为。外部行为与FSP有关。

- 外部行为通过AGiFSP (i=0-11)寄存器配置

- 内部行为通过AGiCFj (i=0-11;j=0-2)寄存器控制, 其中i指定Group(ALMi),

AGiCF0、AGiCF1、AGiCF2中的对应的CFx位域(共3bit)组成ALMi[x] Alarm信号的处理方式,3位操作码对应操作如下:

Eg:CPU0 WDG触发超时Alarm信号后,SMU执行SMU_RESET操作。

CPU0看门狗超时信号对应ALM8[10],所以应配置AG8CF0.CF10、AG8CF1.CF10 、AG8CF2.CF10三个位域。

对应AGCF配置值为:

AG8CF0.CF10 = 0

AG8CF1.CF10 = 1

AG8CF2.CF10 = 1

3.4.3 Alarm operation

每当检测到输入Alarm事件并且SMU_core状态机处于RUN或FAULT状态时,SMU就会以并发的方式检查内部操作和FSP的相应操作。

如果检测到输入Alarm事件,且未对该Alarm指定动作,则相应的状态位也应设置为1,但不发生任何动作。对传入的Alarm事件进行如下处理:

- 同时扫描所有Alarm组和每条Alarm。

- 挂起Alarm的执行是并发的。

- 在一个Alarm组中处理一个Alarm可能需要几个fSPB周期。

- 如果进行了错误处理,则设置SMU_AEX寄存器中相应的位。只要设置了该位,就会阻塞相应的故障处理。此位需要在故障处理完成后由SW复位。

- 如果SMU_AEX寄存器中与待处理Alarm相关的Alarm执行位已经设置,则忽略该Alarm事件,但设置状态位(AGi )和相应的Alarm错过事件位(AEX寄存器高16bit)。

- 如果Alarm事件对应的状态标志已经设置为1,则忽略该Alarm事件。

- 当处理Alarm事件时,硬件会将AGi寄存器中对应的状态位置为1。如果配置并执行了内部SMU_core操作,则AFCNT寄存器中的操作计数器(ACNT)会增加。

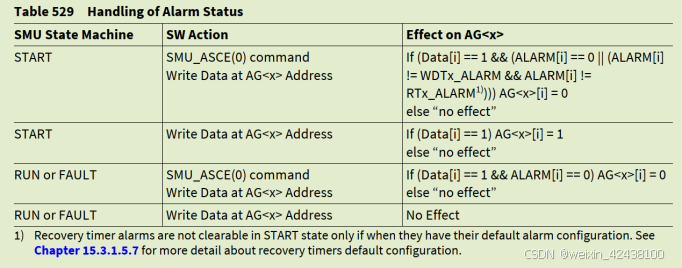

3.4.4 Alarm Status Registers

表529根据SMU_core状态机的状态指定了AGi Alarm组状态寄存器上可能的软件动作。

在START状态下,软件可以通过写入AGi寄存器来“模拟”输入报警事件的发生。软件应回读AGi寄存器,以确保操作完成。清除Alarm,需要软件先写SMU_ASCE(0)命令,在往AGi寄存器写入32bit的值(写1清除标志位,不为0的位域不生效)

3.4.5 Alarm Diagnosis Registers

Alarm诊断寄存器使应用程序能够改进对导致故障的根本原因的诊断。在这种情况下,如果应用程序允许,它们可以帮助实现恢复策略。ADx诊断寄存器应在以下情况下对AGx寄存器进行快照:

- SMU处于RUN或FAULT状态时,SMU被复位

- SMU硬件或软件命令控制SMU_core状态机切换到FAULT状态(RUN ->FAULT, FAULT ->FAULT)

SMU_ADx寄存器只有上电复位时才会被清除。

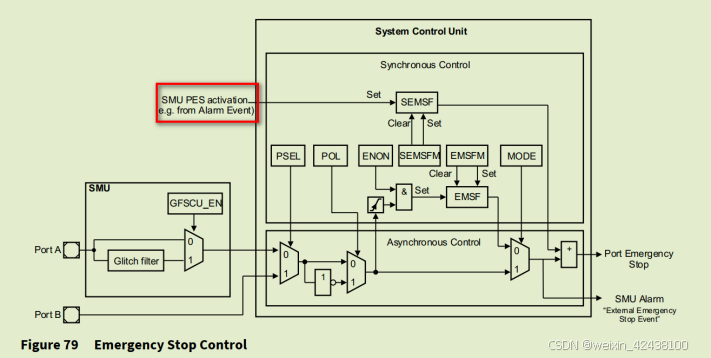

3.4.6 Port Emergency Stop

SMU配合ES模块可以为Port模块提供紧急停止信号,实现Port紧急停止功能,该可以强制Pin由输出变为通用输入模式(三态 or 上拉输入,具体见Port模块)。

SMU共有三个触发源,具体如下:

- SMU_ActivatePES()软件命令

- an alarm event with SMU_AGiFSP enabled and FSP.PES enabled

- 在SMU_AGiCFj寄存器中配置了内部动作的告警事件,并且该动作触发PES信号(SMU_AGC.PES)。

备注:

1、RUN和FAULT状态下,ActivatePES()命令软件触发Alarm,START情下写AGi.SEj寄存器软件触发。

2、第二种没看明白,FSP.PES使能的情况下,FSP对外输出了异常,也触发紧急停止信号?

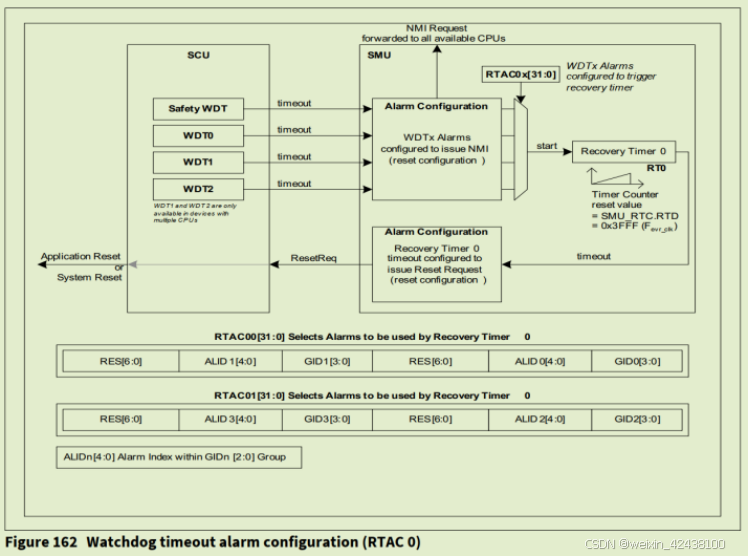

3.4.7 Recovery Timer

恢复定时器(RT)可用于监视Alarm、NMI或中断触发后的持续时间,也可以用于内部错误处理程序。在当前的SMU_core实现中,有两个独立的回复定时器(RT0和RT1)可用。RT持续时间在寄存器RTC中配置。可以启用或禁用每个RT,但是这两个RT在默认情况下都是启用的,因为CPU Watchdog超时Alarm需要使用。除了RTC之外,每个恢复计时器实例都可以使用额外的配置寄存器(RTAC00、RTAC01、RTAC10和RTAC11)来配置警报映射。

RT支持哪些Alarm触发,由GIDi和ALIDi参数配置(其中i = 0…3),其中GIDi是组标识符和实例。

注意:只有当内部动作是中断或NMI时,使用RT才有意义。但是没有进行硬件检查,而是由软件以适当的方式配置SMU_core。

如果使能了RT,并且对于{GIDi, ALIDi]对中的任何一个都发生了Alarm事件,产生了内部动作(Alarm状态被清除),则RT将由硬件自动启动。这种情况称为恢复定时器事件。没有内部动作的Alarm不启动RT。

一旦发生恢复计时器事件,恢复计时器就会启动并计数,直到软件使用SMU_RTStop()停止它。如果定时器超时,则发出SMU内部Alarm(Recovery timer Timeout)。在恢复计时器运行期间,请求RT的其他操作都将被忽略。如果这样的事件发生,STS.RTME(RT错过事件)设置为‘1’。RTME只能通过软件清除。STS.RTS(RT状态)在RT运行期间由硬件设置为‘1’。当接收到SMU_RTStop()或者定时器超时时,硬件会清除RTS状态位。

如果在RT未运行时收到SMU_RTStop()命令,则该命令返回一个错误响应。

注:如果要写RTC.RTD,请确保没有RT正在运行(RT状态由STS寄存器中的RTS0和RTS1位表示)

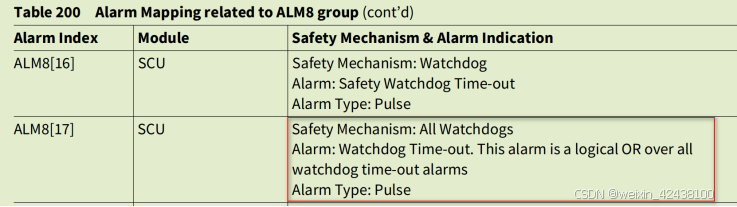

3.4.8 Watchdog Alarms

看门狗(WDT)超时警报需要一个特殊的处理,以确保正确的MCU行为,如果看门狗没有喂狗。应确保MCU在预警阶段后复位,此时软件仍可执行一些关键动作。

- 每个超时警报将激活一个NMI

- 恢复定时器0应配置为WDT(safety,CPU0,CPU1和CPU2)超时报警服务

- 恢复定时器1应配置为WDT(CPU3,CPU4和CPU5)超时报警服务

- 应配置RT0和RT1超时Alarm,以发出复位请求并激活FSP。

上述属性实现为看门狗超时Alarm和RT0/1的重置值。

该图仅显示了RTAC0的示例和相关的四个WDT。RTAC1与相关的WDT3、WDT4和WDT5以同样的方式建立。

因为从CPU执行的第一条指令开始也需要检测看门狗超时,所以SMU应该在START状态期间处理任何看门狗超时Alarm。

注意:如果所有的WDT Alarm都有相同的行为,建议使用所有WDT超时Alarm,它在所有的WDT超时Alarm之间实现一个逻辑或,从而释放RTAC00、RTAC01、RTAC10和RTAC11中的一些{GIDi、ALIDi}配置对,用于其他目的。

备注:

1、GIDx指定ALMx Group,ALIDx指定Group中的哪个Alarm触发RT,每个RT支持四个触发源。如果RT此时正在运行,则触发RT丢失事件,状态保存在STS.RTME。

2、所有WDT超时Alarm为ALM8[17],具体见

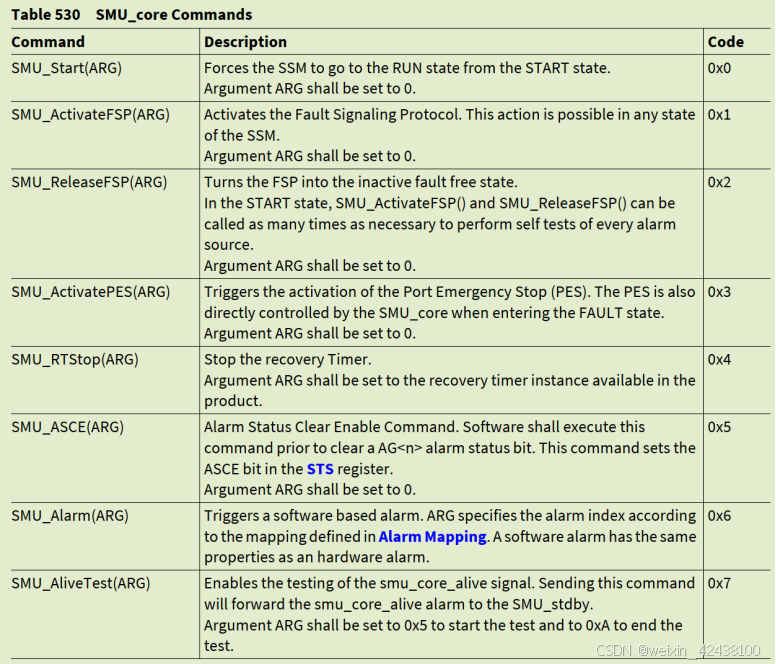

3.5 SMU_core Control Interface

SMU_core的核心功能通过其控制接口介绍。控制接口定义了如何通过软件控制SMU_core,如表530所示。控制接口直接链接到SMU_core state machine中的SSM(SMU_core state machine)操作和FSP(Fault Signaling Protocol)中的FSP协议。控制接口由CMD寄存器的CMD和ARG字段实现。命令完成状态可通过STS寄存器获得。

注意:如果参数不符合命令的规范,命令将被忽略并返回一个错误代码。

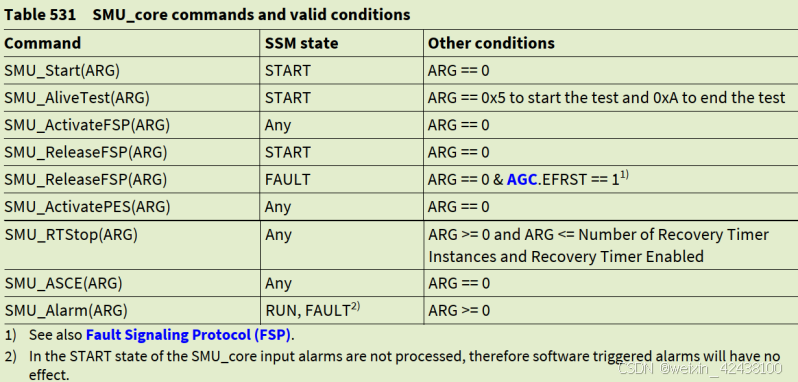

下一个表提供了执行命令的合法条件。这些条件取决于SMU_core状态机(SSM)的状态(参见SMU_core状态机)。任何未指定的情况都会导致错误代码。

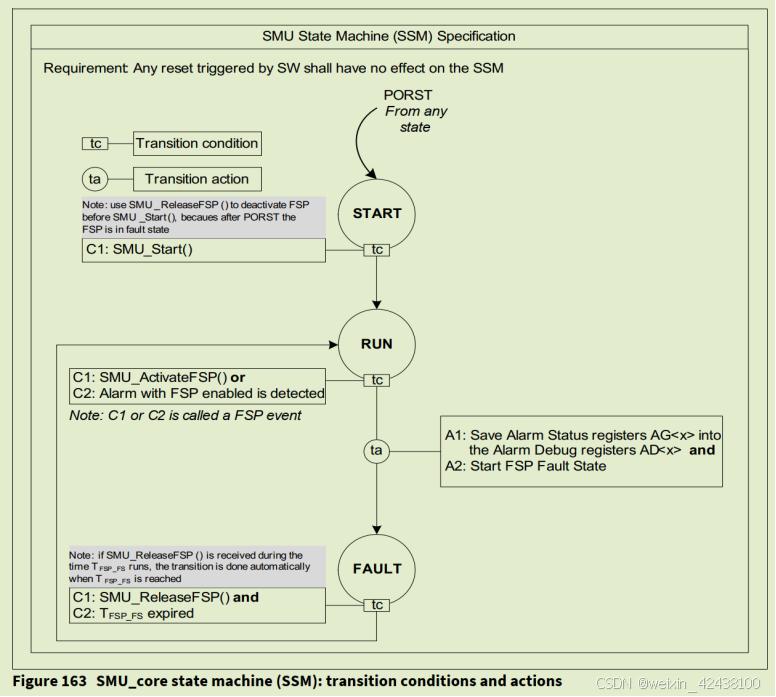

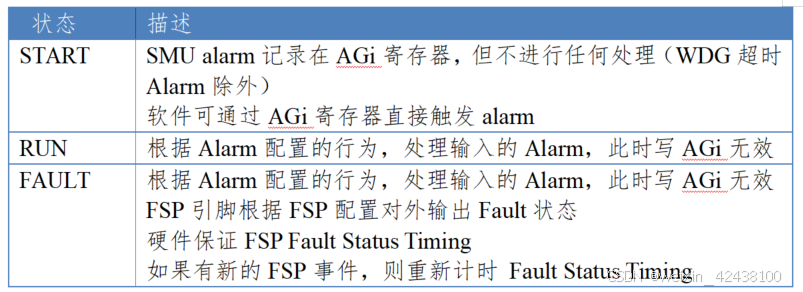

3.6 SMU_core State Machine

故障计数器

SMU实现了一个故障计数器(AFCNT),用于统计从RUN状态到Fault状态的转换次数。故障计数器寄存器只能通过warm power-on-reset清除。

3.7 Fault Signaling Protocol (FSP)

使用FSP[1:0]分别对应P33.10\P33.08两个引脚,P33.08同时是ES的PortA输入引脚。

故障信令协议使微控制器能够向外部安全控制器设备报告危急情况,以控制安全系统的安全状态。

3.7.1 介绍

故障信令协议通过FSP命令寄存器配置。FSP状态由STS寄存器中的FSP标志表示。FSP有三种状态:

- 上电复位状态:热上电复位后,SMU与端口断开。SMU FSP输出为Fault State。

- Fault-free状态:当Fault-fre状态由一个定时控制时,这个定时将被称为TFSP_FFS,并由FSP寄存器控制。

- Fault State:故障状态的时间由FSP寄存器控制。最小活动故障状态时间称为TFSP_FS。

fault -free和fault状态的具体行为可以通过以下协议配置:

- Bi-stable protocol (default)

- Dynamic dual-rail protocol

- Time-switching protocolFSP

FSP可以通过以下方式控制: - 软件使用CMD寄存器发送SMU_ActivateFSP()和SMU_ReleaseFSP()命令

- 基于AGiFSP (i=0-11)配置寄存器的硬件。

为避免出现异常Alarm,建议在SMU在非Fault状态,且FSP协议模式为Bi-stable(FSP.MODE= 00B)时配置PRE1、PRE2或TFSP_HIGH字段。模式切换和配置不能用对寄存器FSP的相同写访问来完成。如果需要写入FSP.PRE1字段,请确保没有恢复定时器正在运行(恢复定时器的状态由STS寄存器中的RTS0和RTS1位表示)。

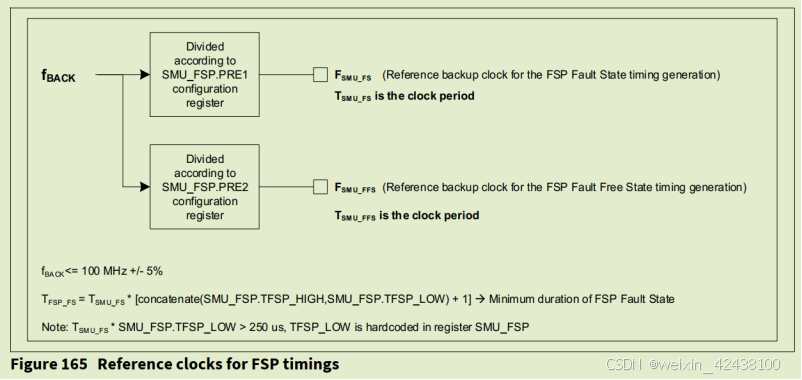

图165指定了生成TFSP_FFS和TFSP_FS计时的中间时钟。

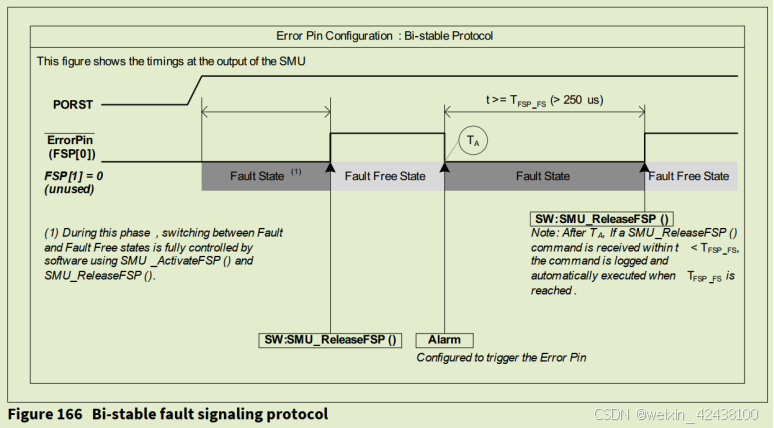

3.7.2 Bi-stable fault signaling protocol

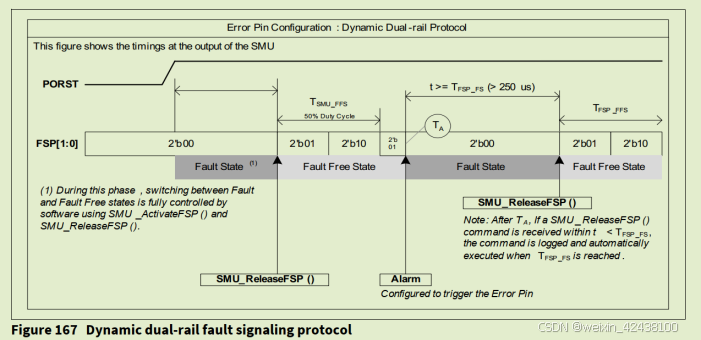

3.7.3 Timed dual rail

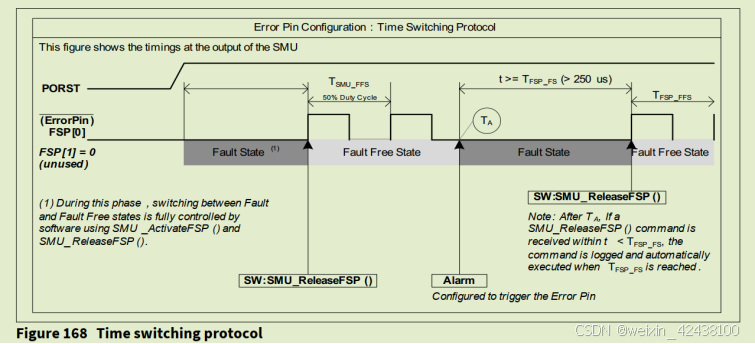

3.7.4 Time switching protocol

3.8寄存器属性

3.8.1 寄存器写保护

在Safety ENDINIT清除的前提下,模块内部通过以下机制保护:

- KEYS.CFGLCK字段设置为0xBC时,才能配置SMU_core的相关寄存器。

- 如果KEYS寄存器的PERLCK字段设置为0xFF,则禁止配置SMU(包括KEYS)。只能通过application reset,将KEYS.PERLCK重置为0x00后,才能继续配置KEYS寄存器。

通过KEYS保护的寄存器有:FSP、AGC、RTC、RTAC00、RTAC01、RTAC10、RTAC11、AGiCFj、AGiFSP 、PCTL、RMCTL。

3.8.2 Safety Flip-flops

安全触发器是一种特殊的触发器,能够检测单事件异常(位翻转)的硬件机制。SMU_core配置和使用安全触发器实现的控制寄存器是:FSP、CMD 、AGC、RTC、KEYS、PCTL、RTAC00、RTAC01、RTAC10、RTAC11、AEX、AGiCFj (i=0-11;j=0-2)、AGiFSP (i=0-11)

此外,下列SMU_core功能也应与Safety Flip-flops一起实现:

- SMU_core状态机寄存器

- 实现FSP功能的寄存器

4. SMU_stdby

4.1 复位类型

SMU_stdby的操作需要多种重置类型。复位类型在电源管理系统中有详细说明。SMU_stdby需要的重置类型有:

- Warm Power-on Reset.

- LVD Reset.

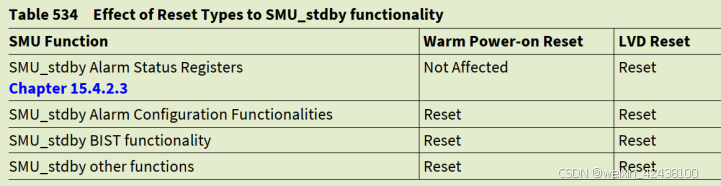

表534为SMU_stdby函数指定了每种重置类型的作用域(一个函数包括控制寄存器和配置寄存器以及相关逻辑)。

4.2 Interface to the Pads (ErrorPin)

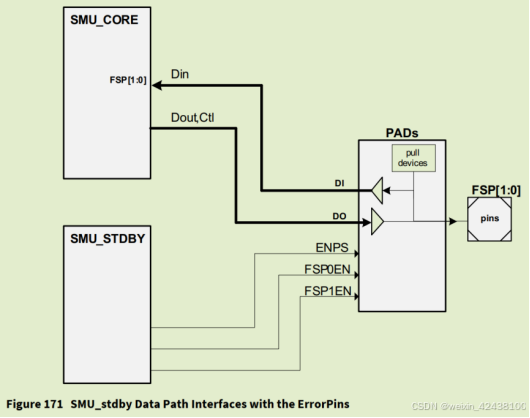

SMU_stdby能够通过FSP ErrorPin向外部世界发出错误信号。图171完整地指定了SMU_stdby与FSP ErrorPins的数据路径连接。

ErrorPin通过两个使能信号FSP0EN和FSP1EN以及ENPS信号连接到SMU_stdby。FSP0EN和FSP1EN由位域CMD_STDBY的FSP0EN和FSP1EN控制。它们使SMU_stdby能够使用ErrorPins。

当设置FSP0EN和FSP1EN时,可以通过SMU_stdby驱动ENPS信号,使FSP[1:0]处于高阻抗状态,而不管Port配置和SMU_core动作如何。

在这种情况下,需要外部下拉设备使高阻抗状态对应于FSP故障状态(为什么不是上拉?)。

4.3 SMU_stdby Internal Alarms

SMU_stdby产生的Alarm说明如下:

4.4 Alarm 处理方式

4.4.1 Alarm协议

每个安全机制都应使用预定义的协议与smu_stdby连接。该协议允许以可靠的方式跨时钟域。协议的运行对软件层没有影响。

4.4.2 Alarm配置

在接收到警报事件后,SMU_stdby对要执行的操作进行解码。可以不响应或设置FSP[1…0]引脚为高阻抗。每条Alarm都可以配置这两种行为。

FSP的外部行为设置[1…0](高阻抗状态)通过:AG2iFSP_STDBY (i=0)和AG2iFSP_STDBY (i=1)寄存器进行配置。

注意:为了识别ErrorPins的高阻抗状态为故障状态,可能需要一个外部下拉设备。

注意:当SMU_stdby响应Alarm,将FSP[0]或/和FSP[1]置为高阻抗状态时,如果各自的ErrorPin上没有外部下拉设备连接,则STS.FSP[0]或/和STS.FSP[1]置为1。

813

813

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?