一.FSM理论基础

- 前期文章详细叙述了FSM,有需要的同学请访问链接:点击次数访问链接https://blog.csdn.net/weixin_42455055/article/details/119118162

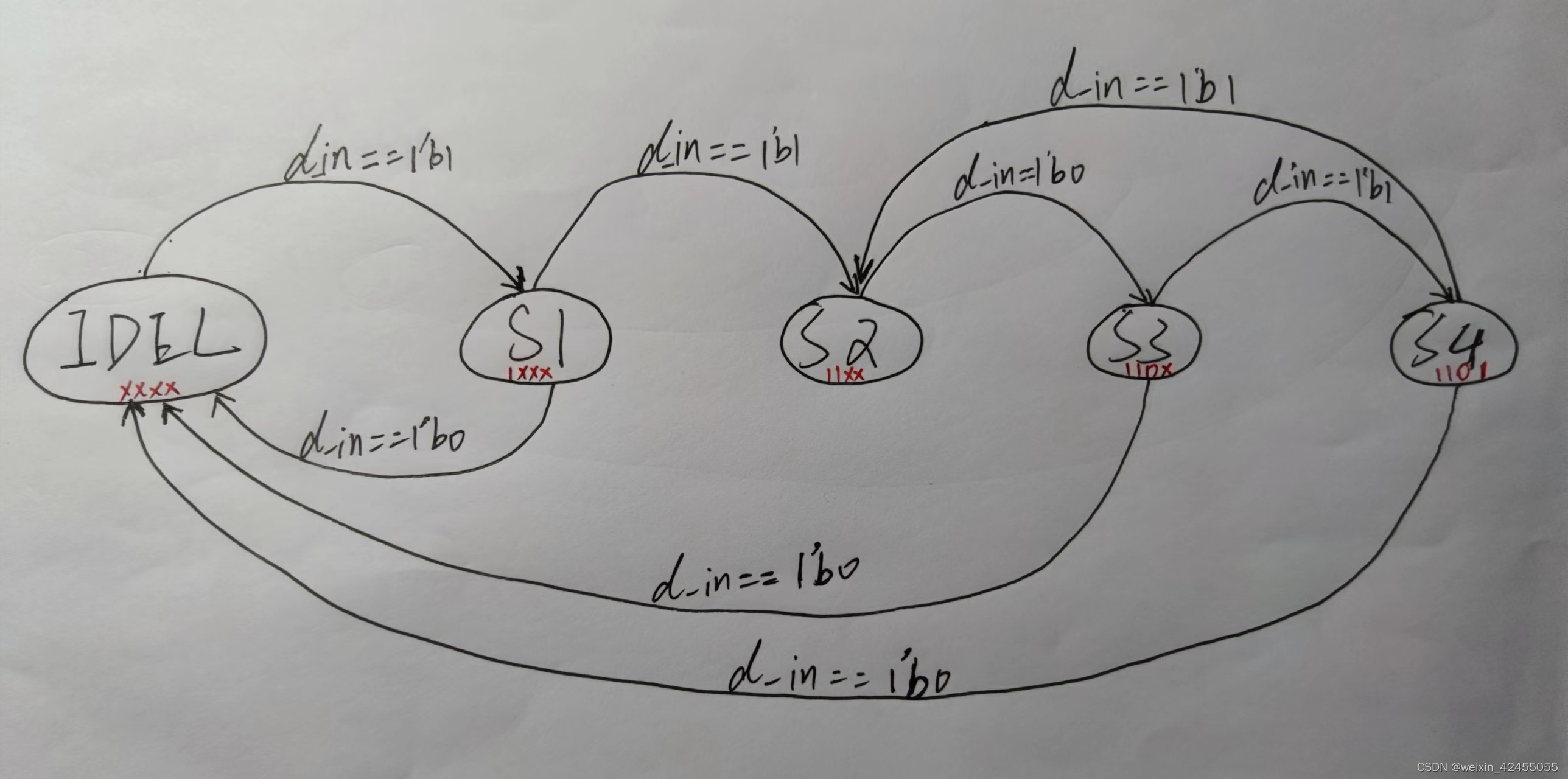

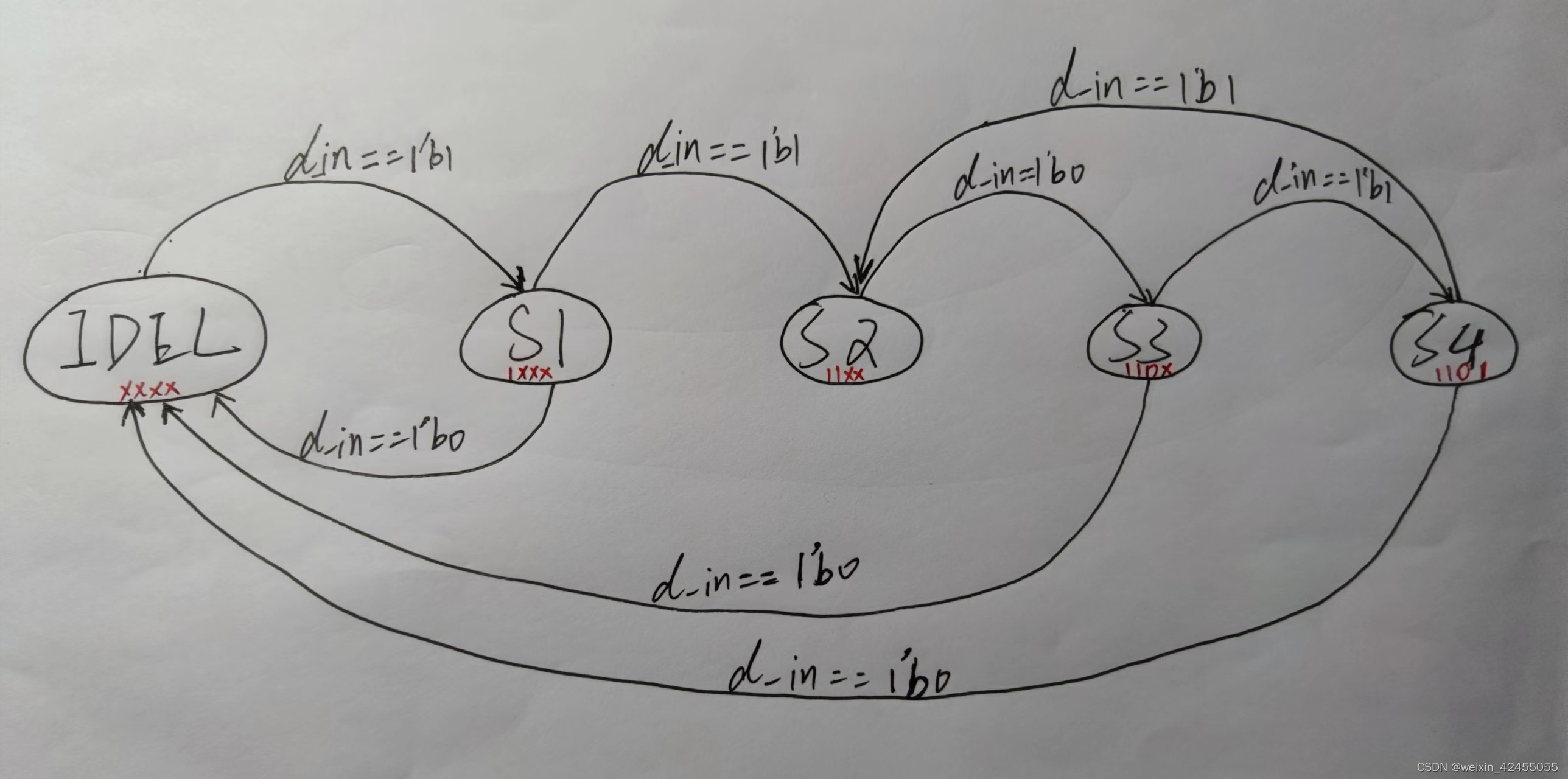

二.连续序列1101检测案例

2.1 需求分析

2.2 Verilog实现

module FSM_1101(

input clk,

input rst_n,

input FSM_1101_in,

output reg Match_Flag

);

reg [2:0] next_state;

reg [2:0] state;

localparam

IDEL = 3'b000,

NUM_1xxx = 3'b001,

NUM_11xx = 3'b011,

NUM_110x = 3'b010,

NUM_1101 = 3'b110;

always@( posedge clk or negedge rst_n ) begin

if( !rst_n )

next_state <= IDEL;

else

next_state <= state;

end

always@(*) begin

case(next_state)

IDEL: begin

if( FSM_1101_in == 1'b1 )

state <= NUM_1xxx;

else

state <= IDEL;

end

NUM_1xxx:begin

if( FSM_1101_in == 1'b1 )

state <= NUM_11xx;

else

state <= IDEL;

end

NUM_11xx:begin

if( FSM_1101_in == 1'b0 )

state <= NUM_110x;

else

state <= NUM_11xx;

end

NUM_110x:begin

if( FSM_1101_in == 1'b1 )

state <= NUM_1101;

else

state <= IDEL;

end

NUM_1101:begin

if( FSM_1101_in == 1'b1 )

state <= NUM_11xx;

else

state <= IDEL;

end

default:state <= IDEL;

endcase

end

always@( posedge clk or negedge rst_n ) begin

if( !rst_n )

Match_Flag <= 0;

else if( next_state == NUM_1101 )

Match_Flag <= 1'b1;

else

Match_Flag <= 1'b0;

end

endmodule

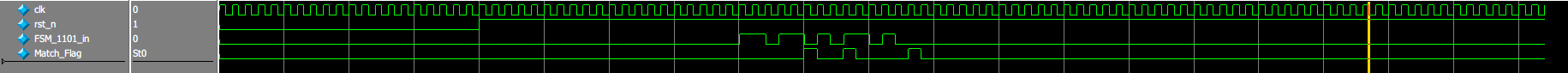

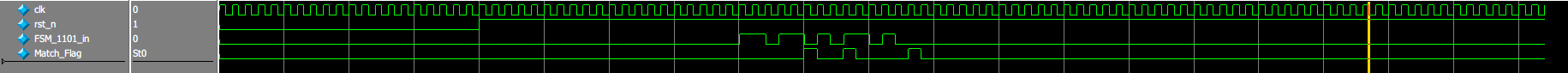

2.3 仿真验证

`timescale 1ns/1ns

`define clock_period 20

module FSM_1101_tb();

reg clk;

reg rst_n;

reg FSM_1101_in;

wire Match_Flag;

FSM_1101 FSM_1101

(

.clk(clk),

.rst_n(rst_n),

.FSM_1101_in(FSM_1101_in),

.Match_Flag(Match_Flag)

);

initial

begin

clk = 1;

rst_n = 0;

FSM_1101_in = 0;

end

always#(`clock_period/2) clk = ~clk;

initial begin

#( `clock_period*20 );

rst_n = 1;

#( `clock_period*20 + 1'b1 );

FSM_1101_in = 1;

#( `clock_period );

FSM_1101_in = 1;

#( `clock_period );

FSM_1101_in = 0;

#( `clock_period );

FSM_1101_in = 1;

#( `clock_period );

FSM_1101_in = 1;

#( `clock_period );

FSM_1101_in = 0;

#( `clock_period );

FSM_1101_in = 1;

#( `clock_period );

FSM_1101_in = 0;

#( `clock_period );

FSM_1101_in = 1;

#( `clock_period );

FSM_1101_in = 1;

#( `clock_period );

FSM_1101_in = 0;

#( `clock_period );

FSM_1101_in = 1;

#( `clock_period );

FSM_1101_in = 0;

#( `clock_period*50 );

$stop;

end

endmodule

仿真结果如下所示,输出正确:

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?