欢迎FPGA工程师加入官方微信技术群

最近在做项目的过程中遇到了一个排序问题,需要对4096个正值数据进行排序。由于使用的Xilinx的Kintex系列FPGA,逻辑资源较为丰富,所以希望能利用逻辑资源尽量加速排序算法。但是自己对排序算法了解不多,所以目前根据网上的资料,选择了堆排序实现排序算法。参考资料如下

目前我实现的堆排序算法并没有很好的利用FPGA的并行特性,更多的还是利用FSM进行循环计算。希望可以借本文抛砖引玉,得到大神的指点,介绍给我一个可以利用FPGA并行计算特性实现大量数据快速排序的FPGA算法。大家要是有什么想法或者建议一定要给我留言,拜托拜托。

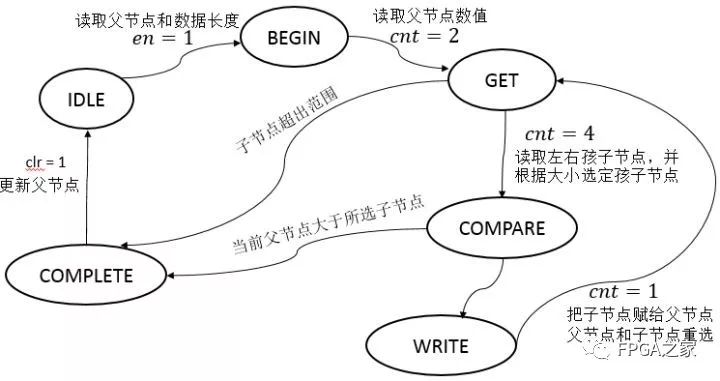

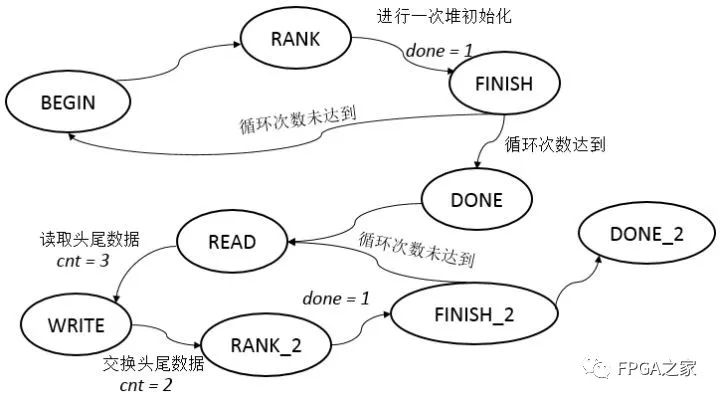

堆排序算法原理不再介绍,排序六 堆排序 - 静默虚空 - 博客园这篇博客介绍的非常详细。这里补充一下:算法的思想是将RAM看做一个堆,RAM的地址就对应堆的各个节点,通过对RAM的读写就可以实现对堆节点的交换、比较,排序结束后RAM内的数据就会按顺序排好。我将堆排序算法分为两个模块:堆初始化模块和上层控制模块,根据堆排序的具体算法可以得到状态机具体内容如下:

这里状态机均由三段式状态机实现,Verilog代码如下(请看明白原理再拿走代码,不然我这篇文章就没有意义了)

堆初始化模块:

`timescale 1ns / 1ps

module initial_stack

#(

parameter addr_width = 5,

parameter data_width = 8

)

(

input clk,

input rst_n,

input en,

input clr,

output reg done,

input [addr_width - 1:0] parent,

input [addr_width - 1:0] length,

output reg wea,

output reg [ addr_width - 1:0 ] addra,

output reg [ data_width - 1:0 ] data_we,

input [ data_width - 1:0 ] data_re

);

reg [data_width - 1:0] temp;

reg [addr_width :0] parent_r;//attention: For recognize the parent, we must expand data width of it

reg [addr_width :0] child_r;

reg [addr_width :0] length_r;

parameter IDLE = 6'b000001;

parameter BEGIN = 6'b000010;

parameter GET = 6'b000100;

parameter COMPARE = 6'b001000;

parameter WRITE = 6'b010000;

parameter COMPLETE= 6'b100000;

reg [5:0] state;

reg [5:0] next_state;

reg [7:0] cnt;

reg [data_width - 1:0] child_compare;

always@(posedge clk or negedge rst_n)

begin

if(!rst_n) begin state <= IDLE; end

else begin state <= next_state; end

end

always@(*)

begin

case(state)

IDLE: begin

if(en) begin next_state = BEGIN; end

else begin next_state = IDLE; end

end

BEGIN:begin

if(cnt == 8'd2) begin next_state = GET; end

else begin next_state = BEGIN; end

end

GET: begin

if(child_r >= length_r) begin next_state = COMPLETE; end

else if(cnt == 8'd4) begin next_state = COMPARE; end

else begin next_state = GET; end

end

COMPARE: begin

if(temp >= child_compare) begi

欢迎FPGA工程师加入官方微信技术群最近在做项目的过程中遇到了一个排序问题,需要对4096个正值数据进行排序。由于使用的Xilinx的Kintex系列FPGA,逻辑资源较为丰富,所以希望能利用逻辑资源尽量加速排序算法。但是自己对排序算法了解不多,所以目前根据网上的资料,选择了堆排序实现排序算法。参考资料如下目前我实现的堆排序算法并没有很好的利用FPGA的并行特性,更多的还是利用FSM进行...

欢迎FPGA工程师加入官方微信技术群最近在做项目的过程中遇到了一个排序问题,需要对4096个正值数据进行排序。由于使用的Xilinx的Kintex系列FPGA,逻辑资源较为丰富,所以希望能利用逻辑资源尽量加速排序算法。但是自己对排序算法了解不多,所以目前根据网上的资料,选择了堆排序实现排序算法。参考资料如下目前我实现的堆排序算法并没有很好的利用FPGA的并行特性,更多的还是利用FSM进行...

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

725

725

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?