1、MAC内核简介

(1)STM32的MAC内核是一个以太网MAC控制器,用于实现以太网通信。它符合IEEE802.3标准,支持10/100Mbit/s的数据传输速率,并提供了地址和媒体访问控制方式。

(2)MAC相关原理学习的资料:STM32F4/F7/H7xx中文参考手册的以太网(ETH)部分

(3)MAC内核的特性:

- 传输速率:支持外部PHY接口实现10/100Mbit/s数据传输速率

- 协议标准:符合IEEE802.3/3u的 MII 和 RMII 接口与快速以太网PHY通信

- 工作模式:支持全双工和半双工操作

- 站管理接口:支持通过MDIO接口配置和管理PHY设备

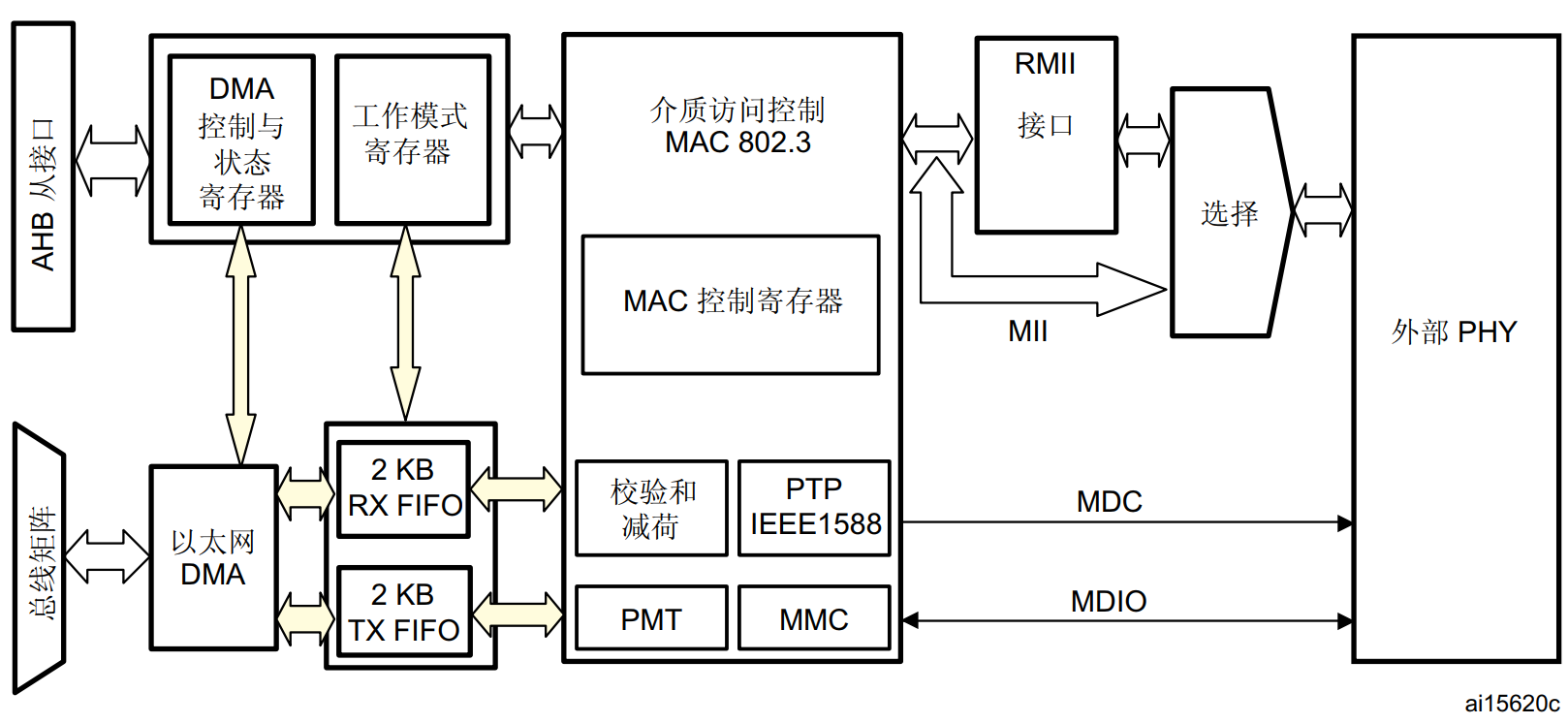

2、ST的以太网框架

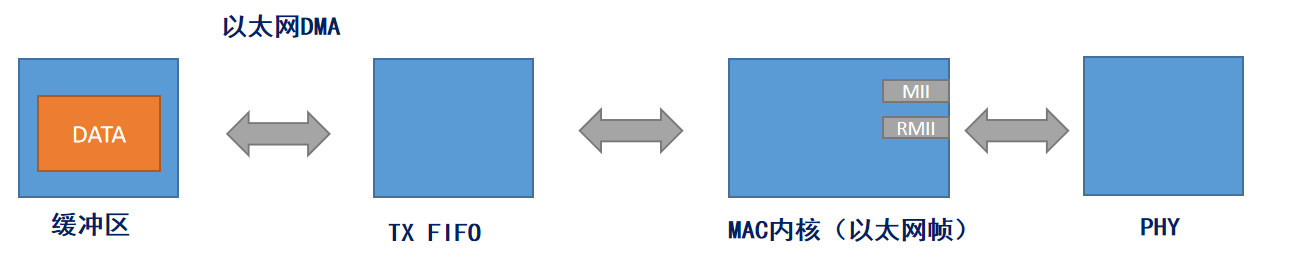

(1)MAC 内核作为数据链路层设备,负责与物理层接口(如以太网 PHY)进行通信,并提供了对数据包的 封装解析、发送接收 等操作的支持。

- MAC内核以太网帧发送时,给数据加上一些控制信息;以太网帧接收时,去掉控制信息。

- PHY交互接口

- 数据通道:介质接口RMII/MII

- 管理通道:SMI站管理接口(MDC和MDIO)

3、介质接口

(1)RMII 与 MII 是 MAC 内核(数据链路层)与 PHY 芯片(物理层)的数据交互通道,用来传输以太网数据。

(2)支持10/100Mbit/s数据传输模式。

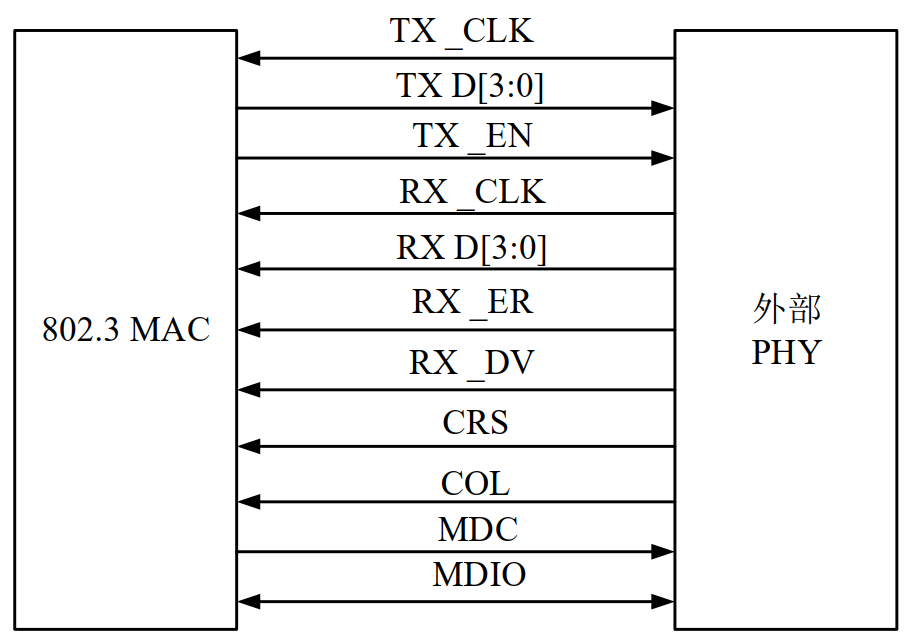

3.1、MII接口

(1)介质独立接口(MII)是一个媒体独立接口,也称为媒体接口。它是 IEEE-802.3 定义的以太网行业标准。

(2)MII 包括一个数据接口,以及一个 MAC 和 PHY 之间的管理接口。

- 数据接口包括分别用于发送器和接收器的两条独立信道,每条信道都有自己的数据、时钟和控制信号。MII 数据接口总共需要 15 个信号。

- 管理接口是个双信号接口:一个是时钟信号,另一个是数据信号。通过管理接口,上层能监视和控制 PHY。

(3)下图为 MCU 通过 MII 接口与 PHY 芯片的连接图。

从上图描述中可以明确地了解到, MII 介质接口使用的引脚数量是非常多的,这也反映出引脚紧缺的 MCU 不适合使用 MII 介质接口来实现以太网数据传输。 MII 接口引脚的作用如下:

- MII_TX_CLK:连续时钟信号。该信号提供进行 TX 数据传输时的参考时序。标称频率为:速率为 10 Mbit/s 时为 2.5 MHz;速率为 100 Mbit/s 时为 25 MHz。

- MII_RX_CLK:连续时钟信号。该信号提供进行 RX 数据传输时的参考时序。标称频率为:速率为 10 Mbit/s 时为 2.5 MHz;速率为 100 Mbit/s 时为 25 MHz。

- MII_TX_EN:发送使能信号。

- MII_TXD[3:0]:数据发送信号。该信号是 4 个一组的数据信号。

- MII_CRS:载波侦听信号。

- MII_COL:冲突检测信号。

- MII_RXD[3:0]:数据接收信号。该信号是 4 个一组的数据信号。

- MII_RX_DV:接收数据有效信号。

- MII_RX_ER:接收错误信号。该信号必须保持一个或多个周期(MII_RX_CLK),从而向 MAC 子层指示在帧的某处检测到错误。

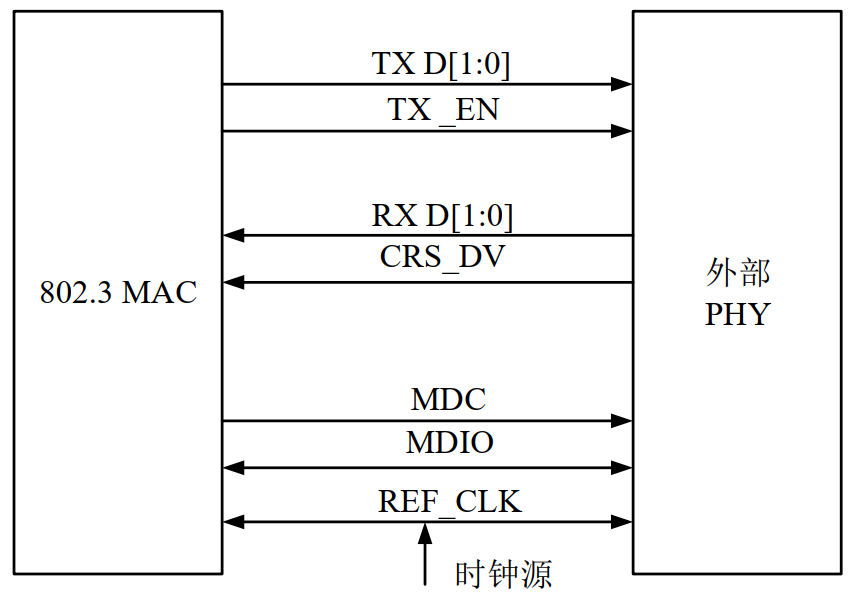

3.2、RMII接口

(1)简化媒体独立接口( RMII)是一种标准的以太网接口之一,比 MII 有更少的 I/O 传输。RMII 口通常只用两根线来传输数据,而 MII 口需要用四根线。(两者的位宽不同)

(2)对于 10M 线速, RMII 的速率是 5M,而 MII 的速率是 2.5M;对于 100M 线速, RMII 的速率是 50M,而 MII 的速率是 25M。

(3)下图为 MCU 通过 RMII 接口与 PHY 芯片的连接图。

(4)从上图描述中可以明确地了解到, REF_CLK 引脚负责提供 50MHz 的时钟频率。这个时钟信号对 MAC 内核和 PHY 芯片都至关重要,确保它们之间的时钟同步,从而保证数据传输的准确性和稳定性。

152

152

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?