当机芯在低温下输出图像异常,且判断原因为FPGA布局布线局限性时,区域约束并不总是奏效,因此考虑时序约束。

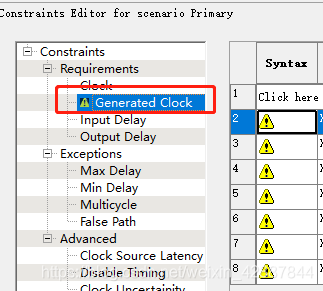

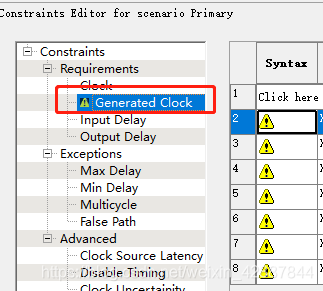

双击“timing constraints”,在新窗口中发现有警告项目,双击它,则右边显示出所有风险项目。逐个添加约束。

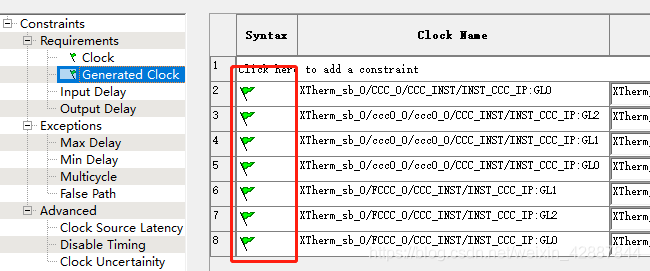

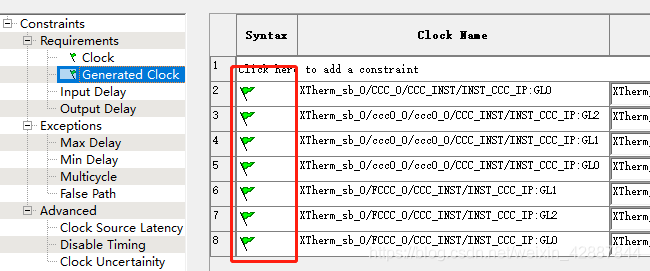

注意这些时钟的参考时钟也需要被约束,约束成功之后如下:

通过区域约束可以使得模块尽可能与管脚靠近,时域约束可以是时钟尽可能准确。但实际效果并不总是如意。

当机芯在低温下输出图像异常,且判断原因为FPGA布局布线局限性时,区域约束并不总是奏效,因此考虑时序约束。

双击“timing constraints”,在新窗口中发现有警告项目,双击它,则右边显示出所有风险项目。逐个添加约束。

注意这些时钟的参考时钟也需要被约束,约束成功之后如下:

通过区域约束可以使得模块尽可能与管脚靠近,时域约束可以是时钟尽可能准确。但实际效果并不总是如意。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?