4.1 存储系统层次结构

1.基本存储体系

- 输入设备将程序与数据写入主存;

- CPU取指令;

- CPU执行指令期间读数据;

- CPU写回运算结果;

- 输出设备输出结果;

2.主存速度慢的原因

- 主存增速与CPU不同步;

- 指令执行期间多次访问存储器;

3.主存容量不足的原因

- 存在制约主板容量的技术因素 由CPU、主板等相关技术指标确定

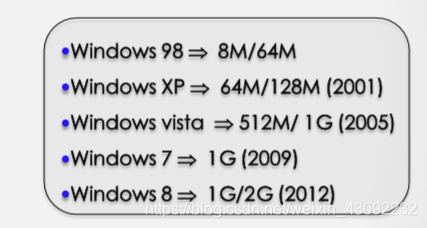

- 应用对主存的需求不断扩大

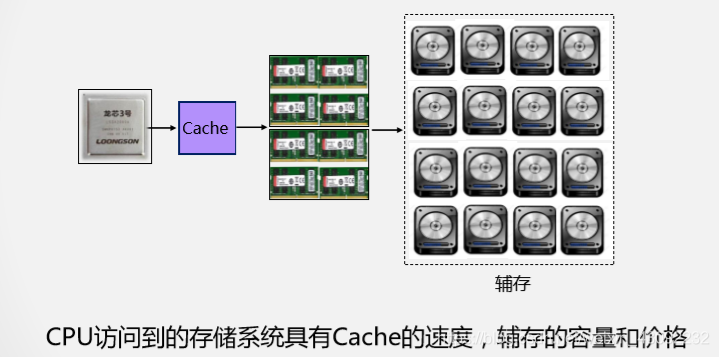

4.存储体系的层次化结构

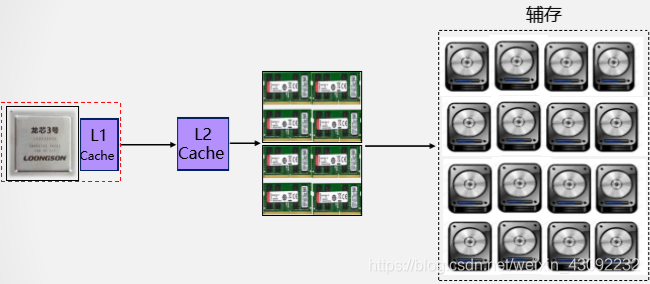

- L1 Cache集成在CPU中,分数据Cache(D-Cache)和指令Cache(I-Cache)

- 早期L2 Cache在主板上或与CPU集成在同一电路板上。随着工艺的提高L2 Cache被集成在CPU内核中,不分D-Cache和I-Cache

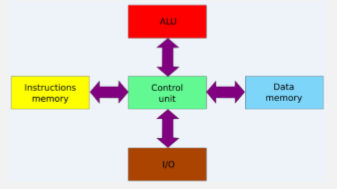

哈佛结构(Harvard architecture)

- 是一种将指令储存和数据储存分开的存储器结构,可支持:数据和指令并行储存、指令预期,提高处理器的执行效率;另外,指令和数据可有不同的数据宽度,如Microchip公司的PIC16芯片的程序指令是14位宽度,而数据是8位宽度。

- 目前使用哈佛结构的:PIC系列、摩托罗拉公司的MC68系列、Zilog公司的Z8系列、ATMEL公司的AVR系列和ARM公司的ARM9、ARM10和ARM11。

5.存储体系层次化结构的理论基础

局部性原理

时间局部性

- 现在被访问的信息2在不久的将来还将再次被访问

- 时间局部性的程序结构体现:循环结构

空间局部性

- 现访问信息2,下一次访问2附近的信息

- 空间局部性的程序结构体现:顺序结构

4.2 主存中的数据组织

1.存储字长

- 主存的一个存储单元所包含的二进制位数;

- 目前大多数计算机的主存按字节编址,存储字长也不断加大,如16位字长、32位字长和64位字长;

2.数据存储和边界的关系

- 按边界对齐的数据存储

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

3543

3543

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?