数据存储与边界的关系:

-

按边界对齐的数据存储,未按边界对齐的数据存储

-

边界对齐与存储地址的关系:(32位为例)

-

双字长边界对齐:起始地址最末三位为000(8字节整数倍)

-

单字长边界对齐:起始地址最末二位为00(4字节整数倍)

-

半字长边界对齐:起始地址最末一位为0(2字节整数倍)

大端与小端存储方式:

-

大端:最高字节地址是数据地址(0123存成0123)

-

小端:最低字节地址是数据地址(0123存成3210)

3. 存储器分类

-

SRAM存储器:存取速度快,但集成度低,功耗大,做缓存

-

DRAM存储器:存取速度慢,但集成度高,功耗低,做主存

DRAM刷新方式:集中刷新、分散刷新、异步刷新

4. 主存容量的扩展

-

位扩展法:8K * 8位 --> 8K * 32位

-

字扩展法:8K * 8位 --> 32K * 8位

-

字位同时扩展法:8K * 8位 --> 32K * 32位

5. Cache的基本原理

-

cache的工作过程

-

数据:cpu与cache交换字,cache与内存交换块

-

读:命中,不命中

-

写:写穿策略,写回策略

-

写策略

-

写穿策略(write through):同时写缓存和内存,好像穿过缓存一样。若不命中,先写到主存中,并选择性地同时分配到缓存中(写分配/非写分配)

-

写回策略(write back):写到缓存后不管了,只有当缓存的内容替换回主存时再管,需有脏位。好像隔段时间后再写回到主存中一样

-

地址映射机制

-

相联存储器:地址本身包含着位置啊可比较的信息啊等内容信息,可根据区分地址内容进行寻址

-

主存地址 = 块地址 + 块内偏移地址 = (Tag + Index) + 块内偏移地址

-

cache结构

-

好多行,每行与主存块大小相等

-

每行 = tag + data + valid + dirty

-

三种映射方式

-

**全相联:**cache行号 = random(内存块号)

-

**直接相联:**cache行号 = 内存块号 % cache行数

-

**组相联:**两者结合。8行1路组相联就是全相联,8行8路组相联就是直接相联

-

替换算法

-

先进先出法-FIFO

-

最近最不经常使用法-LFU

-

近期最少使用法-LRU

-

随机替换法

6. 虚拟存储器

-

解决问题:主存容量不足。希望向程序员提供更大(比主存大)的编程空间

-

分类:页式,段式,段页式

-

页式实现方式:MMU(Memory Management Unit) + 页表 + TLB(Transaction Lookaside Buffer:地址转换后备缓冲器)

-

页式转换过程:虚拟地址 = 虚拟页号 + 页内偏移 ==> 物理页号 + 页内偏移

7. RAID

-

- 概念:独立磁盘构成的具有冗余能力的阵列(Redundant Arrays Independent Disks)

-

核心技术:使用异或运算恢复数据 (x⊕y = z --> x = y⊕z)

-

分类:

-

RAID0:条带均匀分布

| 磁盘0 | 磁盘1 | 磁盘2 | 磁盘3 |

| D0 | D1 | D2 | D3 |

| D4 | D5 | D6 | D7 |

| D8 | D9 | D10 | D11 |

- RAID1:以镜像为冗余方式

| 磁盘0 | 磁盘1 |

| D0 | D0 |

| D1 | D1 |

| D2 | D2 |

- RAID3/4:有校验盘

| 磁盘0 | 磁盘1 | 磁盘2 | 校验磁盘 |

| D0 | D1 | D2 | P0 |

| D3 | D4 | D5 | P1 |

| D6 | D7 | D8 | P2 |

- RAID5:校验信息分布式

| 磁盘0 | 磁盘1 | 磁盘2 | 磁盘3 |

| D0 | D1 | D2 | P0 |

| D3 | D4 | P1 | P5 |

| D6 | P2 | D7 | D8 |

| P3 | D9 | D10 | D11 |

-

RAID10/01:10是先镜像再条带化,01是先条带化再镜像

-

RAID50:先RAID5,再条带化

五、指令系统

1. 指令系统基本概念

-

指令集:一台机器所有指令的集合。系列机(同一公司不同时期生产);兼容机(不同公司生产)

-

指令字长:指令中包含的二进制位数,有等长指令、变长指令。

-

指令分类

-

根据层次结构:高级、汇编、机器、微指令

-

根据地址码字段个数:零、一、二、三地址指令

-

根据操作数物理位置

-

存储器-存储器(SS)

-

寄存器-寄存器(RR)

-

寄存器-存储器(RS)

-

根据指令功能:传送、算术运算、位运算、控制转移

-

指令格式:操作码+数据源+寻址方式

2. 寻址方式

-

**指令寻址方式:**顺序寻址,跳跃寻址

-

操作数寻址方式:

-

立即数寻址:地址码字段是操作数本身 MOV AX, 200H

-

寄存器寻址:地址码字段是寄存器地址 MOV AX, BX

-

直接寻址:地址码字段是内存地址 MOV AX, [200H]

-

间接寻址:地址码字段是内存地址的地址 MOV AX, I[200H]

-

寄存器间接寻址:地址码字段是存内存地址的寄存器地址 MOV AX, [BX]

-

相对寻址:操作数地址 + 当前PC的值

-

基址寻址:操作数地址 + 基址寄存器的值(一段程序中不变) MOV AX, 32[B]

-

变址寻址:操作数地址 + 变址寄存器的值(随程序不断变化) MOV AX, 32[SI]

3. MIPS

-

三种指令格式

-

R型指令:

| 6bits | 5bits | 5bits | 5bits | 5bits | 6bits |

| 000000 | Rs | Rt | Rd | shamt | funct |

- I型指令:

| 6bits | 5bits | 5bits | 16bits |

| OP | Rs | Rt | 立即数 |

- J型指令:

| 6bits | 26bits |

| OP | 立即数 |

六、中央处理器

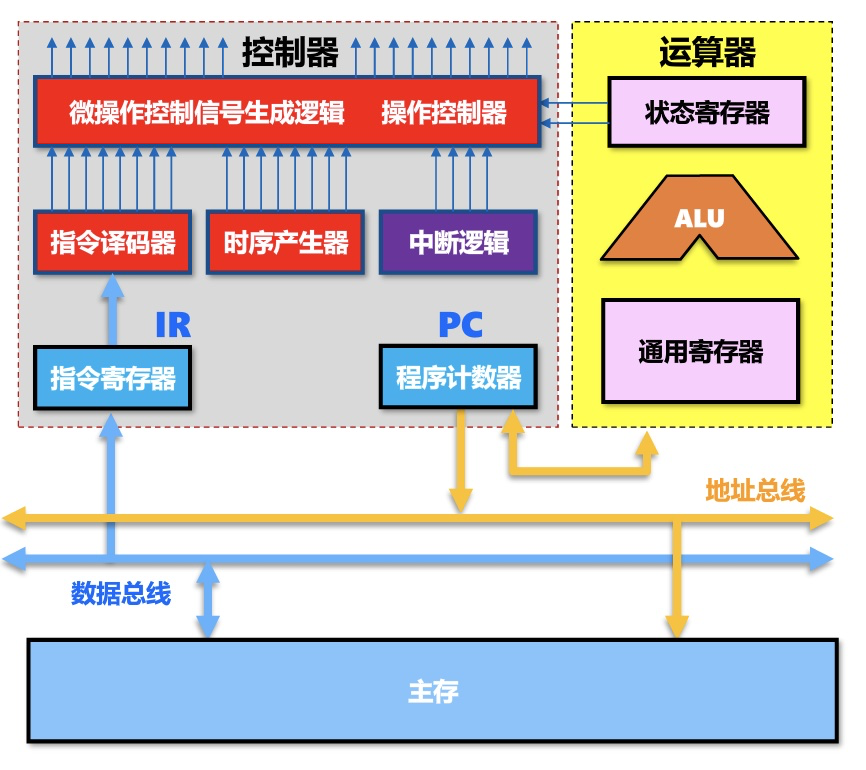

1. CPU的组成与功能

2. 数据通路

-

概念:执行部件间传送信息的路径,分共享通路(总线)和专用通路

-

抽象模型:时钟驱动下,A --> 组合逻辑 --> B

-

D触发器定时模型:

-

时钟触发前要稳定一段时间:建立时间(Setup Time)

-

时钟触发后要稳定一段时间:保持时间(Hold Time)

-

时钟触发到输出稳定的时间:触发器延迟(Clk_to_Q)

-

与时钟周期的关系:

-

时钟周期 > Clk_to_Q + 关键路径时延 + Setup Time

-

Clk_to_Q + 最短路径时延 > Hold Time

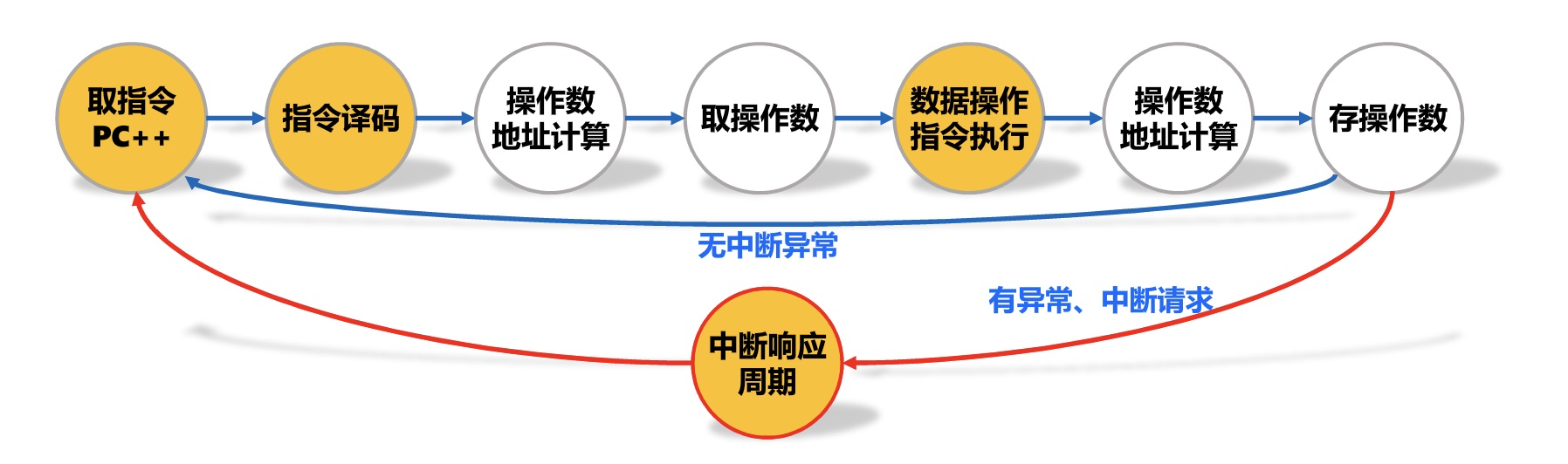

3. 指令周期

- 指令执行的一般流程

-

基本概念

-

时钟周期 = 节拍脉冲 = 震荡周期

-

机器周期 = CPU周期 = 从主存读取一条指令的最短时间

-

指令周期 = 从主存读指令并执行指令的时间

- 指令时间控制:

| 机器周期数 | 节拍数 | 同步方式 | 实践 | |

| 定长指令周期 | 不变 | 不变 | 按机器周期 | mips单周期 |

| 变长指令周期 | 变 | 变 | 按时钟周期 | mips多周期 |

4. CPU设计

略,详情请参见《自制CPU系列》

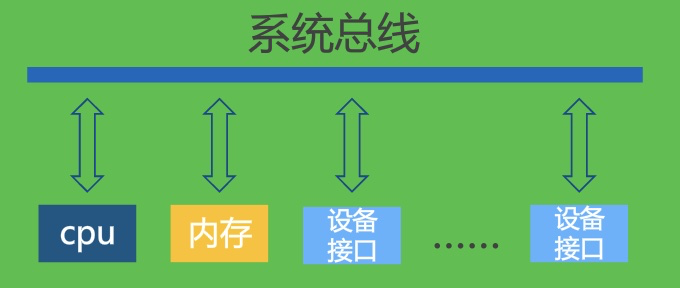

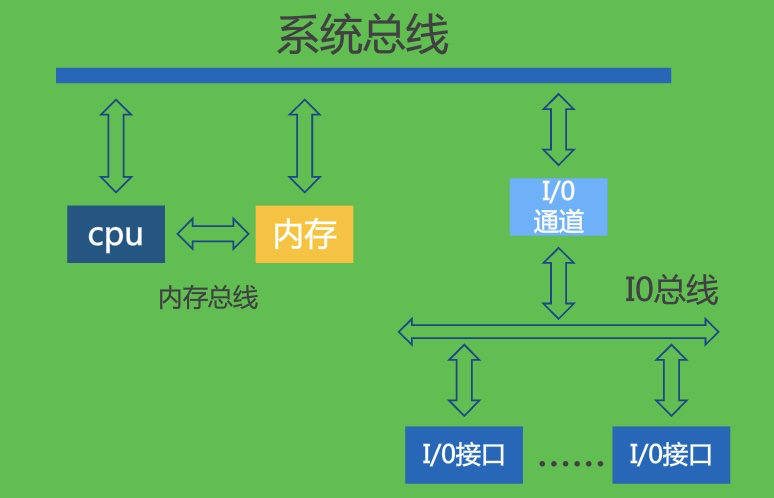

七、总线

1. 系统总线的特性及应用

-

总线概念:将计算机系统中各部件连接起来

-

总线分类:(外部/内部,系统/非系统,串行/并行,同步/异步…)

-

按用途分类:

-

存储总线:cpu与存储器

-

系统总线:连接存储总线和IO总线的中间总线

-

IO总线:连接外部设备

-

按位置分类:

-

外部总线:USB,火线(IEEE1394)

-

内部总线:PCI(连网卡),AGB(连显卡)

-

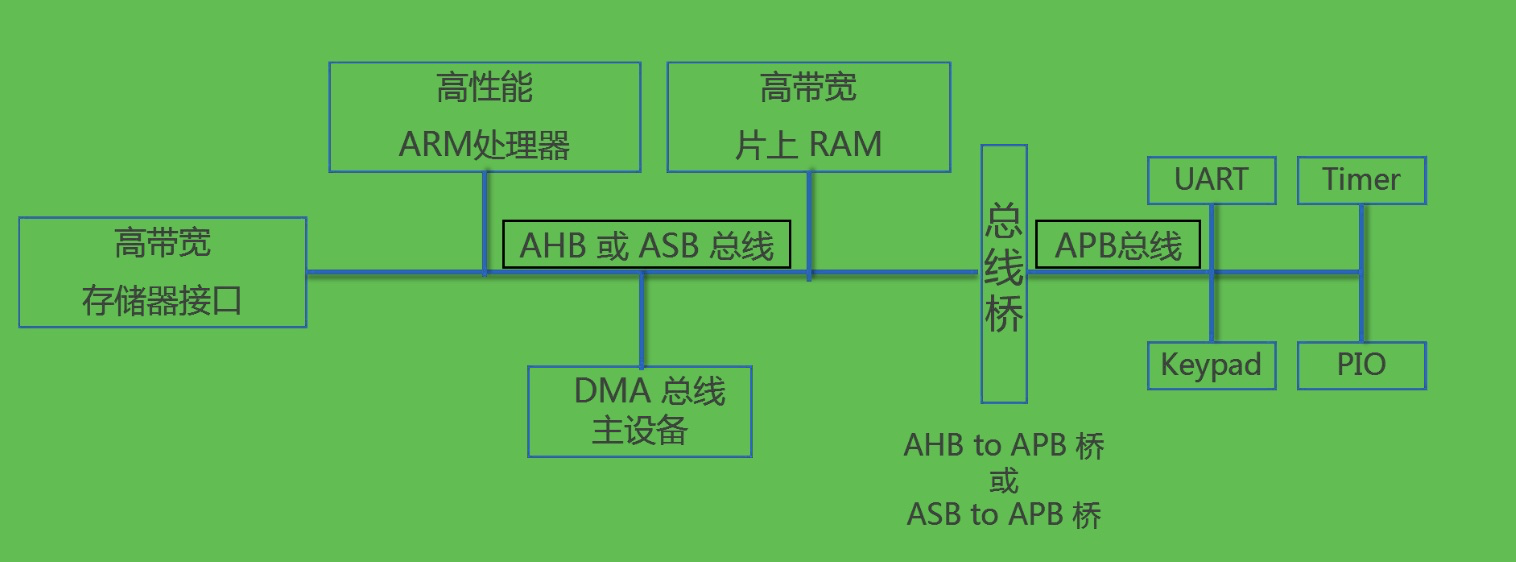

(芯)片内总线:AMBA(ARM处理器)

-

按组成分类

-

数据总线:传数据,双向三态

-

地址总线:传地址,单向三态

-

控制总线:控制信号和时序信号

-

电源线和地线:略

2. 总线性能和总线事物

-

总线的性能参数

-

总线频率:总线工作速率f,单位是MHz

-

总线宽度:数据总线的宽度w,单位是bit

-

总线传输速率:总线传输数据量BW,单位是MB/s。BW = w / 8 * f

-

总线事务

-

概念:从请求总线到完成使用的操作序列(请求 - 裁决 - 地址传输 - 数据传输 - 总线释放)

-

角色:主设备(CPU,DMA)和从设备

-

四个阶段:请求与仲裁 - 传输 - 寻址 - 结束

-

常见总线操作:读,写,读修改写,写后读,块操作

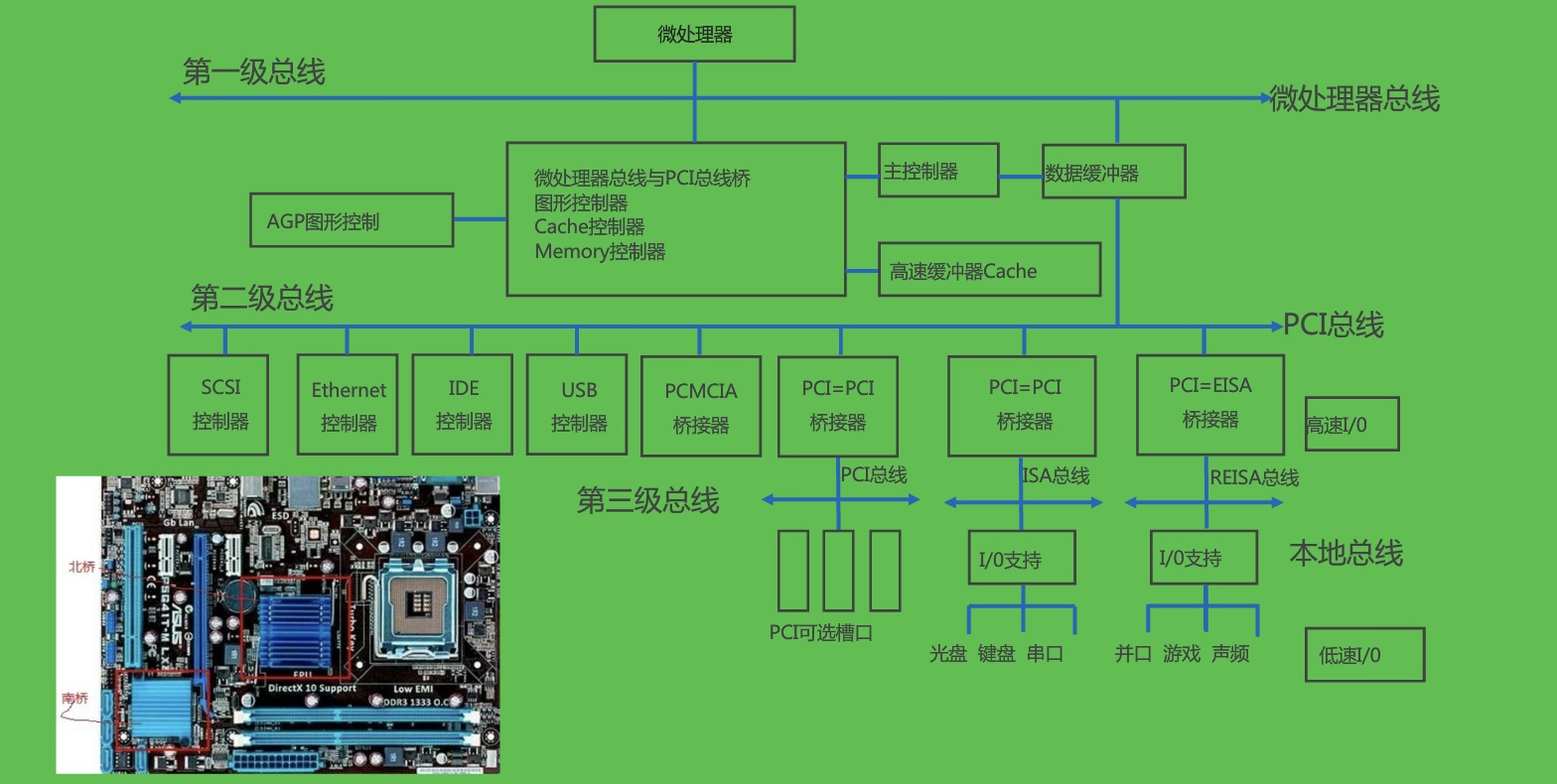

3. 总线连接方式

- 单总线结构

- 双总线结构

- 多总线结构

-

总线桥:不同速率总线之间的连接,起速度缓冲、电平转换、控制协议转换的作用

-

多级总线结构(南北桥)

-

- 单总线结构

- 总线结构对系统性能的影响

| 多总线 | 单总线 | |

| 对最大存储容量 | 不影响 | 因要与io共享内存,影响 |

| 对指令系统 | 增加IO指令 | 无IO指令 |

| 对吞吐量 | 大 | 小 |

4. 总线仲裁和数据传输方式

-

菊花链式串行总线仲裁:简单,只要有一个主设备占用总线,其他就占不了

-

集中式并行总线仲裁:

-

固定优先级策略:优先级高的主设备,总会优先控制总线权

-

轮叫式策略:皇帝轮流做

-

LRG策略:最近获得控制权的,再获得控制权的优先级高(经常用的就更容易获得总线控制权)

5. 总线标准

-

- 概念:计算机各部件之间利用总线传输信息应遵守的协议和规范,包括硬件和软件两部分

-

常见的总线标准

-

机箱内部总线:

-

ISA - EISA - VESA

-

ISA(Industrial Standard Architecture):最早指定的总线技术标准,总线宽度8/16位,频率5-8MHz,带宽5-8MB/s

-

EISA:宽度变成32位

-

VESA:宽度变成64位

-

PCI(PCIe) - AGP

-

主要用于系统总线和IO总线,取代ISA

-

地址总线和数据总线分时复用,支持即插即用(自动寻找驱动程序)

-

32/64位,133/264MB/s

-

机箱外部总线:

-

USB等…

八、输入输出系统

1. 输入输出系统概述

-

组成:外设、接口、总线、管理软件

-

基本功能

-

完成计算机内外的信息传递

-

保证CPU正确选择输出设备

-

利用缓冲等,实现主机与外设的速度匹配

-

**特点:**异步性、实时性、设备无关性

-

**输入过程:**CPU把地址值放入总线 --> CPU等候设备数据有效 --> CPU从总线读入数据存入寄存器

-

**输出过程:**CPU把地址值放入总线 --> CPU把数据值放入总线 --> 设备等数据有效取走数据

-

IO系统性能:存储IO、通信IO

-

连接特性:哪些设备可以和IO相连

-

IO系统容量:IO系统可以容纳的设备数

-

响应时间:从用户输入命令到得到结果所花的时间(s)

-

吞吐率:单位时间完成的IO操作次数(用IOP表示)

2. 输入输出方式

-

无条件IO方式:执行IO指令时,CPU默认外设已经准备就绪,外设很难满足这一点

-

程序控制IO方式:执行IO指令时,先获取设备状态(设备状态寄存器),决定下一步操作(程序决定)

-

数据要经过CPU,CPU还要浪费大量时间查询设备状态

-

中断IO方式:外设主动通知CPU接收或输出数据,有实时性

-

DMA方式:由硬件执行IO,外设准备好后通知DMA,DMA接管总线,完成数据交换

-

既有中断的优点,又降低了服务的开销

-

通道和IO处理机方式:外设种类很多速度差别很大,将外设管理工作从CPU总分离出来

-

通道本身就是个简单的CPU,执行IO指令的处理机

-

IO处理机是通道的进一步发展,更像一个CPU了

3. 中断请求与响应

-

概念:CPU由内部外部事件引起CPU中断正在运行的程序,具有随机性(符合输入输出系统特性)

-

作用:主机与外设并行;故障处理;实时处理

-

类型:

-

内部中断(软件、异常)

-

外部中断(可屏蔽中断INTR、不可屏蔽中断NMI)

-

基本功能:

-

中断信号的保持与清除:通过寄存器存起来,处理完清零

-

中断优先级:硬件响应优先序、软件服务优先序(中断服务程序开头,设置自己的中断屏蔽位)

-

中断源识别:系统分配给每个中断源的代号(中断号),中断号获取可以用硬件或软件方式

-

中断处理:

-

响应:每执行完一条指令,就会判断是否有中断请求

-

处理:保存断点(返回地址)、执行中断程序、返回断点

-

中断控制:

-

中断触发方式:指外设以什么逻辑信号去申请中断(边沿触发、电平触发)

-

中断排队方式:按优先级、循环轮流排队

-

中断嵌套:中断正在执行的中断程序,不可屏蔽中断不能嵌套

-

中断屏蔽:处理器内部有个触发器,“1”时才会响应外部中断

最后

给大家送一个小福利

附高清脑图,高清知识点讲解教程,以及一些面试真题及答案解析。送给需要的提升技术、准备面试跳槽、自身职业规划迷茫的朋友们。

-

外部中断(可屏蔽中断INTR、不可屏蔽中断NMI)

-

基本功能:

-

中断信号的保持与清除:通过寄存器存起来,处理完清零

-

中断优先级:硬件响应优先序、软件服务优先序(中断服务程序开头,设置自己的中断屏蔽位)

-

中断源识别:系统分配给每个中断源的代号(中断号),中断号获取可以用硬件或软件方式

-

中断处理:

-

响应:每执行完一条指令,就会判断是否有中断请求

-

处理:保存断点(返回地址)、执行中断程序、返回断点

-

中断控制:

-

中断触发方式:指外设以什么逻辑信号去申请中断(边沿触发、电平触发)

-

中断排队方式:按优先级、循环轮流排队

-

中断嵌套:中断正在执行的中断程序,不可屏蔽中断不能嵌套

-

中断屏蔽:处理器内部有个触发器,“1”时才会响应外部中断

最后

给大家送一个小福利

[外链图片转存中…(img-TLa6gwwN-1714536484442)]

附高清脑图,高清知识点讲解教程,以及一些面试真题及答案解析。送给需要的提升技术、准备面试跳槽、自身职业规划迷茫的朋友们。

[外链图片转存中…(img-dM7T2NRc-1714536484442)]

1354

1354

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?