🚀DDR 3200Mbps设计全解析:高速布线中的陷阱与应对策略

一、为何DDR 3200Mbps设计如此棘手?

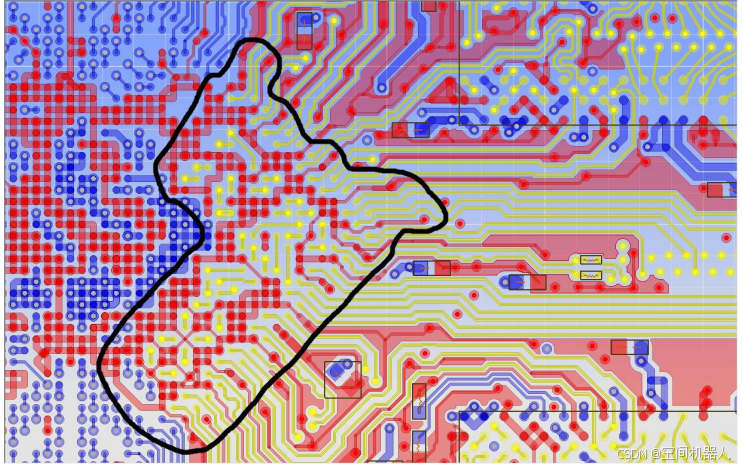

当DDR数据速率提升到3200Mbps时,设计难度不仅线性增加,而是呈指数级增长。这是由于高速信号具备以下特性:

- 信号上升沿更快:边沿陡峭,容易激发EMI;

- 眼图窗口变窄:Timing裕量极小;

- 信号易反射和串扰:对阻抗不连续极为敏感;

- 布线要求更精细:等长误差控制在mm甚至mil级别;

- 电源完整性要求更高:PDN噪声易影响数据稳定。

因此,每一个信号线的拓扑、阻抗、长度、过孔结构都必须谨慎设计。

订阅专栏 解锁全文

订阅专栏 解锁全文

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?