本文章着重与介绍LVDS的发展背景、电气参数以及如何代码实现符合LVDS的接收器。

1 LVDS 概述

1.1 背景

定义:LVDS,即Low Voltage Differential Signaling。是一种低压差分信号技术接口。利用非常低的电压摆幅(约350mV)在两条PCB走线或一对平衡电缆上通过差分进行数据的传输,即低压差分信号输出。

采用TTL接口的缺点是:

传输速率低

传输距离较短

电磁抗干扰能力较差,对RGB数据造成一定的影响

多路数据信号采用排线连接方式,连接不便,且不适合超薄化趋势

采用LVDS可以使以上问题迎刃而解,实现数据的高速率,低噪声,远距离,高准确度的传输。

LCD驱动板传输的数字信号包括:

RGB数字信号

行同步信号HS

场同步信号VS

数据使能信号DE

像素时钟等

1.2 LVDS Interface电路组成

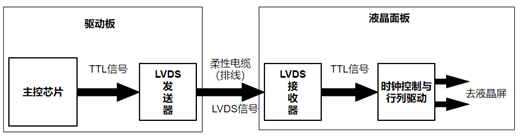

在LCD显示器中,LVDS接口电路包括两部分:驱动板侧的LVDS输出驱动电路(LVDS发送器)和液晶面板侧的LVDS输入接口电路(LVDS接收器)。

LVDS发送器:将驱动板主控芯片输出的TTL电平并行RGB数据信号和控制信号转换为低压串行LVDS信号;

LVDS接收器:将串行信号转换为TTL电平的并行信号,送往液晶屏时序控制与行列驱动电路。接收器与发送器之间使用柔性电缆。结构图如下所示:

在传输过程中,还必须有时钟信号参与,LVDS接口在传输数据和时钟时都是采用差分信号对的形式进行传输。所谓信号对,指LVDS接口电路中,每一个数据传输通道或时钟传输通道的输出都是两个信号(正输出端+和负输出端-)。

LVDS输出接口类型

类别 |

单路6bit |

双路6bit |

本文详细介绍了LVDS(低压差分信号)技术,包括其发展背景、电路组成以及数据输出格式。LVDS作为一种高速、低噪声、长距离传输的接口,解决了TTL接口的不足,常用于LCD驱动板。LVDS接口电路由LVDS发送器和接收器组成,数据通过差分信号对传输。在LVDS发送器中,串行器将并行数据转换为串行数据,时钟生成电路提供多相时钟,输出驱动电路则产生有效的差分输出信号。

本文详细介绍了LVDS(低压差分信号)技术,包括其发展背景、电路组成以及数据输出格式。LVDS作为一种高速、低噪声、长距离传输的接口,解决了TTL接口的不足,常用于LCD驱动板。LVDS接口电路由LVDS发送器和接收器组成,数据通过差分信号对传输。在LVDS发送器中,串行器将并行数据转换为串行数据,时钟生成电路提供多相时钟,输出驱动电路则产生有效的差分输出信号。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2681

2681

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?