时序逻辑电路是数字电路中非常重要的一类,它们不仅仅依赖输入信号,还依赖于电路的过去状态。与组合逻辑电路不同,时序电路的输出不仅仅由当前的输入决定,还与电路的历史状态相关,因而需要通过时钟信号来管理电路的状态变化。以下是时序逻辑电路的详细介绍。

1. 时序逻辑电路的基本概念

- 时序电路:电路的输出不仅依赖于输入信号,还依赖于电路的内部状态。时序电路通常需要一个或多个时钟信号来触发状态的改变。

- 状态:时序电路中,电路的状态由一组寄存器(例如触发器或锁存器)保存。每个状态可以表示电路的一种特定配置或行为。

- 时钟:时序电路通常通过时钟信号来控制状态的转换。时钟信号的周期性波动决定了电路状态的更新时机。

- 同步时序电路与异步时序电路:

- 同步时序电路:所有状态转换都由时钟信号同步控制。

- 异步时序电路:状态的转换由输入信号或其他条件驱动,不依赖统一的时钟信号。

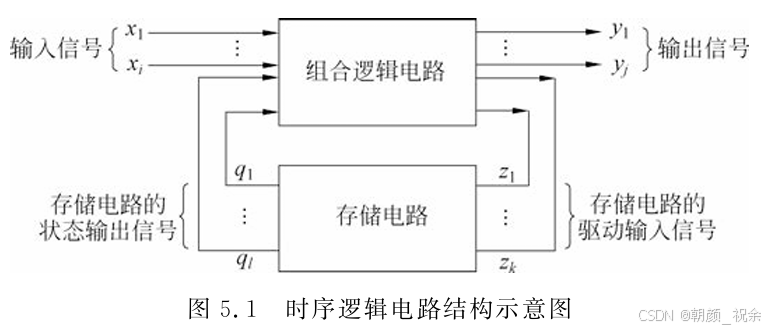

2. 时序电路的基本组成

时序电路的组成包括两部分:

- 组合逻辑电路:根据当前输入和状态计算输出,常见的组合逻辑单元有与门、或门、非门、与非门、或非门等。

- 存储元件(触发器或锁存器):存储电路的状态信息。常见的存储元件有D触发器、T触发器、JK触发器、SR触发器等。

存储元件的作用是根据时钟信号的变化更新电路的状态。存储元件的状态由前一时刻的输入决定,并在时钟的控制下进行改变。

3. 时序电路的分类

时序电路可以根据不同的标准进行分类,主要有以下两类:

3.1 根据时钟的使用:

- 同步时序电路:所有的状态转换都由时钟信号同步控制,状态变化发生在时钟的上升沿或下降沿。典型应用:计数器、状态机。

- 异步时序电路:状态变化不依赖时钟信号,而是由输入信号直接触发。异步电路设计复杂,容易发生不稳定或竞态现象,实际中较少使用。典型应用:异步计数器、异步状态机。

3.2 根据功能分类:

- 计数器:用于对时钟脉冲进行计数。分类:同步计数器、异步计数器、二进制计数器、十进制计数器等。

- 寄存器:用于存储二进制数据。分类:移位寄存器、并行寄存器

- 状态机:用于实现特定的状态转换逻辑。分类:有限状态机(FSM)。Moore型时序电路:在Moore电路中,输出仅与当前状态有关,与输入无关。即每个状态都有唯一的输出。Mealy型时序电路:在Mealy电路中,输出不仅与当前状态有关,还与输入信号相关。输入的变化可以直接影响输出。

4. 常见的时序逻辑元件

以下是常见的时序逻辑电路元件,它们是构建时序电路的基本单元。

4.1 触发器

触发器是时序逻辑电路中最基本的存储元件,常用的触发器有:

- D触发器(数据触发器):D触发器的输出仅由输入D和时钟信号决定,输入信号在时钟脉冲的上升或下降沿时被传递到输出。

数据锁存功能,输出等于输入D。

常用于寄存器和状态机。

- JK触发器:JK触发器是一个具有两个输入(J和K)和时钟输入的触发器。它可以执行更复杂的状态控制。

改进SR触发器,消除了禁止状态。

功能:J=1、K=1时,状态翻转

- T触发器:T触发器的工作原理简单,当T为1时,触发器的输出状态会在时钟脉冲时翻转;当T为0时,输出不变。

- SR触发器:SR触发器有两个输入(S和R),通过这两个输入控制输出的状态。 基本功能:置位(Set)和复位(Reset)。 缺点:存在禁止状态(S=R=1)。

4.2 计数器(Counter)

计数器是用电路的状态变化累计时钟脉冲CP作用个数的时序逻辑电路,此外还有定 时、分频等功能,是数字系统中用途最广泛的基本部件。

计数器由具有存储记忆功能的触发器构成,n个触发器共有2^n个状态,可用其中的部 分状态或全部状态进行计数。

计数器有如下4种分类方法。

(1)按计数时钟脉冲输入方式分类。

①同步计数器。计数时钟脉冲CP接至所有触发器的时钟端,使应改变状态的触发器 同时改变状态。 ②异步计数器。计数时钟脉冲CP不接至所有触发器的时钟端,使应改变状态的触发 器不同时改变状态。

(2)按模数N 分类。 计数器计数时所经历循环变化的有效状态数称为模数N。

①二进制计数器。由n个触发器组成,模数N=2n,没有无效状态。

②十进制计数器。由4个触发器组成,模数N=10,有6个无效状态。

③非二进制计数器。由n个触发器组成,模数N<2n,有2n-N 个无效状态。

(3)按计数增减规律分类。

①加法计数器。递增规律计数。

②减法计数器。递减规律计数

③ 可逆计数器。可加可减计数。

④ 特殊编码规律计数器。

(4) 按电路的集成度分类。

① 小规模计数器。由若干个集成触发器和门电路经外部连接构成某种类型的计数器。

② 中规模集成计数器。一般由4个触发器和若干个门电路经内部连接集成在一块硅片上,计数功能比较完善并能扩展。

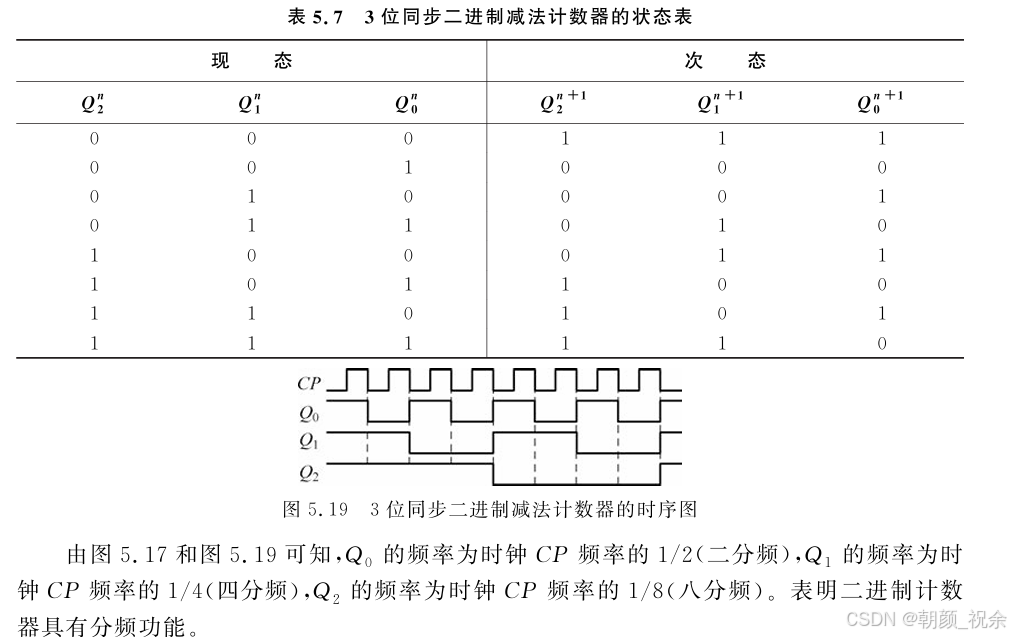

1. 同步计数器

1) 同步二进制计数器

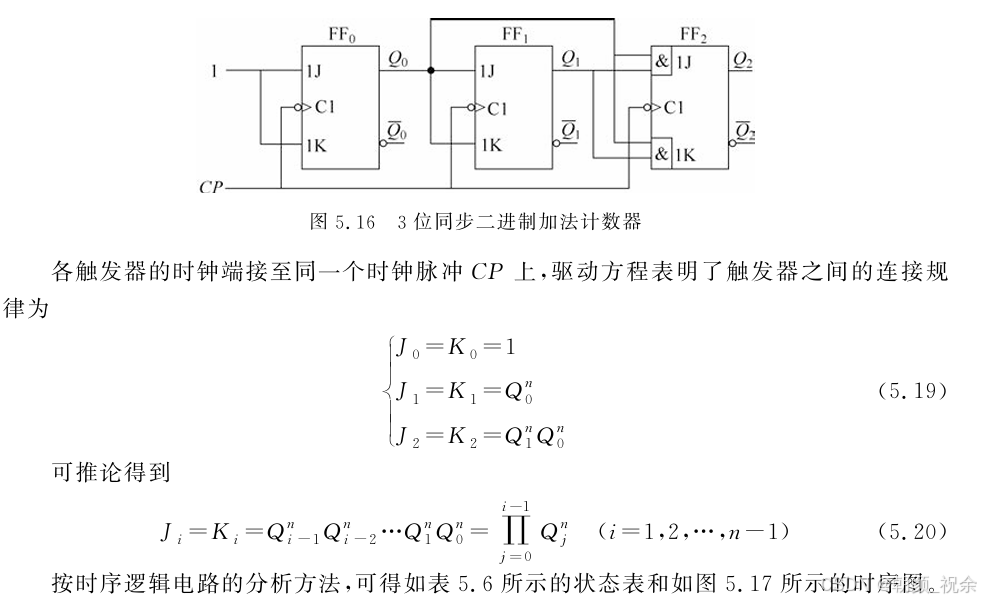

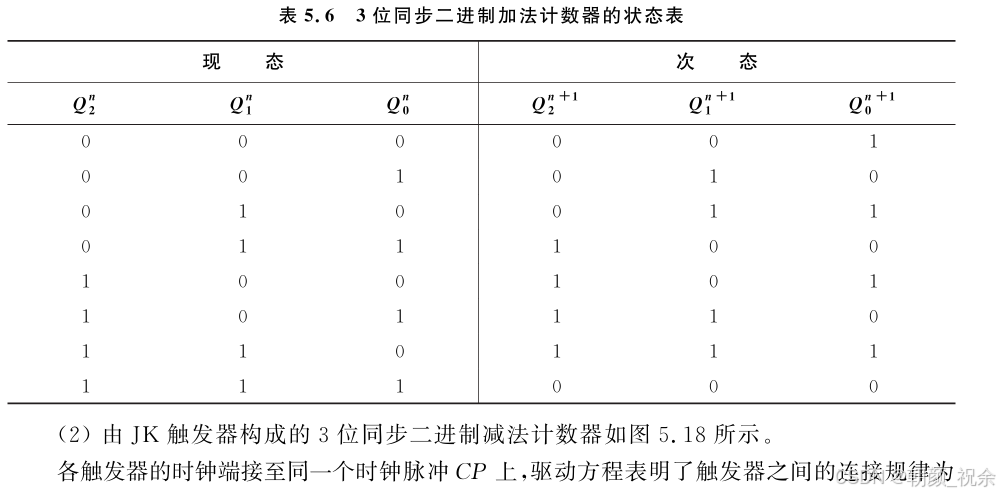

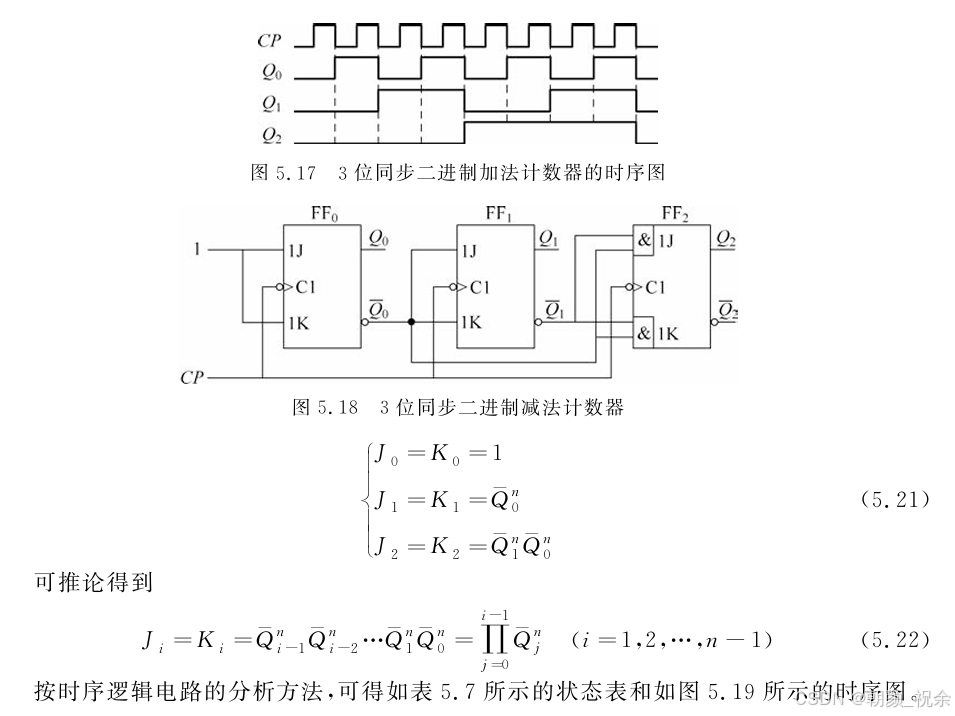

(1) 由JK触发器构成的3位同步二进制加法计数器如图5.16所示。

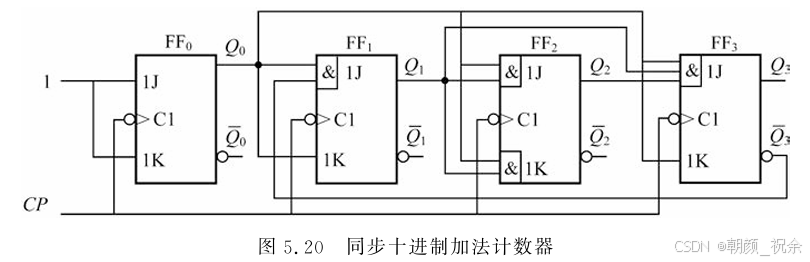

2) 同步十进制计数器

由JK触发器构成的同步十进制加法计数器如图5.20所示。

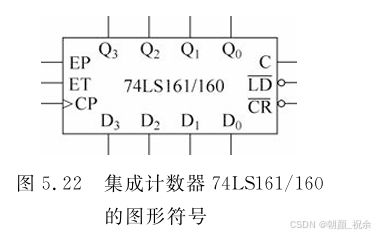

3) 集成同步可预置数4位二进制/十进制计数器74LS161/160

集成同步可预置数4位二进制/十进制计数器74LS161/160是典型的常用中规模集成计数器。

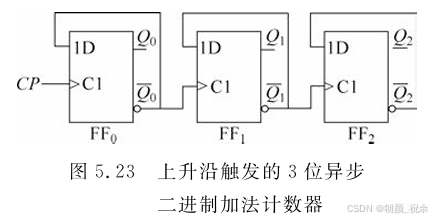

2. 异步计数器

1) 异步二进制计数器 异步二进制计数器必须满足下列构成条件。

(1) 最低位触发器,每接收一个输入计数脉冲翻转一次。

(2) 最低位以外的触发器,每当接收相邻低位触发器送来的进位或借位信号就翻转 一次。

加法计数器: 当触发器由1态变0态时向高位进位,该触发器Q 端的负向脉冲(或非 Q 端的正向脉冲)作为进位信号。对于上升沿触发器,其CP端应接相邻低位触发器的非 Q 端; 对于下降沿触发器,其CP端应接相邻低位触发器的Q 端。

减法计数器: 当触发器由0态变1态时向高位借位,该触发器Q 端的正向脉冲(或非Q端 的负向脉冲)作为借位信号。对于上升沿触发器,其CP端应接相邻低位触发器的Q端; 对于 下降沿触发器,其CP端应接相邻低位触发器的非 Q端。

(3) 计数器中的触发器均构成T' 触发器。 异步二进制计数器可分为以下4类。

(1) 上升沿触发的异步二进制加法计数器。

由上升沿D触发器构成的3位异步二进制 加法计数器如图5.23所示。 按时序逻辑电路的分析方法,可得如表5.10 所示的状态表。

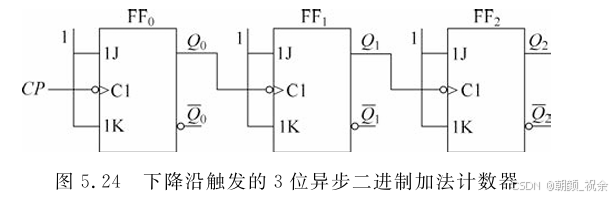

(2) 下降沿触发的异步二进制加法计数器。

由下降沿JK触发器构成的3位异步二进制加法计数器如图5.24所示。

(3) 上升沿触发的异步二进制减法计数器。

由上升沿D触发器构成的3位异步二进制减法计数器如图5.25所示。

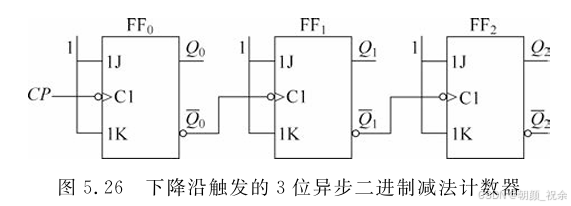

(4) 下降沿触发的异步二进制减法计数器。

由下降沿JK触发器构成的3位异步二进制减法计数器如图5.26所示。

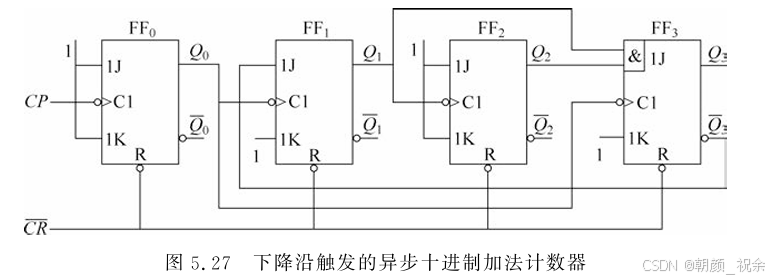

2) 异步十进制计数器

由下降沿JK触发器构成的异步十进制加法计数器如图5.27所示。

4.3 移位寄存器(Shift Register)

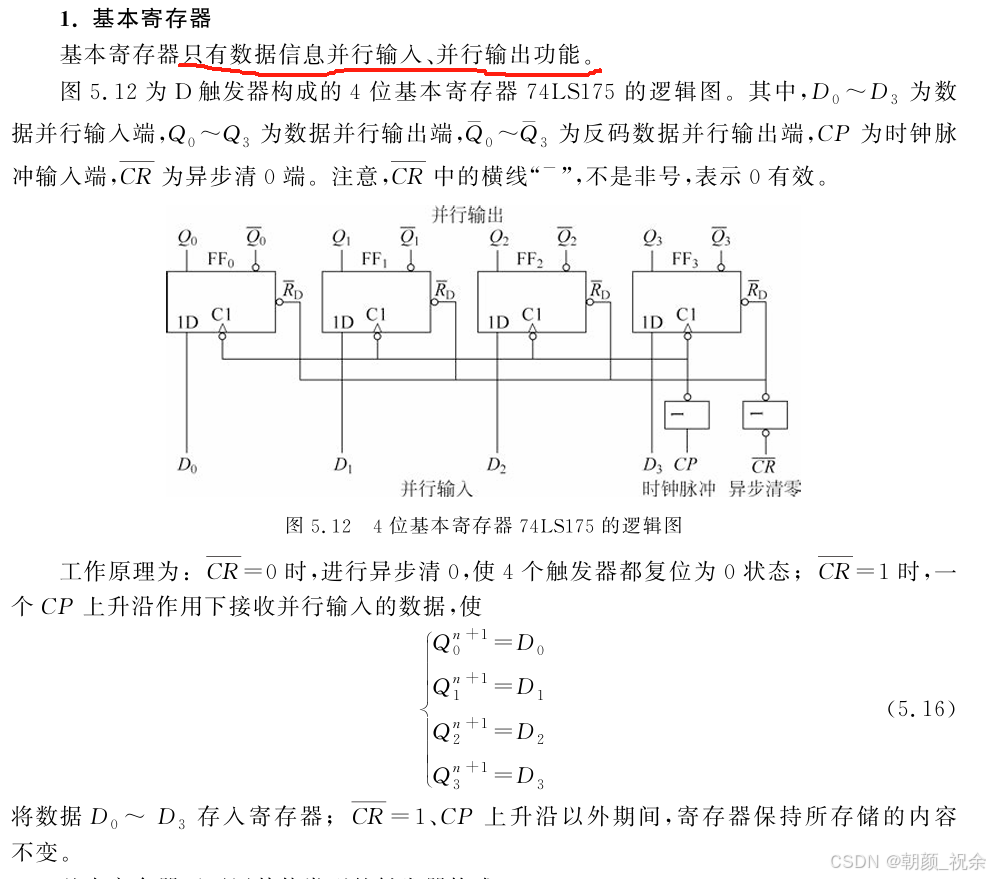

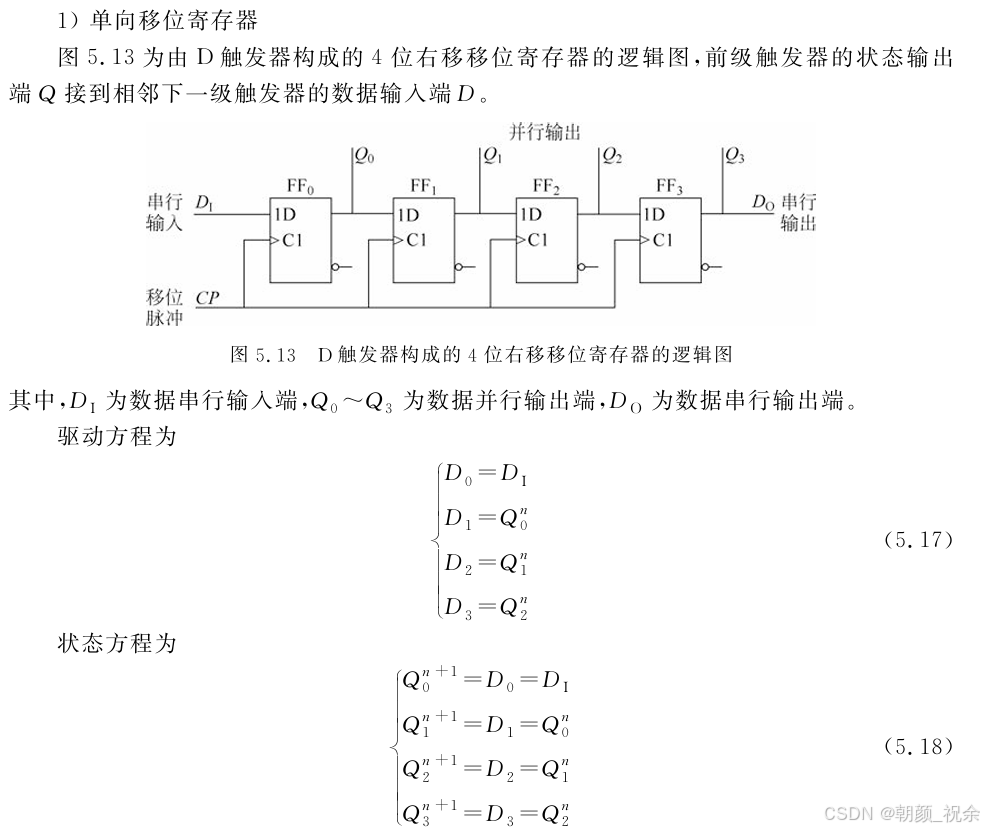

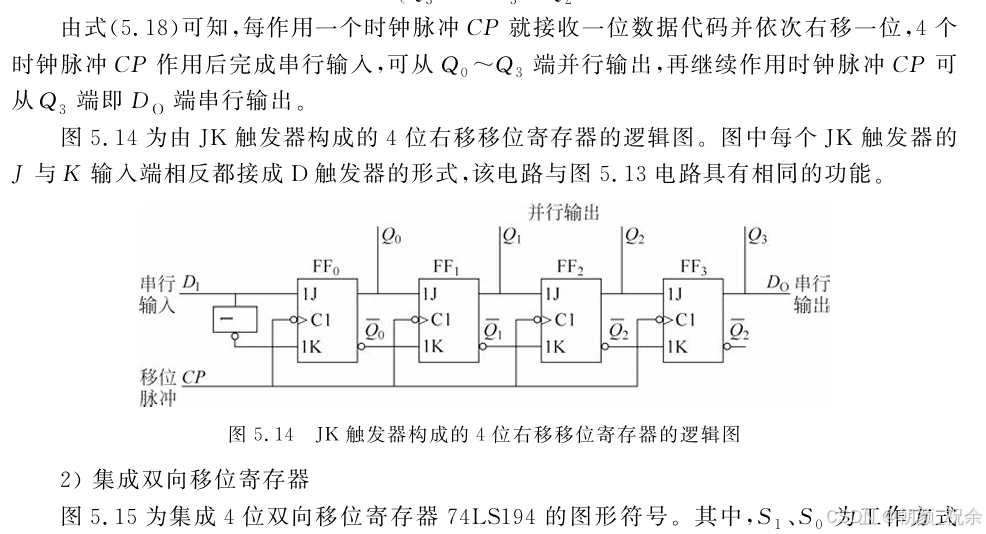

寄存器是用来暂时存放一组二进制数据信息的逻辑记忆电路,它是计算机及接口技术的一种重要部件。寄存器由具有存储记忆功能的触发器和控制接收数据的控制门构成,触发器的个数等于所存储二进制数据信息的位数。按寄存功能不同,寄存器分为基本寄存器和移位寄存器。

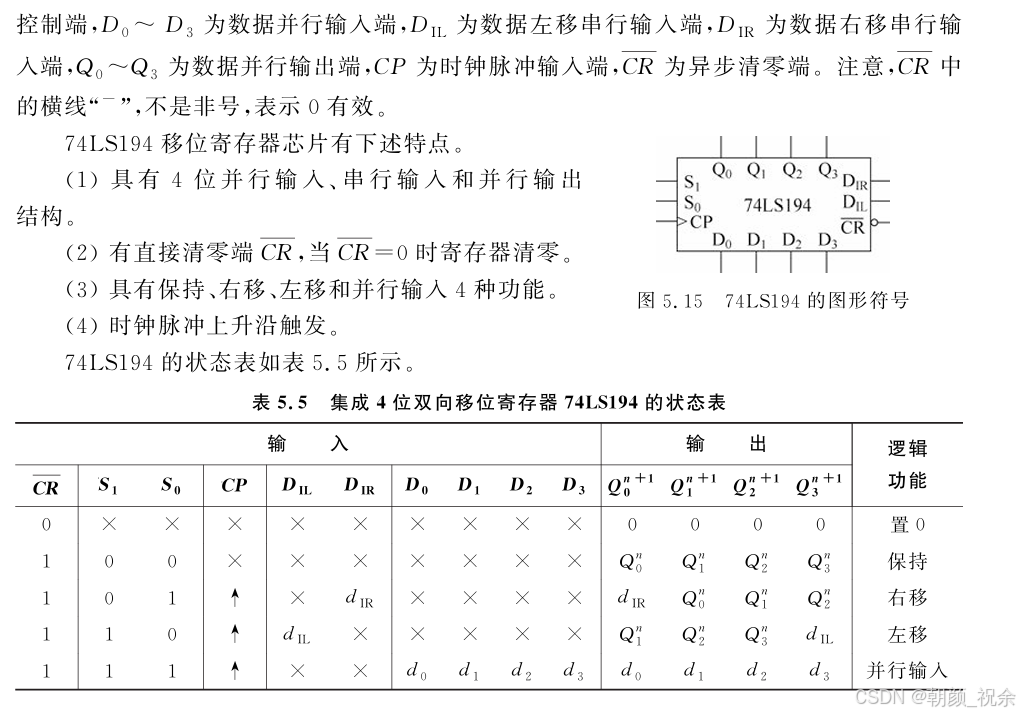

2.移位寄存器

移位寄存器可以串行输入、输出及并行输入、输出数据信息,在移位脉冲CP的作用下可使寄存 的数据依次逐位右移或左移。具有单向移位功能的寄存器称为单向移位寄存器,既可右移又可 左 移的寄存器称为双向移位寄存器。

4.4 有限状态机(Finite State Machine, FSM)

有限状态机用于实现复杂的控制逻辑,常见类型包括:

-

Mealy型状态机:

-

输出取决于当前状态和输入信号。

-

-

Moore型状态机:

-

输出仅取决于当前状态。

-

4.5 锁存器

锁存器是一种能够保存和保持状态的电路,它通常由两级门电路组成。锁存器对输入的响应是实时的,不像触发器那样受时钟信号的控制。

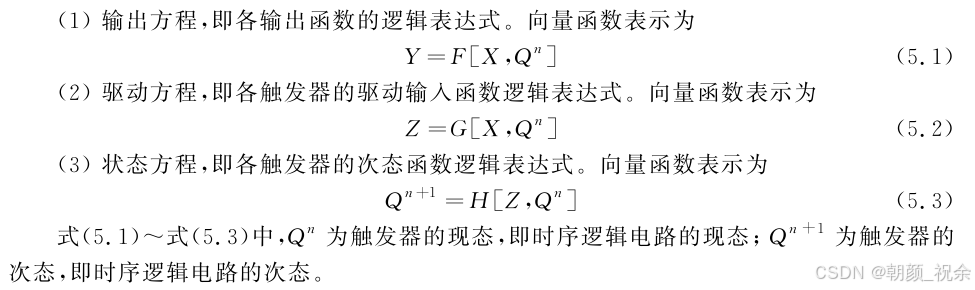

5. 时序逻辑电路逻辑功能的描述方法

1.逻辑表达式

一般有三组方程。

2.状态转换表

反映时序逻辑电路由现态到次态的状态转换关系,实现转换所需输入条件及现态输出 的真值表,简称状态表。

3.状态转换图

反映时序逻辑电路由现态到次态的状态转换关系,实现转换所需输入条件及现态输出 的图形,简称状态图。

4.时序图

反映时序逻辑电路在时钟序列脉冲作用下,由现态到次态的状态转换关系,实现转换所 需输入条件及现态输出的波形。

6. 时序电路的常见应用

时序逻辑电路广泛应用于各种数字系统中,包括但不限于:

- 计数器:使用时序电路设计的计数器能够按时钟脉冲顺序计数。

-

用于时钟分频、定时器、频率计等。

- 寄存器:用于保存数据的存储单元,是CPU的基本组成部分。

-

用于数据存储、数据传输、数据缓冲等。

- 时序控制器:如状态机,常用于控制各种流程。

-

用于控制系统、通信协议、数字信号处理等。

- 同步电路:时序电路常用于处理同步信号、信号时序等问题。

-

用于串行通信、数据加密、数据压缩等。

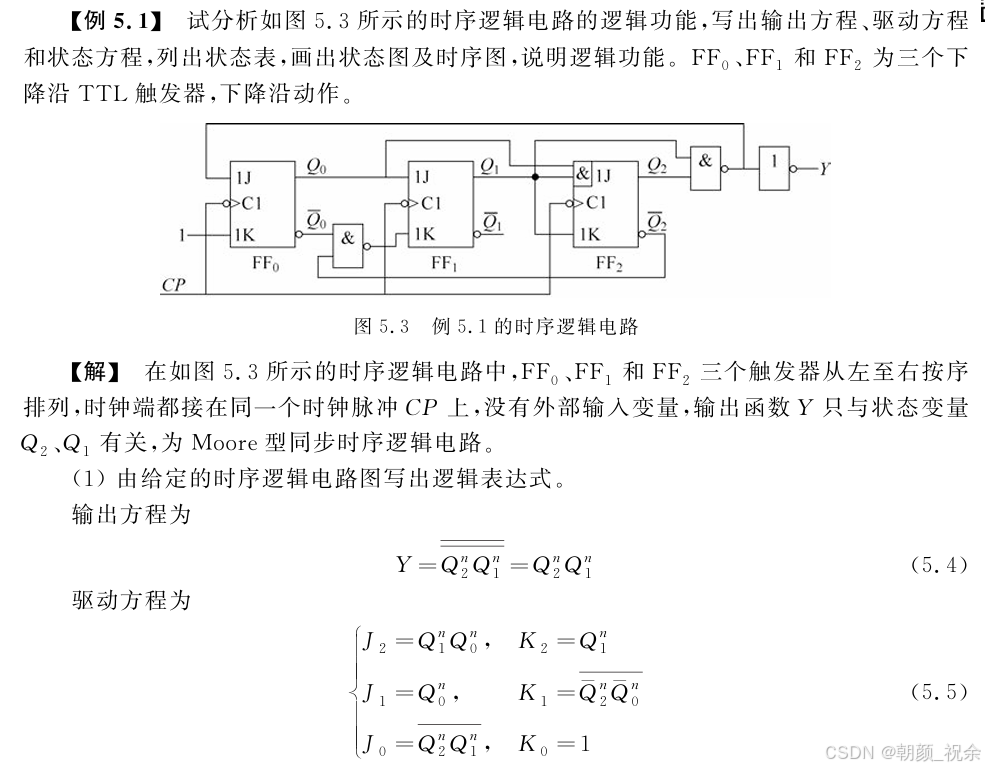

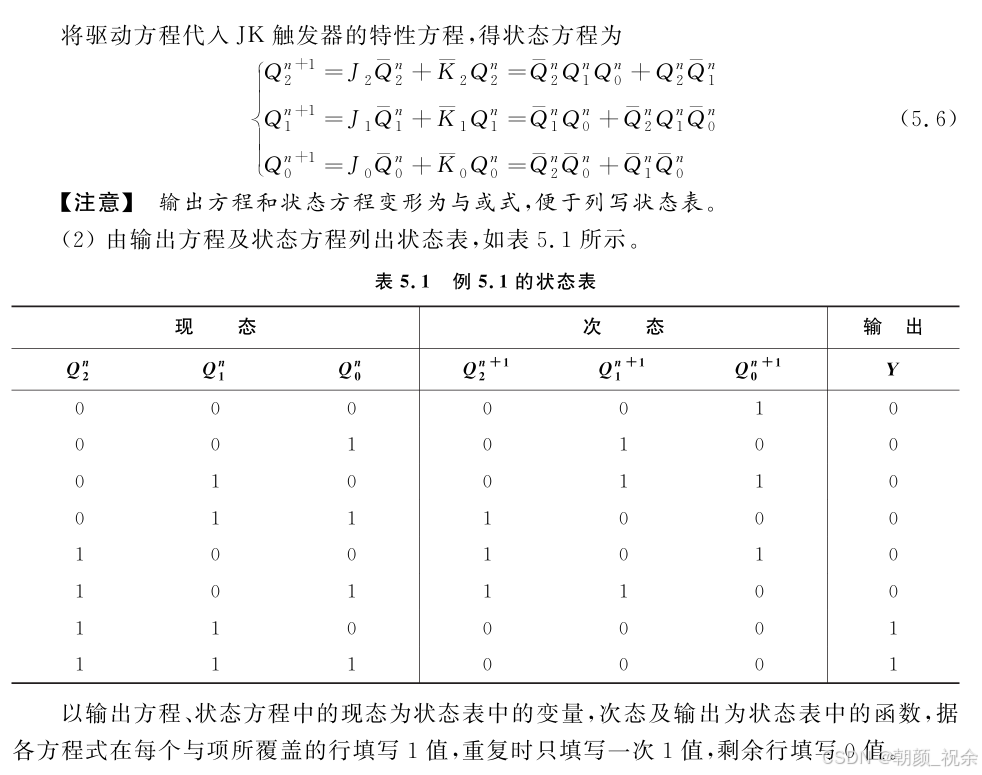

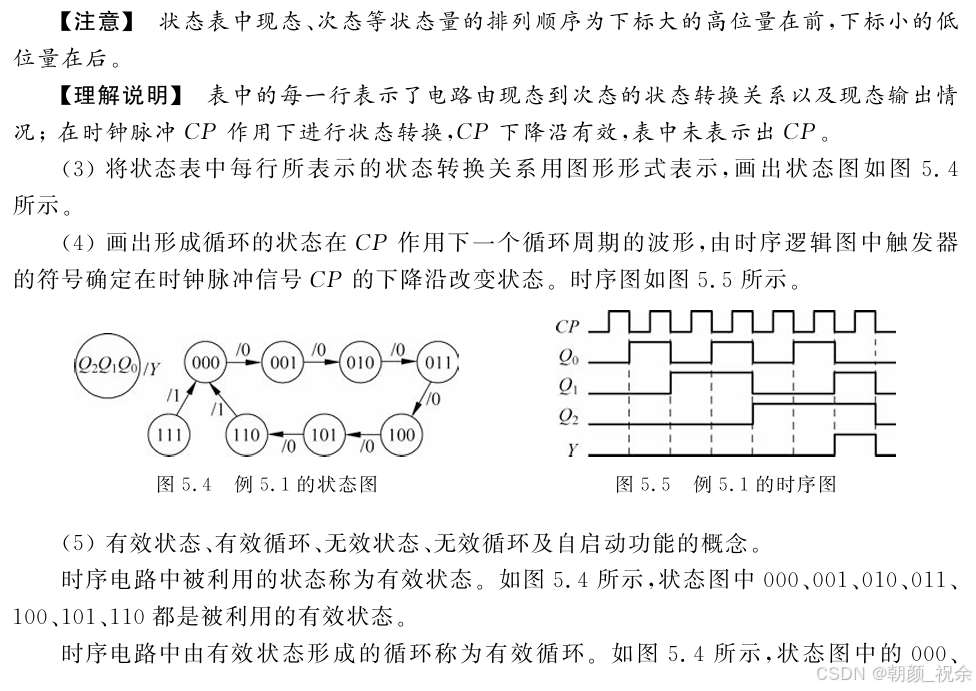

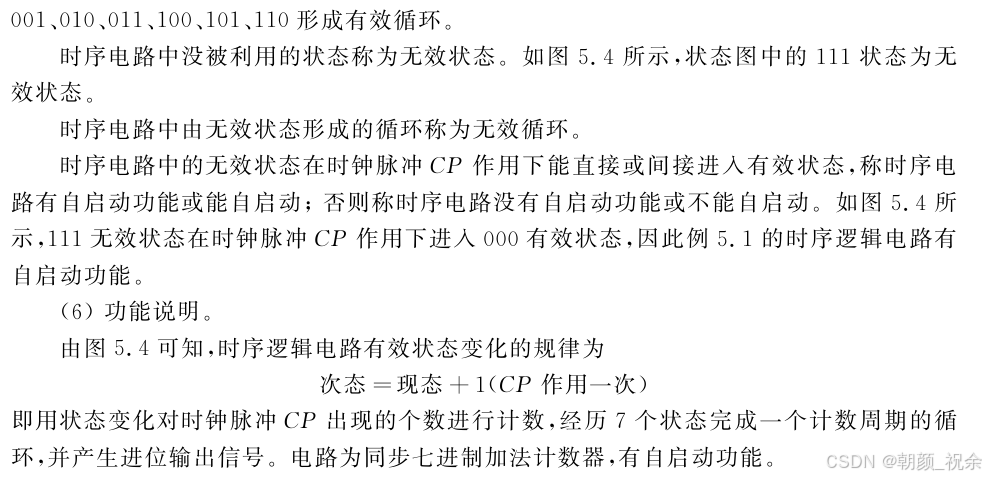

7. 同步时序逻辑电路分析举例

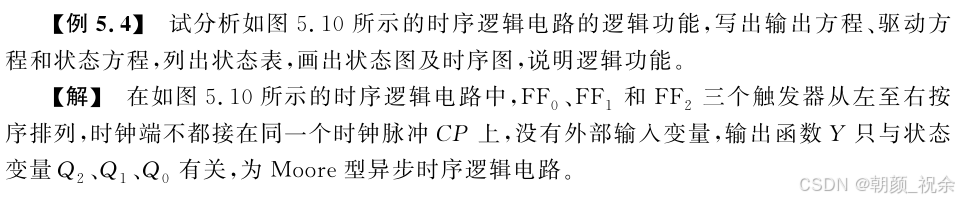

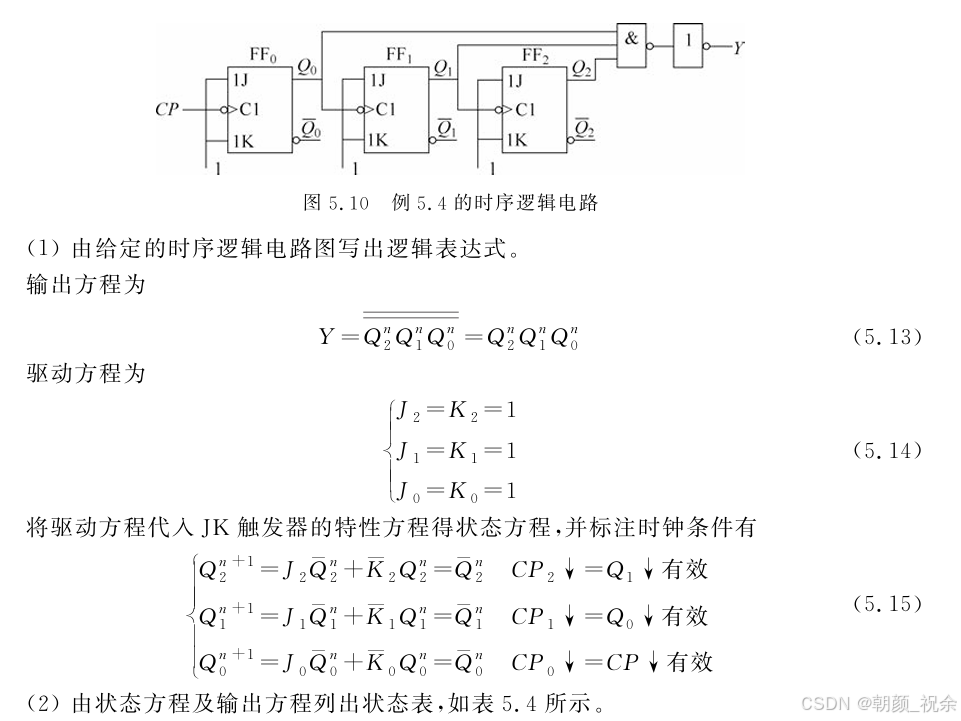

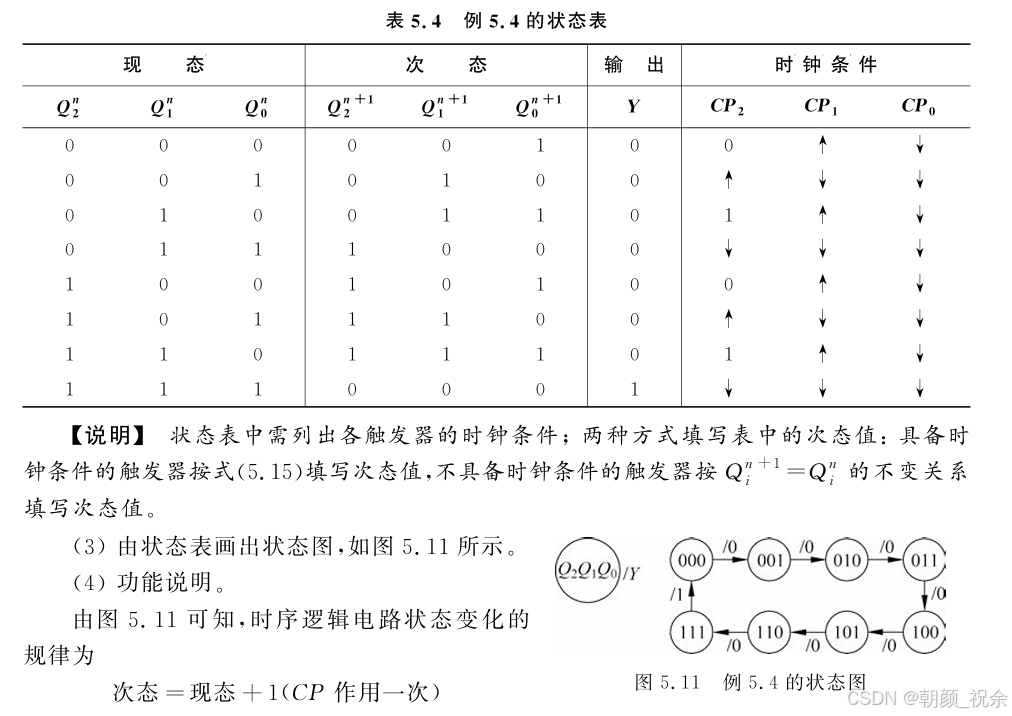

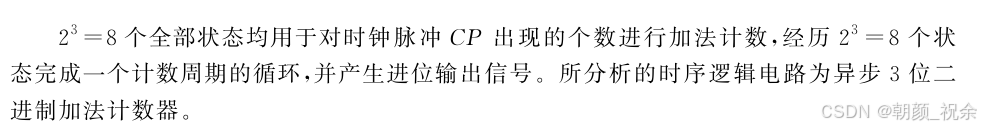

异步时序逻辑电路分析举例

3750

3750

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?