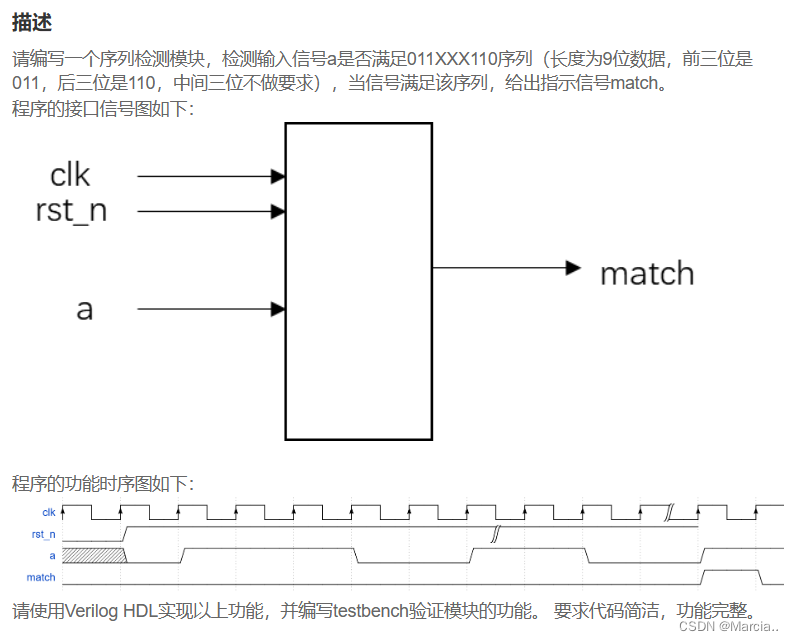

VL26 含有无关项的序列检测

有了上一题的基础,这一题就变得十分简单,不明白的朋友可以看我的上一篇博客牛客数字IC刷题记录(1)—序列检测器VL25

在上一题的基础上稍作修改,这里还是用两种方法做:

我会在代码里把修改的点用change的注释标出来。

1、状态机法:

`timescale 1ns/1ns

module sequence_detect(

input clk,

input rst_n,

input a,

output reg match

);

parameter IDLE = 10'b00_0000_0001,

S1 = 10'b00_0000_0010,

S2 = 10'b00_0000_0100,

S3 = 10'b00_0000_1000,

S4 = 10'b00_0001_0000,

S5 = 10'b00_0010_0000,

S6 = 10'b00_0100_0000,

S7 = 10'b00_1000_0000,

S8 = 10'b01_0000_0000,

S9 = 10'b10_0000_0000;//change1 上一题8bit这题变9bit了

reg [9:0]state,next_state;

always@(posedge clk or negedge rst_n)

begin

if(!rst_n)

state <= IDLE;

else

state <= next_state;

end

always@(*)

begin

if(!rst_n)

next_state <= IDLE;

else

case(state)//change2 注意对应的状态跳转x的时候直接下一个状态,无需判断

IDLE:next_state <= (~a)?S1:IDLE;//0

S1:next_state <= a?S2:IDLE;//1

S2:next_state <= a?S3:IDLE;//1

S3:next_state <= S4;//x

S4:next_state <= S5;//x

S5:next_state <= S6;//x

S6:next_state <= a?S7:IDLE;//1

S7:next_state <= a?S8:IDLE;//1

S8:next_state <= (~a)?S9:IDLE;//0

S9:next_state <= IDLE;

default:next_state <= IDLE;

endcase

end

always@(posedge clk or negedge rst_n)

begin

if(!rst_n)

match <= 1'b0;

else if(state==S9)//change3 9bit都判断完拉高match

match <= 1'b1;

else

match <= 1'b0;

end

endmodule

2、序列缓存对比法

相比于原来固定值的序列01110001这题多了几个不定态xxx,那么咱们只需要把有数的几bit数单独拿出来,能和咱们要的数完全相等即可:

`timescale 1ns/1ns

module sequence_detect(

input clk,

input rst_n,

input a,

output reg match

);

reg [8:0]reg_a;//change1 上一题8bit这题变9bit了

always@(posedge clk or negedge rst_n)

begin

if(!rst_n)

reg_a <= 9'b0;

else

reg_a <= {reg_a[7:0],a};//change2 位宽随之修改

end

always@(posedge clk or negedge rst_n)

begin

if(!rst_n)

match <= 1'b0;

else if((reg_a[8:6] == 3'b011) && (reg_a[2:0] == 3'b110) )//change3 单独把有数的bit拎出来,看看相等不

match <= 1'b1;

else

match <= 1'b0;

end

endmodule

也是主打一个通过!

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?