MT25QU128在开发板复位时,应该复位。复位时,66h和99h应该单独片选,即:片选,发送66h,取消片选,片选,发送99h,取消片选。

注意电压为1.8V。

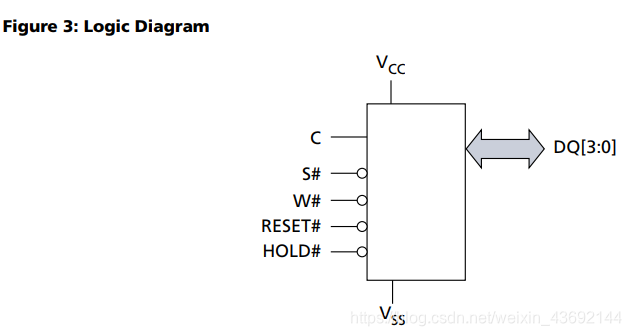

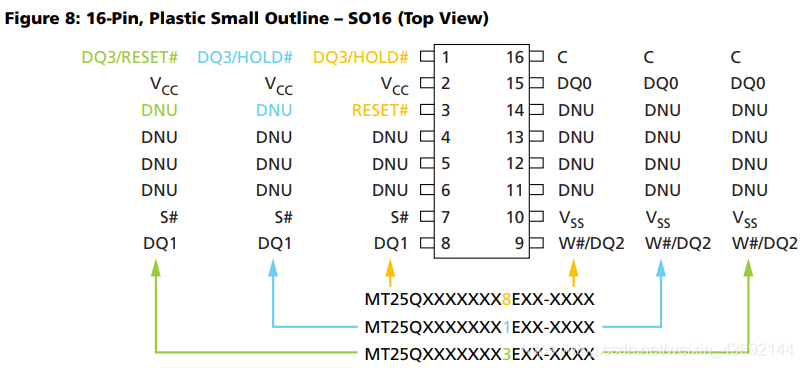

每个具体型号的MT25Q设备的引脚有所不同,有的没有RESET或HOLD引脚,如下所示:

| 引脚名 | 类型 | 功能描述 | |

| S# | 输入 | 片选:将S#驱动为高电平时,除非正在进行内部编程,擦除或写状态寄存器周期,否则器件将进入待机模式。 所有其他输入引脚均被忽略,输出引脚为三态。 但是,在具有专用RESET#引脚的引脚配置的器件上,即使S#为高电平,RESET#输入引脚仍保持活动状态。 将S#驱动为低电平会启用设备,使其处于活动模式。 上电后,在开始任何命令之前,需要在S#上提供一个下降沿。 | |

| C | 输入 | 时钟:提供串行接口的时序。 命令输入在时钟的上升沿锁存。 在STR命令或协议中,当数据在时钟的下降沿输出时,地址和数据输入在时钟的上升沿锁存。 在DTR命令或协议中,地址和数据输入在时钟的两个边沿上锁存,数据在时钟的两个边沿上输出。 | |

| RESET# | 输入 | RESET#:将RESET#驱动为低电平时,器件复位并且输出为三态。 如果在进行内部写,编程或擦除操作时,将RESET#驱动为低电平,则数据可能会丢失。 可以使用非易失性配置寄存器的位4或增强型易失性配置寄存器的位4禁用RESET#功能。 RESET#共享DQ3引脚的引脚配置,在QIO-SPI模式下禁用RESET#功能。 | |

| HOLD# | 输入 | 保持:暂停与设备的串行通信,而无需取消选择或重置设备。 输出为三态,数据输入被忽略。 可以使用非易失性配置寄存器的位4或增强型易失性配置寄存器的位4禁用HOLD#功能。 HOLD#共享DQ3引脚的引脚配置,在QIO-SPI模式下或启用DTR操作时,将禁用HOLD#功能。 | |

| W# | 输入 | 写保护:与状态寄存器的启用/禁用位一起冻结状态寄存器。 当状态寄存器的使能/禁用位设置为1且W#信号被驱动为LOW时,状态寄存器的非易失性位将变为只读状态,并且将不执行WRITE STATUS REGISTER操作。 在具有QOFR和QIOFR指令的扩展SPI协议以及QIO-SPI协议中,此引脚功能是作为DQ2功能的输入/输出。 该信号没有内部上拉,即使不使用W#/ DQ2功能,也不能悬空并且必须被驱动。 | |

| DQ[3:0] | 输入/输出 | 串行I / O:双向DQ信号传输地址,数据和命令信息。 在扩展I / O协议(XIO-SPI)中使用旧版(x1)SPI命令时,DQ0是输入,DQ1是输出。 不使用DQ [3:2]。 在XIO-SPI中使用双命令或在DIO-SPI中使用时,DQ [1:0]是I / O。 不使用DQ [3:2]。 在XIO-SPI中使用四线指令或在QIO-SPI中使用时,DQ [3:0]是I / O。 | |

| Vcc | 电源 | 正极 | |

| Vss | 电源 | 接地 | |

| DNU | - | Do not use | |

| NC | - | No connect | |

| RFU | - | Reserved for future use |

状态寄存器

可以分别使用READ STATUS REGISTER或WRITE STATUS REGISTER命令读取或写入状态寄存器位。 当状态寄存器启用/禁用位(位7)设置为1且W#被驱动为LOW时,状态寄存器的非易失性位变为只读状态,并且将不执行WRITE STATUS REGISTER操作。 退出此硬件保护模式的唯一方法是将W#驱动为高电平。

| 位 | 名称 | 设置 | 功能描述 | 注释 |

| 7 | Status register write enable/disable | 0 = Enabled(默认) 1 = Disabled | 非易失性控制位:与W#一起使用,以启用或禁用对状态寄存器的写入。 | |

| 5 | Top/bottom | 0 = Top(默认) 1 = Bottom | 非易失性控制位:确定由块保护位定义的受保护存储区是从存储阵列的顶部还是底部开始。 | |

| 6,4:2 | BP[3:0] | 查看保护区域表 | 非易失性控制位:定义要进行软件保护的存储器,以防止PROGRAM或ERASE操作。 当一个或多个块保护位设置为1时,将保护指定的存储区免受PROGRAM和ERASE操作的影响。 | 仅当所有位= 0时才执行BULK ERASE命令。 |

| 1 | Write enable latch | 0 = Clear(默认) 1 = Set | 易失性控制位:器件始终在上电时清除该位,以防止意外的写,编程或擦除操作。 要启用这些操作,必须首先执行WRITE ENABLE操作以将该位置1。 | |

| 0 | Write in propress | 0 = Ready(默认) 1 = Busy | 易失性状态位:指示是否为以下之一 命令周期正在进行中: 写状态寄存器 写非易失性配置寄存器 程序 擦除 | 状态寄存器的位0与标志状态寄存器的位7相反。 |

标记状态寄存器

使用READ FLAG STATUS REGISTER命令读取标志状态寄存器位。 所有位都是易失性的,上电时复位为零。

状态位由内部控制器自动设置和重置。 错误位必须通过CLEAR STATUS REGISTER命令清除。

| 位 | 名称 | 设置 | 功能描述 | 注释 |

| 7 | Program or erase controller | 0 = Busy 1 = Ready | 状态位:指示是否为以下之一 命令周期正在进行中:WRITE STATUS 寄存器,写入非易失性配置寄存器,写或擦除 | |

| 6 | Erase suspend | 0 = Clear 1 = Suspend | 状态位:指示是否已暂停或将要暂停ERASE操作。 | |

| 5 | Erase | 0 = Clear 1 = Failure or protection error | 错误位:指示ERASE操作是成功还是失败。 | |

| 4 | Program | 0 = Clear 1 = Failure or protection error | 错误位:指示写操作是成功还是失败。 它还指示CRC检查是成功还是失败。 | |

| 3 | Reserved | 0 | 保留 | |

| 2 | Program suspend | 0 = Clear 1 = Suspend | 状态位:指示是否已暂停或即将暂停PROGRAM操作。 | |

| 1 | Protection | 0 = Clear 1 = Failure or protection error | 错误位:指示ERASE或PROGRAM操作是否已尝试修改受保护的阵列扇区,或者PROGRAM操作是否已尝试访问锁定的OTP空间。 | |

| 0 | Reserved | 0 | 保留 |

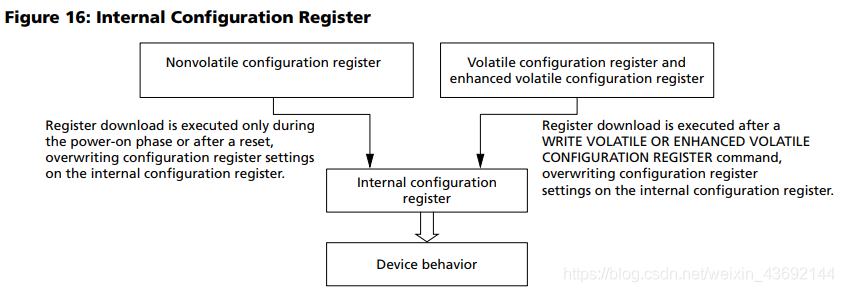

内部配置寄存器

内存配置由内部配置寄存器设置,用户无法直接访问该内部配置寄存器。

用户可以使用“写入非易失性配置寄存器”在开机时更改默认配置。 非易失性配置寄存器中的信息在上电期间或复位后会覆盖内部配置寄存器。

用户可以在操作过程中通过使用WRITE VOLATILE CONFIGURATION REGISTER或WRITE ENHANCED VOLATILE CONFIGURATION REGISTER命令来更改配置。 WRITE命令完成后,来自易失性配置寄存器的信息会立即覆盖内部配置寄存器。

非易失性配置寄存器

分别使用“读取非易失性配置寄存器”和“写入非易失性配置寄存器”命令读取和写入该寄存器。 在上电期间或复位后执行寄存器值的下载刷新,覆盖确定设备行为的内部配置寄存器设置。

| 位 | 名称 | 设置 | 功能描述 | 注释 |

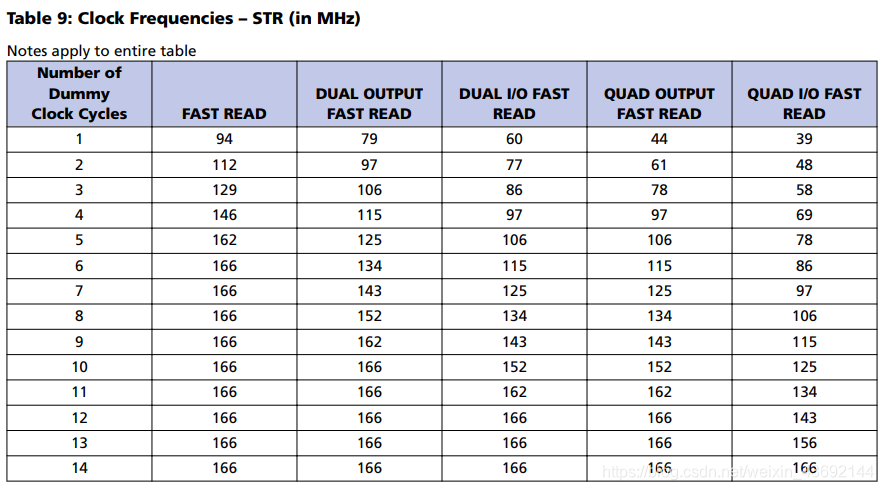

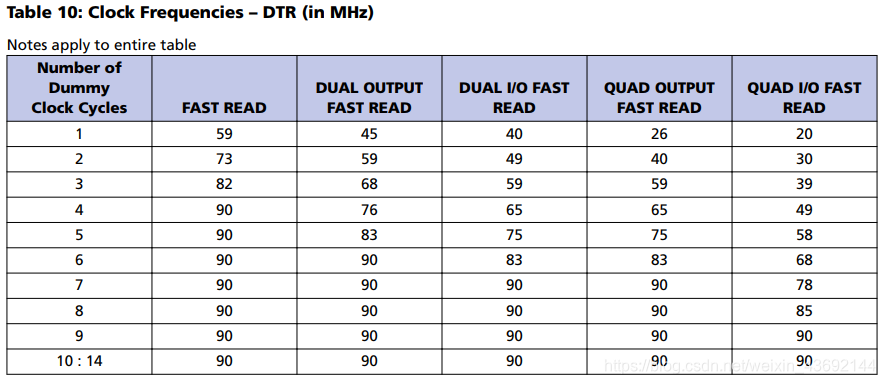

| 15:12 | Number of dummy clock cycles | 0000 = 等同于1111 0001 = 1 . . 1110 = 14 1111 = Default | 设置所有FAST READ命令之后的虚拟时钟周期数(有关默认设置值,请参见命令集表)。 | 1.必须根据时钟频率设置周期数,时钟频率随FAST READ命令的类型而变化(请参阅支持的时钟频率表)。 虚假时钟周期不足以达到工作频率会导致存储器读取错误的数据。 |

| 11:9 | XIP mode at power-on reset | 000 = XIP: Fast read 001 = XIP: Dual output fast read 010 = XIP: Dual I/O fast read 011 = XIP: Quad output fast read 100 = XIP: Quad I/O fast read 101 = Reserved 110 = Reserved 111 = Disabled(Default) | 使设备在上电复位后立即以选定的XIP模式运行。 | |

| 8:6 | Output driver strength | 000 = Reserved 001 = 90 Ohms 010 = Reserved 011 = 45 Ohms 100 = Reserved 101 = 20 Ohms 110 = Reserved 111 = 30 Ohms(Default) | 优化VCC / 2输出电压下的阻抗。 | |

| 5 | Double transfer rate protocol | 0 = Enabled 1 = Disabled(Default) | 将DTR协议设置为当前协议。 启用后,所有 命令将在DTR中起作用。 | |

| 4 | Reset/hold | 0 = Enabled 1 = Disabled(Default) | 启用或禁用DQ3引脚上的HOLD#或RESET#。 | |

| 3 | Quad I/O protocol | 0 = Enabled 1 = Disabled(Default) | 启用或禁用四路I / O命令输入(4-4-4模式)。 | 当第2位和第3位都设置为0时,设备将以四方I / O协议运行。 |

| 2 | Dual I/O protocol | 0 = Enabled 1 = Disabled(Default) | 启用或禁用双重I / O命令输入(2-2-2模式)。 | |

| 1 | Reserved | 1 | 保留 | |

| 0 | Reserved | 1 | 保留 |

易失性配置寄存器

该寄存器分别由READ VOLATILE CONFIGURATION REGISTER和WRITE VOLATILE CONFIGURATION REGISTER命令读取和写入。 在这些命令之后执行寄存器下载刷新,覆盖确定设备存储器行为的内部配置寄存器设置。

| 位 | 名称 | 设置 | 功能描述 | 注释 |

| 7:4 | Number of dummy clock cycles | 0000 = 等同于1111 0001 = 1 . . 1110 = 14 1111 = Default | 设置所有FAST READ命令之后的虚拟时钟周期数(有关默认设置值,请参见命令集表)。 | 必须根据时钟频率设置足够的周期数,并且时钟频率必须足够,这取决于FAST READ命令的类型,如“支持的时钟频率”表中所示。 虚假时钟周期数不足以达到工作频率会导致存储器读取错误的数据。 |

| 3 | XIP | 0 = Enabled 1 = Disabled(Default) | 使能或禁止XIP。 | |

| 2 | Reserved | 0 | 固定为0 | |

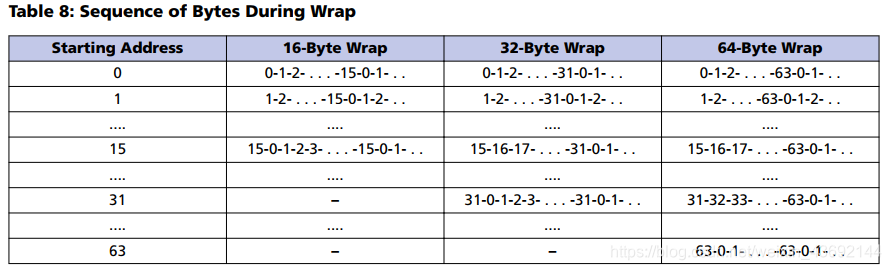

| 1:0 | Wrap | 00 = 16字节边界对齐 | 16字节换行:从命令代码后发出的3字节地址开始,输出数据在对齐的16字节边界内换行。 | 请参见换行期间的字节顺序表。 |

| 01 = 32字节边界对齐 | 32字节换行:从命令代码后发出的3字节地址开始,输出数据在对齐的32字节边界内换行。 | |||

| 10 = 64字节边界对齐 | 64字节换行:从命令代码后发出的3字节地址开始,输出数据在对齐的64字节边界内换行。 | |||

| 11 = 连续的(默认) | 连续对整个数组的地址进行排序。 |

注意:

1.数值是通过特性保证的,并非在生产中经过100%的测试。

2.当在STR模式下将时钟频率设置为高于133 MHz,在双传输速率模式下将时钟频率设置为高于66 MHz时,调整数据模式(TDP)功能为应用程序提供了用于调整主机端数据锁存点的数据模式(DTR)。 有关更多详细信息,请参阅TN-25-07:针对MT25Q和MT25T器件的调整数据模式。

注意:

1.数值是通过特性保证的,并非在生产中经过100%的测试。

2.调整数据模式(TDP)功能为应用程序提供了数据模式,用于在STR模式下将时钟频率设置为高于133 MHz且在双传输速率(DTR)中将时钟频率设置为高于66 MHz时,在主机端调整数据锁存点。 模式。 有关更多详细信息,请参阅TN-25-07:针对MT25Q和MT25T器件的调整数据模式。

增强的易失性配置寄存器

分别使用READ ENHANCED VOLATILE CONFIGURATION REGISTER和WRITE ENHANCED VOLATILE CONFIGURATION REGISTER命令读取和写入该寄存器。 在这些命令之后执行寄存器下载,覆盖确定设备存储器行为的内部配置寄存器设置。

| 位 | 名称 | 设置 | 功能说明 | 注释 |

| 7 | Quad I/O protocol | 0 = Enabled 1 = Disabled(Default) | 启用或禁用四路I / O命令输入(4-4-4模式)。 | 当第6位和第7位都设置为0时,设备将以四方I / O协议运行。 当第6位或第7位设置为0时,设备分别在双I / O或四I / O中运行。 设置该位后,设备会在“写入增强的挥发量配置注册”命令后立即进入所选协议。 下次上电或重置后,设备将返回默认协议。 另外,救援序列或其他WRITE ENHANCED VOLATILE CONFIGURATION REGISTER命令将使设备返回默认协议。 |

| 6 | Dual I/O protocol | 0 = Enabled 1 = Disabled(Default) | 启用或禁用二路I / O命令输入(2-2-2模式)。 | |

| 5 | Double transfer rate protocol | 0 = Enabled 1 = Disabled(Default, single transfer rate) | 将DTR协议设置为当前协议。 一旦启用,所有命令将在DTR中起作用。 | |

| 4 | Reset/hold | 0 = Enabled 1 = Disabled(Default) | 启用或禁用DQ3引脚上的HOLD#或RESET#。 (仅在指定的零件号上可用。) | |

| 3 | Reserved | 1 | ||

| 2:0 | Output driver strength | 000 = Reserved 001 = 90 Ohms 010 = Reserved 011 = 45 Ohms 100 = Reserved 101 = 20 Ohms 110 = Reserved 111 = 30 Ohms(Default) | 优化VCC / 2输出电压下的阻抗。 |

安全寄存器

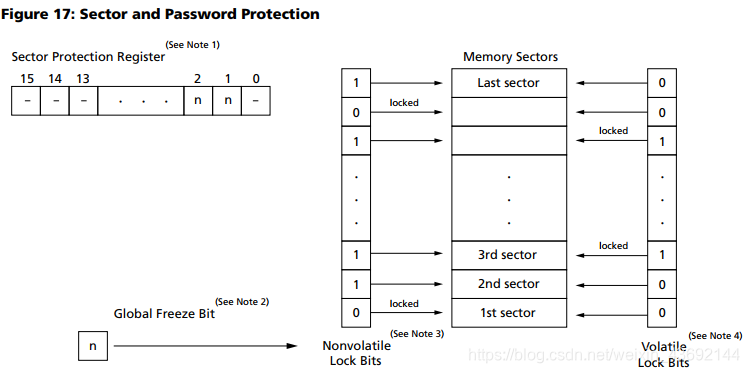

安全寄存器使用非易失性和易失性寄存器及位设置(如下所示)在多个级别上启用扇区和密码保护。 适用的寄存器表如下。

注释:

1.扇区保护寄存器。 该16位非易失性寄存器包括两个有效位[2:1],以启用扇区和密码保护。

2.全局冻结位。 该易失性位保护所有非易失性锁定位中的设置。

3.非易失性锁定位。 每个非易失性位对应于单个存储器扇区并为其提供非易失性保护,该存储器扇区保持锁定(启用保护),直到将其相应的位清除为1为止。

4.易失的锁定位。 每个易失性位对应于单个存储器扇区并为其提供易失性保护,该存储器暂时锁定(在设备复位或掉电时会清除保护)。

5.第一个和最后一个扇区将在4KB的子扇区级别上具有易失性保护。 这些扇区中的每个4KB子扇区都可以通过易失性锁定位设置分别锁定。 非易失性保护的粒度保持在扇区级别。

部门保护安全寄存器

| 位 | 名称 | 设置 | 功能描述 | 注释 |

| 15:3 | Reserved | 1 = Default | - | |

| 2 | Password protection lock | 0 = Enabled 1 = Disabled(Default) | 非易失性位:设置为1时,禁用密码保护。 设置为0时,密码保护会永久启用;无法检索或重置64位密码。 | 1,2 |

| 1 | Sector protection lock | 0 = Enabled, without password protection 1 = Enabled, with password protection(Default) | 非易失性位:设置为1时,可以将非易失性锁定位设置为锁定/解锁其相应的存储扇区; 可以将位2设置为0,以永久启用密码保护。 当设置为0时,可以将非易失性锁定位设置为锁定/解锁其相应的存储扇区; 位2必须保持设置为1,永久禁用密码保护。 | 1,3,4 |

| 0 | Reserved | 1 = Default | - |

注释:

1.位2和1是用户可配置的,可以一次编程,并且互斥,因为它们中只有一个可以设置为0。建议在第一次对该设备编程时将其中一个设置为0。

2.必须对此位设置为0之前对64位密码进行编程和验证,因为在设置该位后,不允许更改密码,从而提供了免受恶意软件攻击的保护。当此位设置为0时,需要64位密码才能将全局冻结位从0重置为1。此外,如果密码不正确或丢失,则不能再设置全局冻结位,并且非易失性锁定位无法更改。 (请参阅“扇区和密码保护”图和“全局冻结位定义”表)。

3.无论该位设置为1还是0,它都可以编程或擦除非易失性锁定位(提供存储器扇区保护)。必须预先设置密码保护位,因为设置该位将永久启用密码保护(位2 = 0)或永久禁用密码保护(位1 = 0)。

4.默认情况下,设备出厂时所有扇区均处于解锁状态。扇区被锁定,解锁,读取或锁定,如非易失性和易失性锁定位表和易失性锁定位寄存器位定义表中所述。

全局冻结位

| 位 | 名称 | 设置 | 功能描述 |

| 7:1 | Reserved | 0 | 0 |

| 0 | Global freeze bit | 0 = Enabled 1 = Disabled(Default) | Volatile bit:当设置为1时,所有的非易失锁定位都可以设置为开启或关闭对应内存扇区的锁定。 当设置为0时,非易失锁定位将被保护,不受PROGRAM或ERASE命令的影响。在非易失性锁定位被置1之前,不应该将该位设置为0。 |

注释:

READ GLOBAL FREEZE BIT命令用来开启读取该位。当密码保护启用时,该位在设备上电或重置时被锁定。没有密码不能修改。输入密码后,UNLOCK password命令将该位重置为1,启用编程或擦除非易失锁定位。

当位被改变后,WRITE GLOBAL FREEZE BIT命令将该位设置为0,保护非易失锁定位不受PROGRAM或ERASE操作的影响。

Nonvolatile and Volatile Sector Lock Bits Security

| 位详情 | 非易失锁定位 | 易失锁定位 |

| 描述 | 内存的每个扇区有一个对应的非易失锁定位 | 内存的每个扇区有一个对应的volatile锁位;这是在Volatile锁位寄存器表中描述的扇区写锁位。 |

| 功能 | 当设置为0时,锁住并保护其对应的内存扇区不受PROGRAM或ERASE操作的影响。因为这个位是不易失的,所以扇区保持锁定状态,启用保护,直到该位被清除为1。 | 当设置为1时,锁住并保护其对应的内存扇区不受PROGRAM或ERASE操作的影响。因为这个位是不稳定的,所以保护是暂时的。当设备复位或下电时,扇区解锁,保护关闭。 |

| 设置 | 1 = 禁止锁 0 = 使能锁 | 0 = 禁止锁 1 = 使能锁 |

| 使能保护 | 该位通过WRITE NONVOLATILE LOCK BITS命令设置为0,表示启用对指定锁定扇区的保护。扇区锁定位的编程需要典型的字节编程时序。 | 该位由WRITE VOLATILE LOCK BITS命令设置为1,表示启用对指定锁定扇区的保护。 |

| 禁止保护 | 所有位被ERASE NONVOLATILE LOCK bits命令清除为1,同时解锁和禁用所有扇区的保护。清除所有扇区锁定位需要典型的扇区清除时间。 | 在复位或下电时,所有位设置为0,解锁和禁用所有扇区的保护。 |

| 对该位 | 位由read NONVOLATILE LOCK Bits命令读取。 | 位由read VOLATILE LOCK Bits命令读取 |

Volatile Lock Bit Security Register

一个易失性锁位寄存器与内存的每个扇区相关联。使用WRITE VOLATILE LOCK BITS命令使扇区被锁定、解锁或锁定,该命令只在扇区锁定(第1位)设置为0时执行。每个寄存器都可以用read VOLATILE LOCK BITS命令读取。这个寄存器是兼容的,并提供相同的锁定能力,作为锁寄存器在Micron N25Q SPI NOR家族。

| 位 | 名称 | 设置 | 功能描述 |

| 7:2 | Reserved | 0 | 0 |

| 1 | Sector lock down | 0 = 禁止锁(默认) 1 = 使能锁 | 易失性位:设备总是将该位设置为0,以便扇区锁定和扇区写锁定位可以设置为1。当这个位设置为1时,这两个不稳定的锁定位都不能被写入,直到下一个电源周期,硬件或软件重置。 |

| 0 | Sector write lock | 0 = 禁止写锁(默认) 1 = 使能写锁 | 易失性位:设备总是将此位设置为0,以便执行此扇区中的PROGRAM和ERASE操作并修改扇区内容。当这个位设置为1时,这个扇区中的PROGRAM和ERASE操作不会被执行。 |

感觉bit1就是控制bit0的,很鸡肋(bit0可以自己使能或禁止写锁)。

1425

1425

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?