基于xilinx7 Artix xc7a35t 的FPGA开发日记(二)

我们这次来讲讲时序电路设计的基本步骤,完成这节之后我们就可以开始讲述FPGA的开发了,请各位看官耐心看完本节~

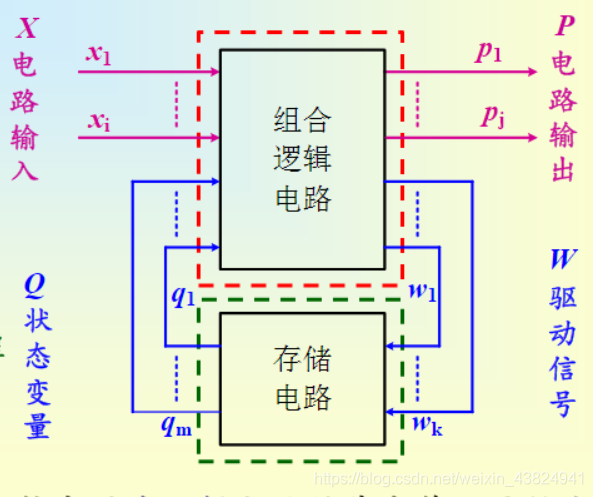

时序电路简单来说就是组合逻辑电路加上存储电路,常见的时序电路的基本单位由触发器构成,触发器的特点有:1.大部分触发器都有时钟源 2.触发器的下一个时刻的输出与上一时刻有关。常见的时钟触发器有时钟RS触发器,D触发器,JK触发器,还有T以及T’触发器。大家可以在上一节推荐的教材中找到详细的介绍。

时序电路又分为同步、异步。由于异步电路设计极为复杂,没有固定的设计方法,在这里我们只介绍同步时序电路的设计。

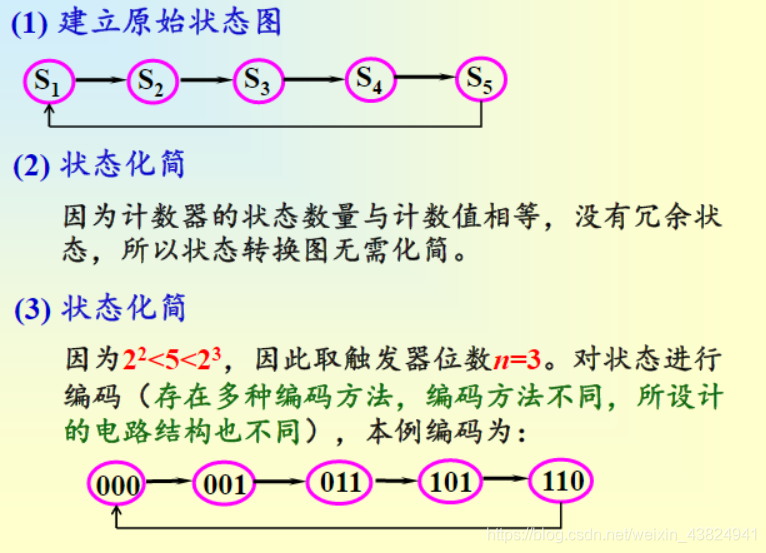

这里以有D触发器构成五进制计数器来说明

首先我们确定计数器的五个状态对应的编码。我们知道我们触发器总共需要与技术长度一样的状态,一个触发器有两个状态,4<5<8,所以我们向上补一用3个触发器来完成设计。

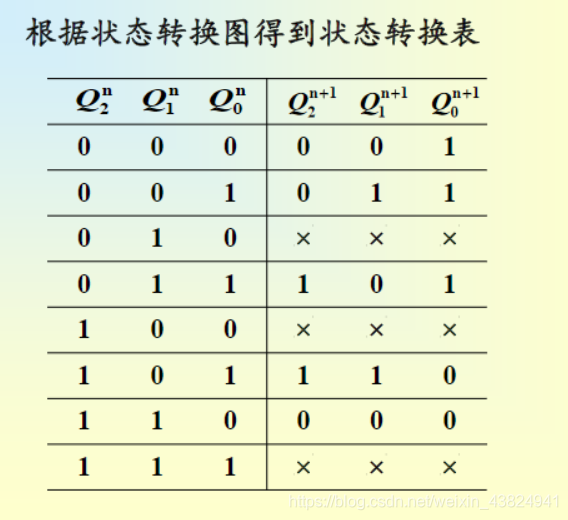

此时我们假设初态为000,列出状态转换表

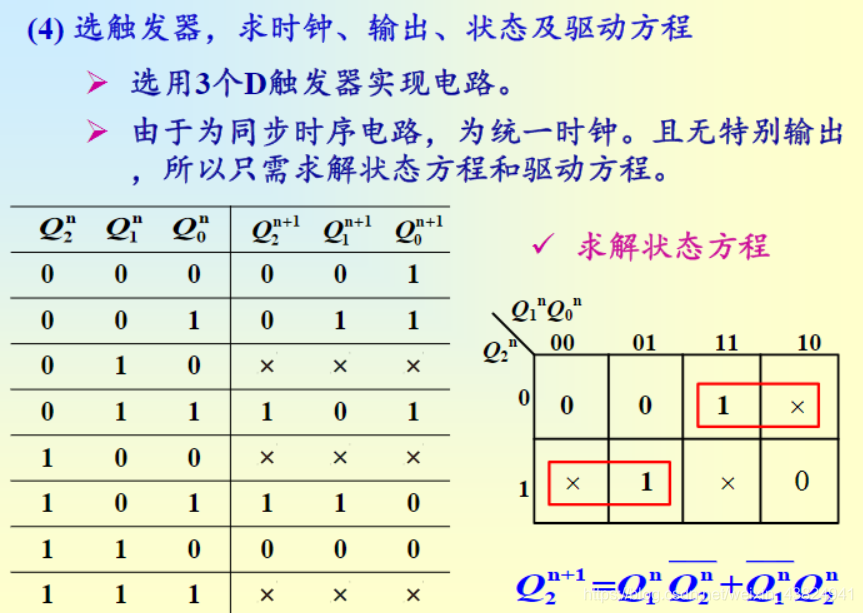

然后用跟组合逻辑一样的化简方法化解出驱动方程和状态方程。

在实际开发中,还要检查电路的自启动问题,即从初态开始是否能进入循环。

之后就画出时序电路图就完成了。

有兴趣的朋友可以尝试着设计一个“串行1101序列检测器”,我会在下次发布博客的时候附上说明和仿真文件供大家参考。

谢谢观看。

【1】图片来自哈尔滨工业大学(威海)信息学院的王永玲老师,侵删。

4361

4361

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?