I2C总线的上拉电阻计算

概述

对于I2C总线,由于使用OD/OC驱动,因此需要借助上拉电阻建立高电平。对于上拉电阻的选择,主要由以下因素影响。

- 总线的负载电容

- 总线的速度

- 总线的驱动电压

- 总线的低电平阈值

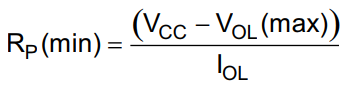

上拉电阻的下限

上拉电阻不能无限制的小,不妨想象一种极端情况,当上拉电阻为0.00001R时,此时为了达到总线的低电平阈值,电阻上所承受的压降约等于电源电压-低电平阈值,此时电阻需要的电流时十分巨大的,因此上拉电阻的下限受到三个因素的影响。

- 总线的电压 VCC

- 总线的低电压阈值 VOL

- 总线上所有设备中,IO灌电流最低的设备的灌电流(流入IC的电流) IOL

根据这三个值就可以计算出上拉电阻的下限

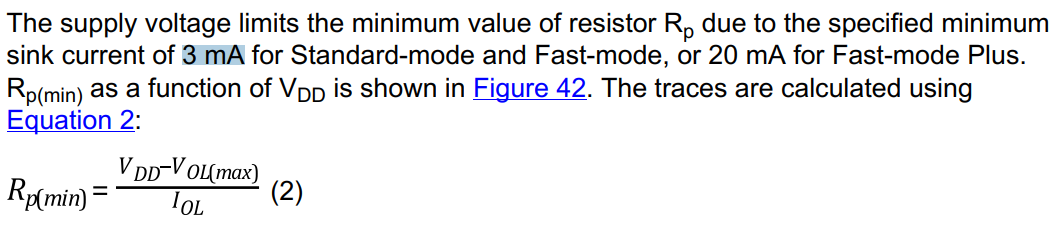

总线的电流要求

在NXP的手册中,对不同速度等级的总线的灌电流(sink current)做了不同的要求

实际使用中还是要根据具体的器件手册评估器件的灌电流。

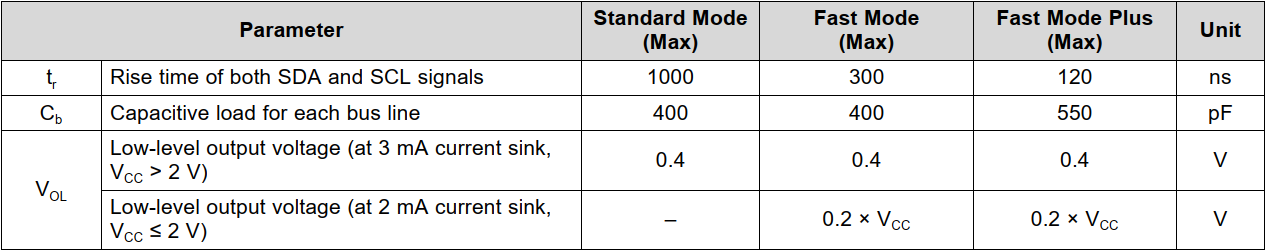

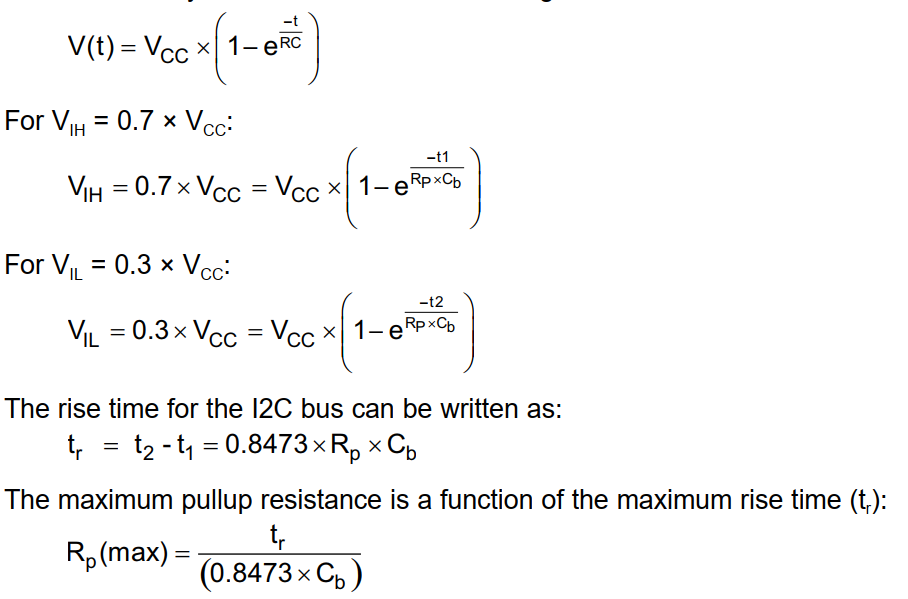

上拉电阻的上限

上拉电阻不能无限制的大,因为总线是有驱动速度的需求的,由于总线存在分布电容、输入接口也存在寄生电容,假设总线上的MOS或晶体管是能瞬间截止的,此时总线上的电压可以看做是一个标准的RC充电模型。此时电压的上升时间与两个值有关,总线的上拉电阻,总线的负载电容。

因此总线的上拉电阻的上限,受到总线的负载电容和速度等级的限制

I2C总线对于负载上升时间的定义

I2C总线的上升时间是按照30%-70%的电压上升时间定义的。

对于不同速度等级的I2C总线,上升时间有不同的要求。具体要求见表格

因此,上拉电阻的上限可以按照下式计算

实际应用中

在实际的应用中,决定电阻的所有变量中,总线的负载电容很难精确地计算,只能大致的估计范围。因此通常在应用中,一般是根据估计和经验选择一个临时上拉电阻,然后根据波形的测试效果去选择合适的电阻。在一些系统中,假设10k,4.7k,2k电阻都能满足要求,那么就要在速度和功耗中按照设计需求进行取舍,上拉电阻越大意味着功耗越低,同时要牺牲部分上升时间。上拉电阻小意味着功耗高,同时意味着总线的扩展能力更强,在多板卡I2C互联时要尤其注意上拉电阻的设计问题。

- 当波形上升边缓慢的时候,需要减小上拉电阻。

- 当波形低电平无法降低到VOl以下时,需要增加上拉电阻。

- 当上拉电阻已经调整到一个很小的水平,但是依然无法满足总线的时序要求时可以增加总线中继。分担总线的负载电容,重新调整上拉电阻。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?