数字集成电路与系统设计基础知识(一)

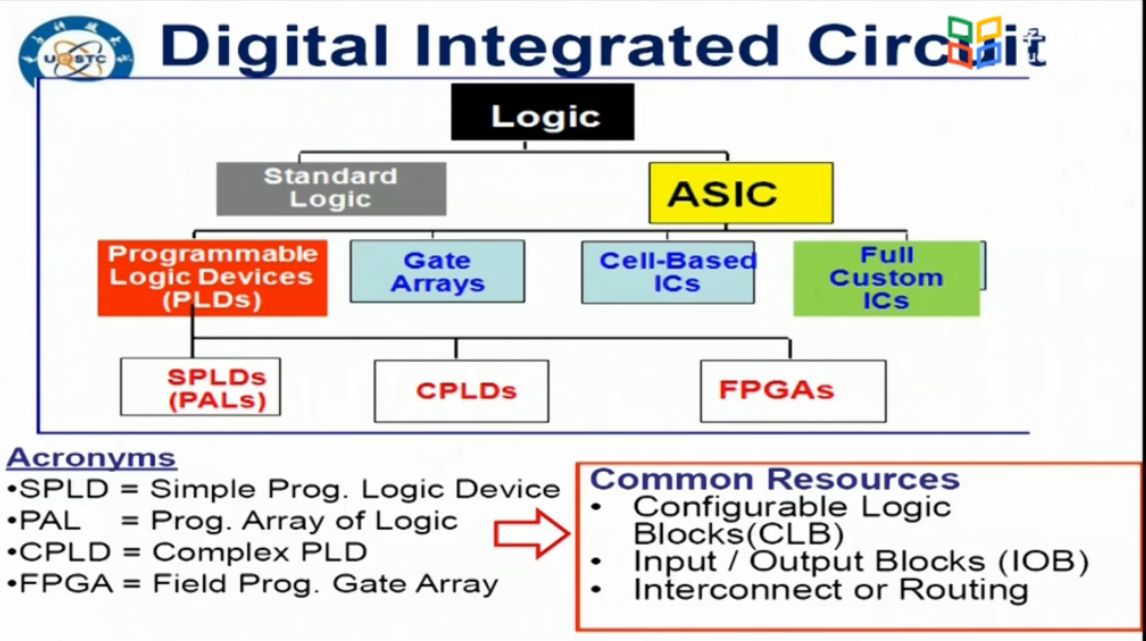

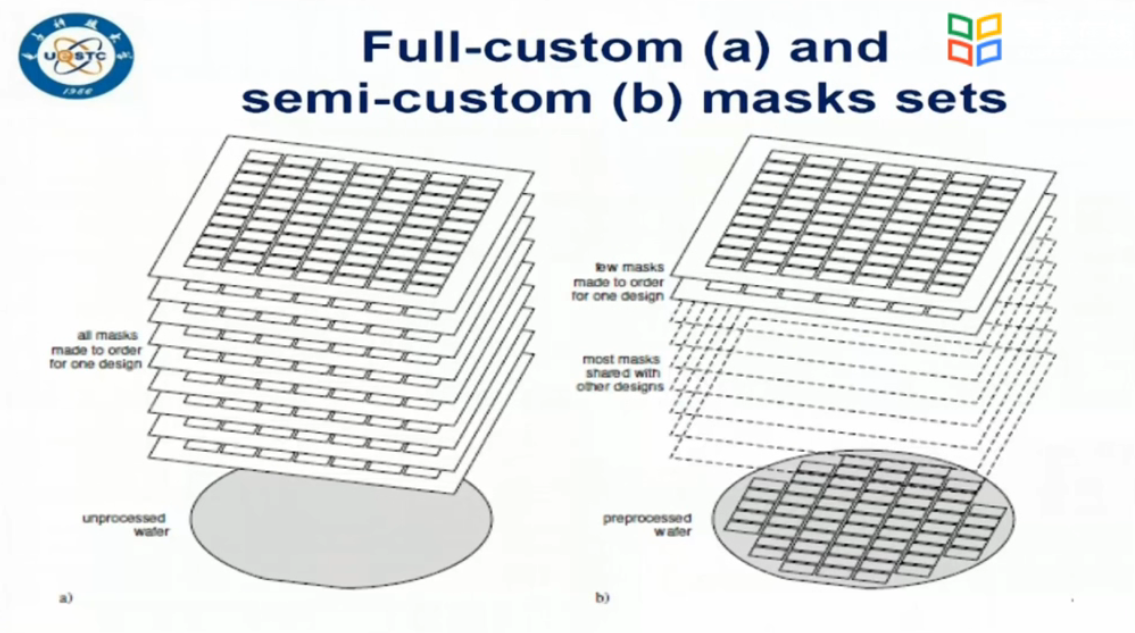

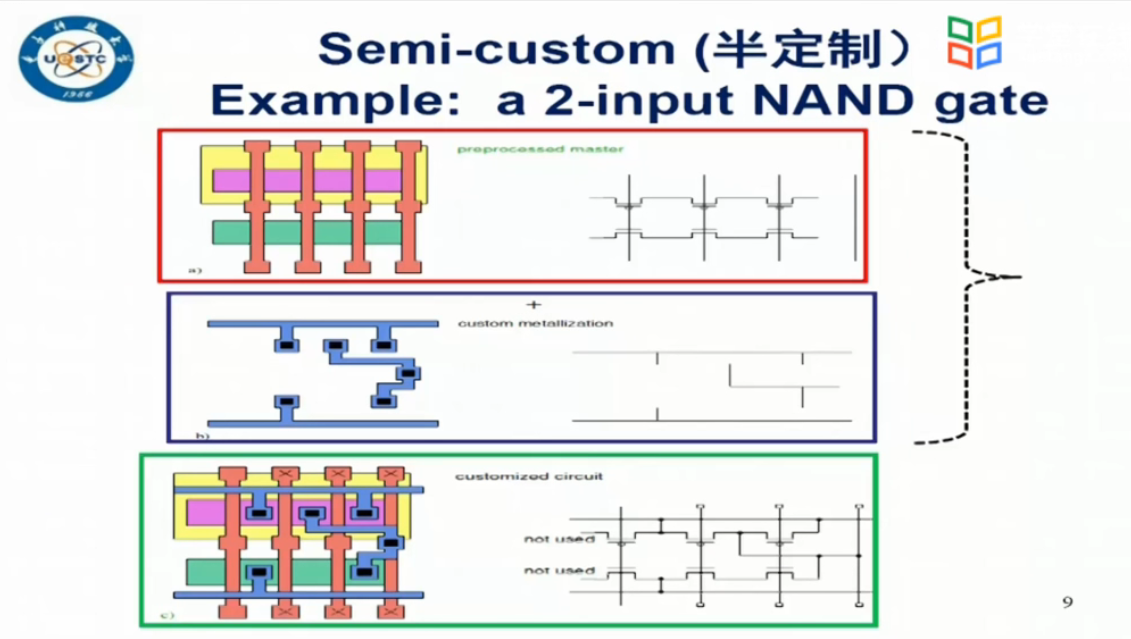

ASIC可分为全定制和半定制。

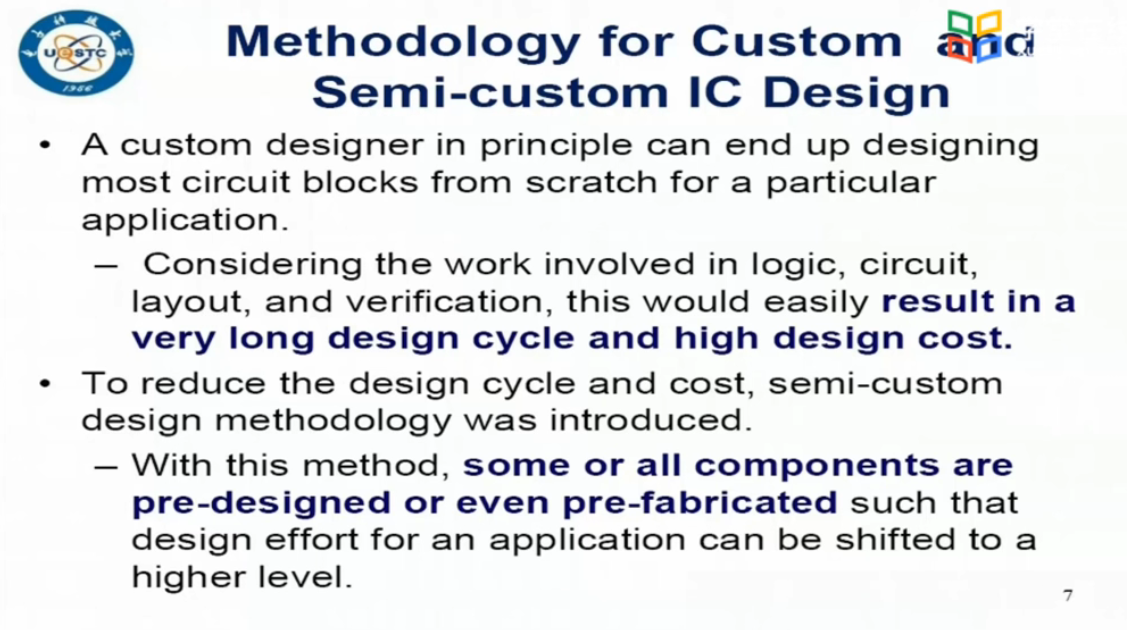

半定制是调配厂家的设计资源(库单元),全定制是全部自己做。

from scratch:白手起家、从头开始。

such that:使得;这样。

design effort:可理解为设计工作。

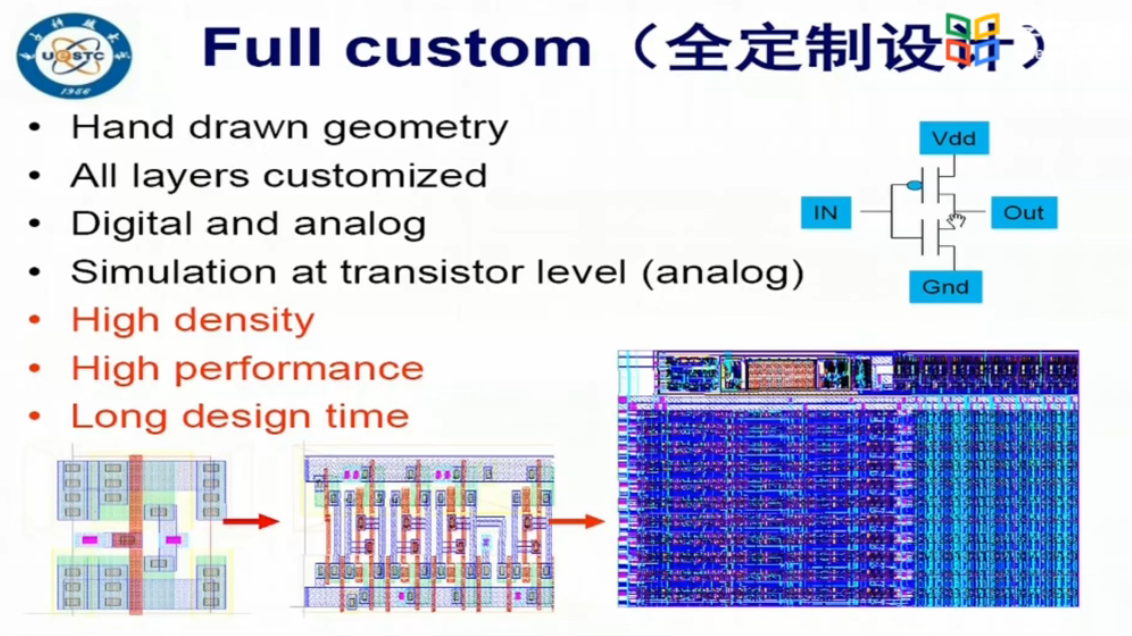

手绘Geometry(在光掩模上成像的预期图案);

所有层定制;(构成设备的一系列重叠光掩模或光掩模图像中的一个)

数字和模拟;

晶体管级仿真(模拟);

高密度;

高性能;

设计时间长。

PS:对密度的理解

-

光掩模上图案与无图案区域的相对程度,如电路密度(circuit density)

-

给定尺寸下允许的缺陷数,如缺陷密度(defect density)

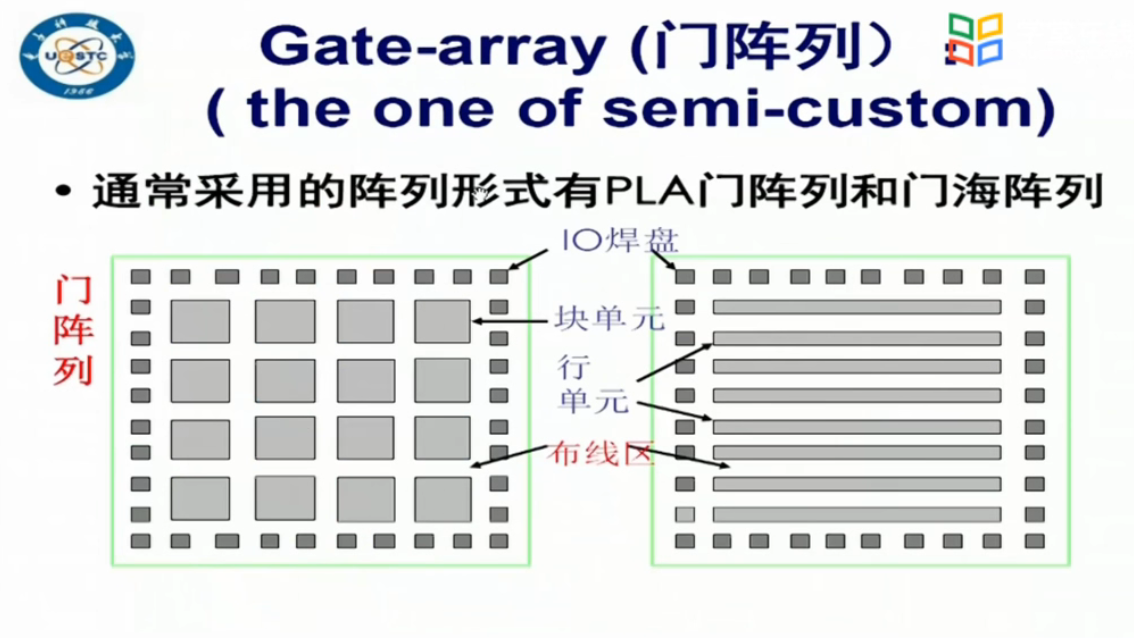

门阵列:只需要连接现成的门。

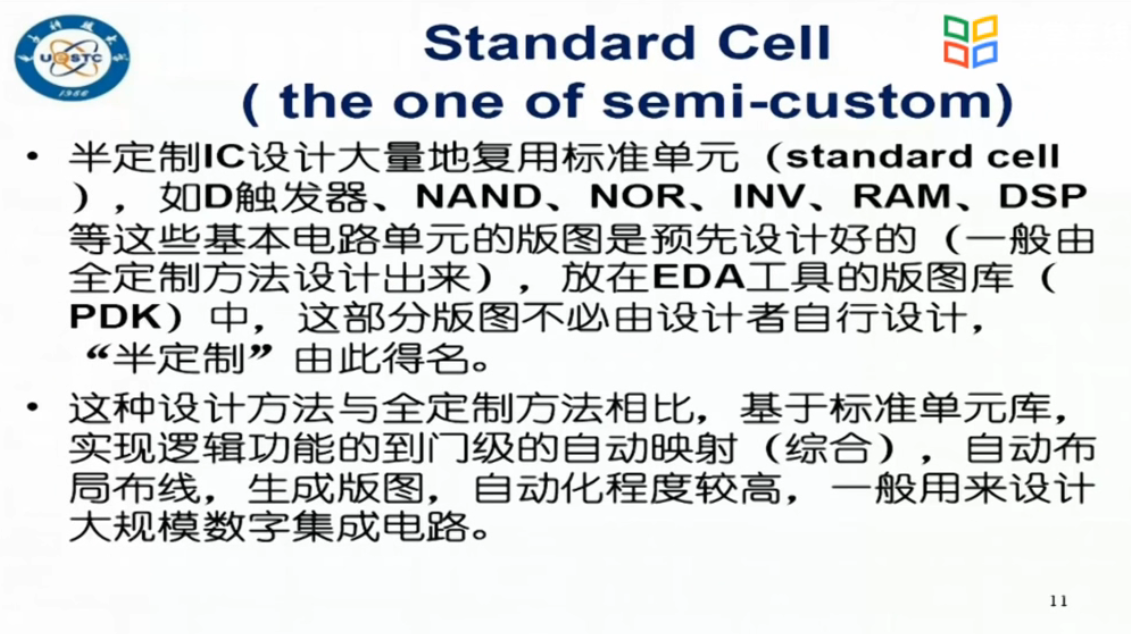

标准单元库:直接用厂家写好的lib库。

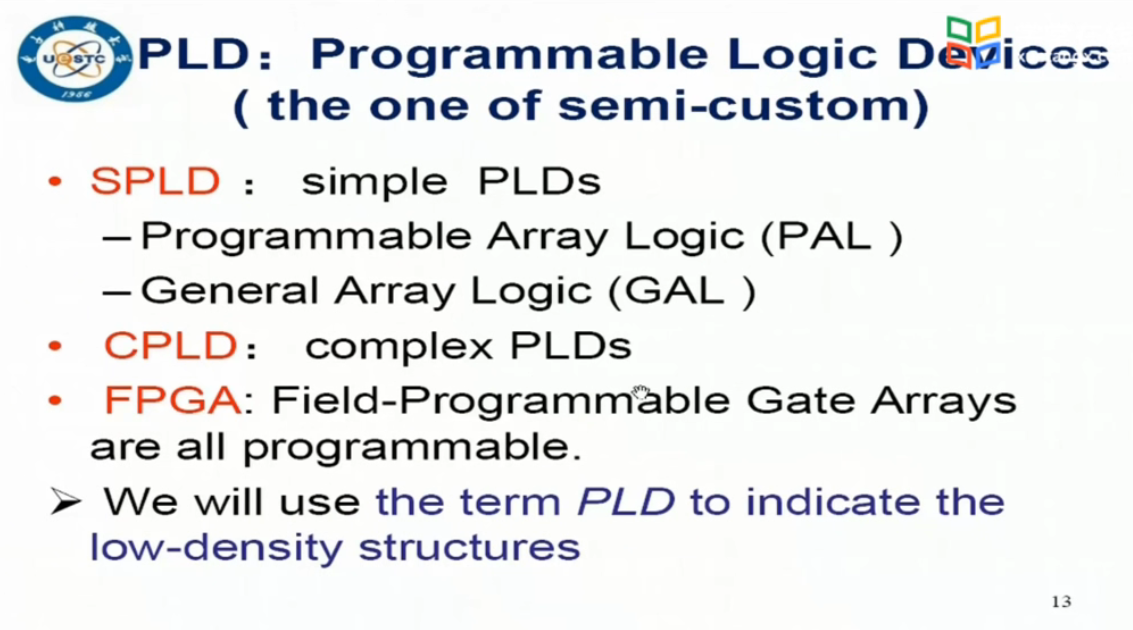

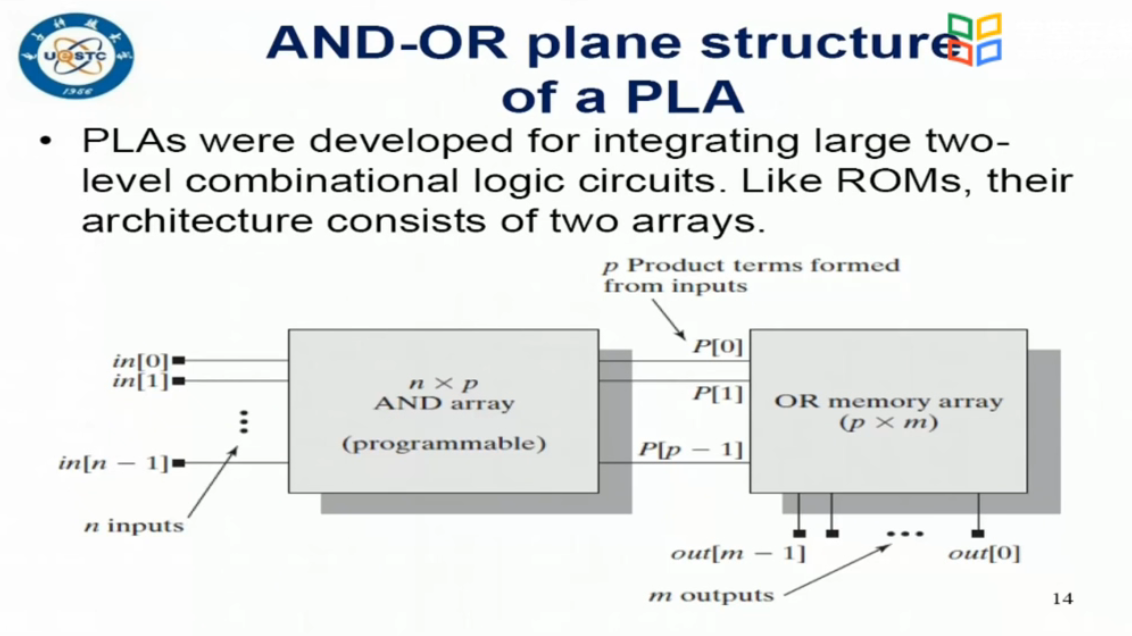

PLD:可编程逻辑器件,使用术语PLD来表示低密度结构。

<

<

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?