关键词:

TriCore TC1.6.2;TC1.6.2架构手册;TC1.6.2 System Registers;TC3XX系统寄存器;TC397架构手册;

简介:

本篇为英飞凌TC1.6.2架构手册第三章翻译 - General Purpose and System Registers

手册适用于TC3XX(包括TC397)芯片

官方架构手册下载链接:

目录

3.系统和通用寄存器

TriCore内核寄存器有两种类型:

通用寄存器 - General Purpose Registers (GPRs)

内核特殊功能寄存器 - Core Special Function Registers (CSFRs)

通用寄存器包含16个数据寄存器以及16个地址寄存器,内核特殊功能寄存器控制内核运行,同时提供内核相关的状态信息,内核寄存器大致可分为如下几种类型:

-

通用寄存器

-

系统寄存器:

PSW、PC、PCXI -

堆栈管理寄存器:

A[10]、ISP -

SYSCON、CPU_ID寄存器 -

Trap寄存器 -

上下文管理寄存器

-

内存保护寄存器

-

调试寄存器

-

浮点寄存器

-

内核相关的特殊功能寄存器

复位值

架构手册只给出了部分通用的复位值,未给出的需要参考各个平台的具体实现

ENDINIT保护

TriCore架构支持在用户程序运行之前进行预初始化

预初始化阶段,可以使用MTCR指令修改所有的内核特殊功能寄存器CSFR

用户程序执行阶段,仅部分内核特殊功能寄存器可以通过MTCR指令修改,其他指令不受影响

这种CSFR仅在预初始化阶段可写入的行为称为ENDINIT保护,从预初始化阶段过渡至用户程序执行阶段的方式依照各具体的平台实现,ENDINIT保护使得CSFR仅在预初始化阶段可被修改,从而为关键的CSFR提供额外的保护,如下几个CSFR受ENDINIT保护:

-

BTV、BIV、ISP、PMA0、PMA1、PMA2、PCON0、DCON0、SEGEN

TriCore架构提供了安全版本的ENDINIT保护,如下几个寄存器受到SAFETY_ENDINIT保护:

-

SMACON、SYSCON、COMPAT、TPS_EXTIM_ENTRY_LVAL、TPS_EXTIM_EXIT_LVAL

3.1.通用寄存器 - GPR

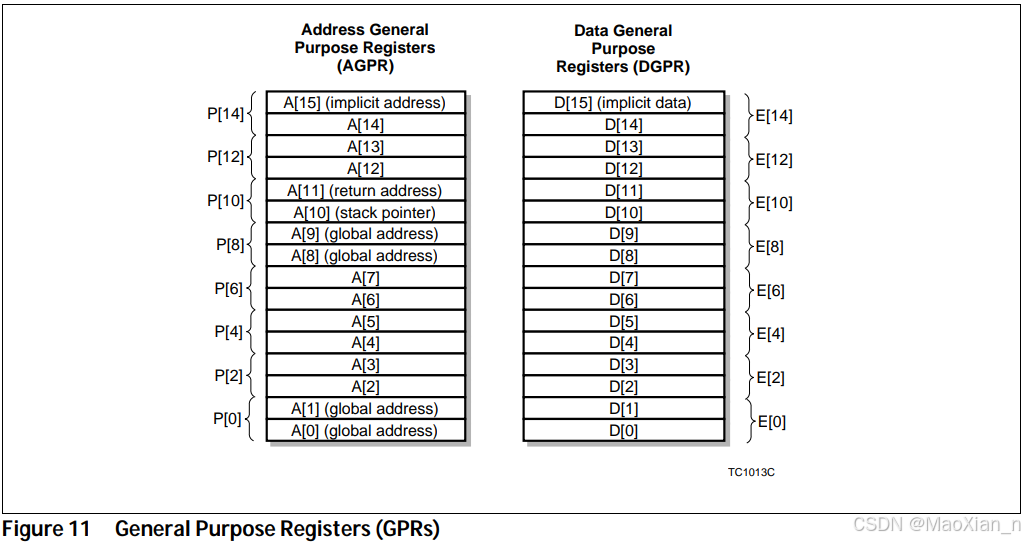

通用寄存器GPR分为数据寄存器和地址寄存器:

-

16个数据寄存器DGPR:D[0]~D[15] -

16个地址寄存器AGPR:A[0]~A[15]

数据寄存器和地址寄存器分离的设计,使算数运算和地址运算得以并行执行,从而提升芯片的运行效率,一些指令被允许在数据寄存器和地址寄存器之间交换信息(例如创建或获取索引表),数据寄存器可以按相邻两个为一组的方式,构成8个扩展大小的寄存器E[0]、E[2]、E[4]、E[6]、E[8]、E[10]、E[12]、E[14],从而可以支持64-bit宽度的数据,地址寄存器也可以按照相同的方式构成P[0]、P[2]、P[4]、P[6]、P[8]、P[10]、P[12]、P[14]

-

A[0]、A[1]、A[8]、A[9]被定义为系统全局寄存器,其中的值不由CALL指令、Trap或者Interrupt保存或恢复 -

A[10]为栈指针SP -

A[11]保存调用指令CALL和跳转指令的返回地址,中断或Trap中保存将要返回的PC -

许多

16位的指令隐式的使用A[15]作为地址寄存器,D[15]作为数据寄存器

通过将相邻两个32位寄存器构成一对的方式支持64位指令,汇编语法中这些寄存器称为32位寄存器对或扩展64位寄存器,例如D[8]/D[9]寄存器对(E8寄存器为D[8]和D[9]的串联,D[8]为E[8]的最低有效字或者低32位)

为了支持扩展地址模式,相邻的一奇一偶两个32位寄存器构成寄存器对,用于保存扩展的地址值,如A[8]/A[9]寄存器对

TriCore架构没有单独的浮点寄存器,通用数据寄存器GPR也用于浮点数计算,浮点数据使用自动上下文切换,支持自动保存和恢复

GPR是任务上下文切换的必要部分,保存或恢复任务的上下文时会将其分为上半部分和下半部分:

-

Lower Context:A[2]~A[7]、D[0]~D[7] -

Upper Context:A[10]~A[15]、D[8]~D[15]

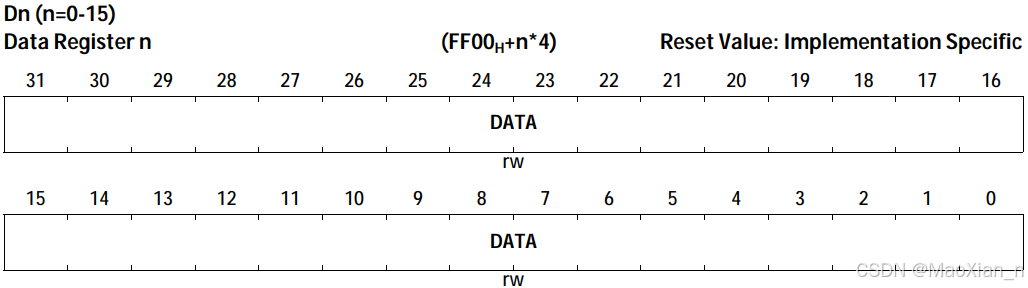

通用数据寄存器

-

DATA:Data Register n Value,数据

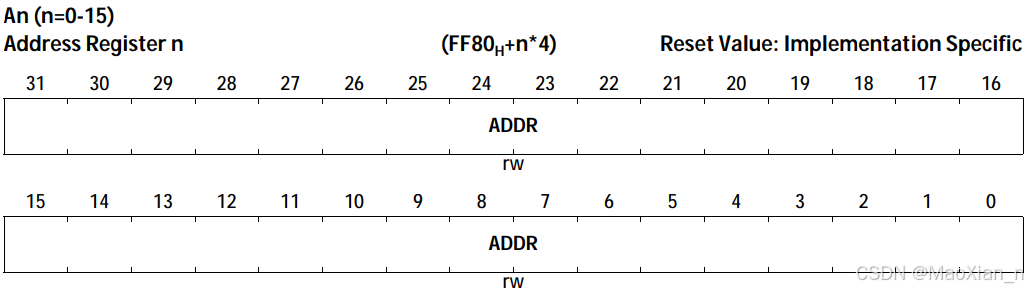

通用地址寄存器

-

ADDR:Address Register n Value,地址

3.2.程序状态信息寄存器

PC、PSW、PCXI三个寄存器保存程序状态相关信息,在保存、恢复以及修改任务内容的过程中,这些寄存器是保存和恢复任务上下文的重要组成部分

-

PC:程序计数器 -

PSW:程序状态字 -

PCXI:之前上下文信息

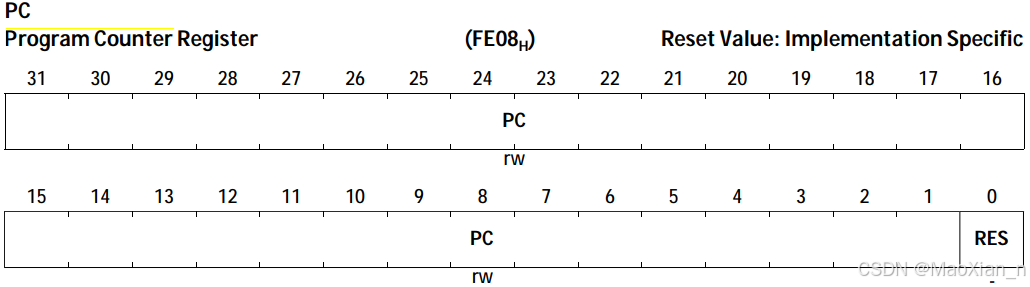

程序计数器 - PC

指向当前正在执行的指令(保存当前正在执行指令的地址),PC是任务状态信息的一部分,修改PC指针需要在内核处于Halt状态时进行,内核运行时修改指针无效

-

PC:Program Counter,当前正在执行指令的地址

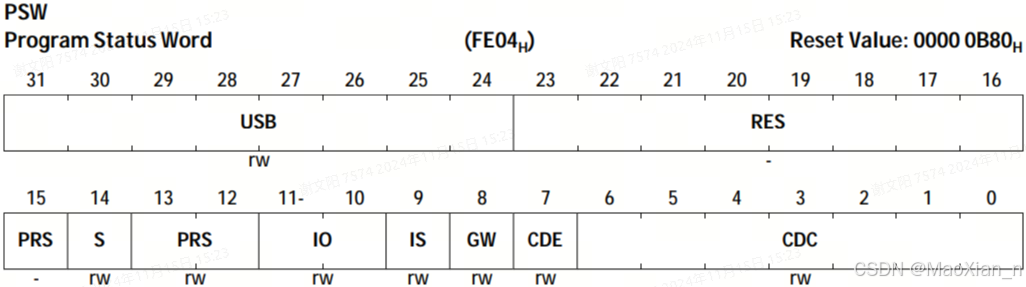

程序状态字 - PSW

PSW寄存器包含了通用寄存器GPR中没有记录,且特定于任务的状态信息,其下半部分(Lower Half)包含了保护系统相关的控制参数,包括:

-

PRS:保护寄存器组 -

IO:I/O特权等级 -

IS:中断栈标志 -

GW:全局寄存器写入允许标志 -

CDC:调用深度计数器 -

CDE:调用深度计数使能位

-

USB:User Status Bits,用户指令会设置或清除这些标志,具体位含义如Table 6所示 -

PRS[2]:Protection Register Set bit[2] ,选择活动的数据和代码内存保护寄存器组,内存保护寄存器控制当前进程的加载、保存和指令提取,最多支持8个寄存器组 -

S:Safety Task Identifier,当前任务应该被标记为安全任务(Safety Task) -

PRS[1:0]:Protection Register Set bits[1:0] ,选择活动的数据和代码内存保护寄存器组 -

IO:Access Privilege Level Control (I/O Privilege),控制CSFR和外设的访问权限-

00B:User-0 Mode,禁止访问外设,禁止访问包含外设内存空间的内存,否则导致PSE或者MPPTrap -

01B:User-1 Mode,常规访问外设,允许访问未受保护的普通外设,包括读写串行I/O端口、读取定时器和大部分I/O状态寄存器,任务处于该级别时可以禁用中断(系统控制寄存器可以覆盖该模式的默认行为) -

10B:Supervisor Mode,允许访问所有外设,允许对核心寄存器及受保护的外设进行读写访问,任务处于该运行级别时可以禁用中断 -

11B:保留值,未使用

-

-

IS:Interrupt Stack Control,决定当前执行线程使用全局共享(中断)栈或者用户栈-

0:User Stack,如果中断产生时PSW.IS位为0,则在中断服务例程ISR的第一条指令开始执行之前,堆栈指针寄存器将从ISP加载 -

1:Shared Global Stack,如果中断产生时PSW.IS位为1,则中断服务例程ISR使用当前堆栈指针

-

-

GW:Global Address Register Write Permission,决定当前执行线程是否有权限修改全局地址寄存器,大部分Task和ISR将全局地址寄存器用作Read Only寄存器,指向全局Literal Pool和关键数据结构,但是Task和ISR也可以被指定为某个全局地址寄存器的Owner,并且允许对该寄存器进行修改,系统设计者必须确定哪些全局地址寄存器的使用频率较高,以及该寄存器有足够的独占时间提供给紧迫的任务/代码,从而确定有必要为其分配全局地址寄存器,按照编译器的习惯,全局地址寄存器A[0]被保留用作临时的加载/存储,寄存器A[1]保留给编译器使用,编译器未使用寄存器A[8]和A[9],这两个寄存器可用于保存关键的系统地址变量-

0:禁用寄存器A[0]、A[1]、A[8]、A[9]的写入权限 -

1:使能寄存器A[0]、A[1]、A[8]、A[9]的写入权限

-

-

CDE:Call Depth Count Enable,使能调用深度计数,前提是PSW.CDC没有全部置1-

0:暂时禁用调用深度计数,会在下一条Call指令执行完后自动打开(Re-Enable) -

1:使能调用深度计数,如果PSW.CDC = 1111111B,则无论PSW.CDE为何值,都会禁用调用深度计数

-

-

CDC:Call Depth Counter,由两个宽度可变的字段组成,第一个字段由多个0和1组成字符串,以0结尾,其余位为第二个字段CDC.COUNT,构成调用深度计数值,每次调用时递增,返回时递减-

0CCCCCCB: 6-bit counter; trap on overflow -

10CCCCCB: 5-bit counter; trap on overflow -

110CCCCB: 4-bit counter; trap on overflow -

1110CCCB: 3-bit counter; trap on overflow -

11110CCB: 2-bit counter; trap on overflow -

111110CB: 1-bit counter; trap on overflow -

1111110B: Trap every call (call trace mode) -

1111111B: Disable call depth counting -

调用深度

CDC.COUNT溢出时会产生CDO Trap,将CDC设置为1111110B时计数器无有效存储位,此时每条Call指令都会被捕获(用于追踪调用深度),将CDC设置为1111111B会禁用调用深度计数

-

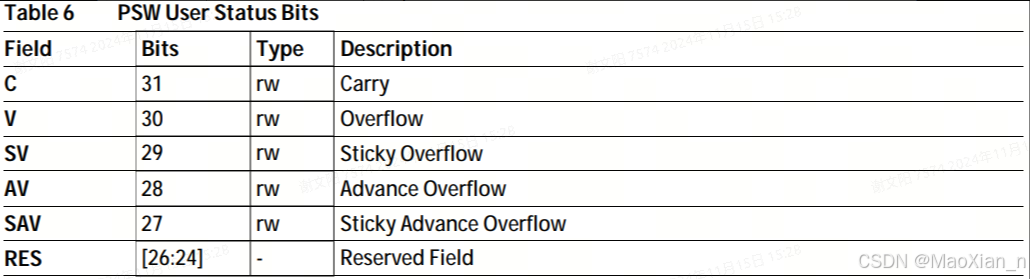

PSW用户状态位

PSW寄存器最高的8位被指定为用户状态位,用户指令会设置或清除相关位,通常用于记录指令执行结果的状态,单独的位也可用于调整部分指令的操作,例如Add Extended(ADDE)和Add with Carry(ADDE)指令使用第31位记录ADD操作的执行情况,以及该位在指令执行前的值会反映在ADDC指令的执行结果中

有两类用户指令使用用户状态位:

-

可能产生进位和溢出结果的算数指令

-

特定于实现的协处理器指令,可以使用全部的

8位,使用方式取决于该指令的具体实现

PSW的[23:16]为保留位,系统复位后通过MFCR(Move From Core Register)指令读取PSW时这些位的值为0,通过MTCR(Move To Core Register)指令写入PSW时,应向其写入0

访问权限等级控制 - I/O权限

软件任务管理(Software Managed Tasks, SMTs)由实时内核或操作系统的服务创建,并在调度软件的控制下调度,中断服务例程(Interrupt Service Routines, ISRs)在响应中断时由硬件调度,ISR是处理器在接收到中断时直接调用的代码,SMT有时称为用户任务,因为它们是在用户模式下执行的

每个任务依据任务的相关函数分配了对应的模式:

-

User-0 Mode:用于无需访问外设的任务,该模式下无法使能或禁用中断 -

User-1 Mode:用于访问普通、无保护外设的任务,通常是读取或写入串行端口,读取定时器和大部分I/O状态寄存器,该模式下的任务可以禁用中断(系统控制寄存器可以覆盖该模式的默认行为) -

Supervisor Mode:允许读/写系统内存和访问外设,该模式下的任务可以禁用中断

任何任务都与一组状态元素相关联,这些元素统称为任务的上下文,上下文是处理器定义任务状态并使其继续执行所需的一切,其中包括任务使用的CPU通用寄存器、任务的程序计数器PC以及程序状态信息PCXI和PSW,平台通过硬件管理和维护任务的上下文

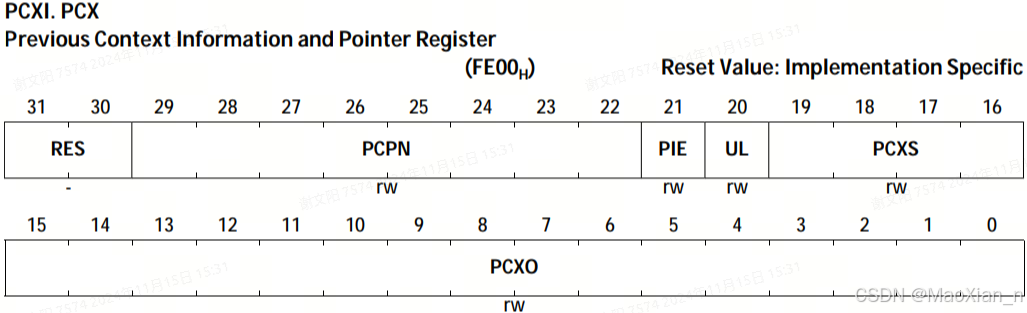

PCXI - 之前上下文信息

之前上下文信息寄存器(Previous Context Information, PCXI)包含了之前执行任务的上下文相关信息,用于中断和自动上下文切换,PCXI是任务状态信息的一部分,之前上下文指针(Previous Context Pointer, PCX)保存之前任务的Context Save Area(CSA)地址

-

PCPN:Previous CPU Priority Number,包含中断任务的优先级编号 -

PIE:Previous Interrupt Enable,指示中断任务的中断使能位ICR.IE的状态 -

UL:Upper or Lower Context Tag,指示已保存上下文的类型,如果执行上下文恢复时类型不匹配则生成Trap-

0:Lower Context -

1:Upper Context

-

-

PCXS:PCX Segment Address,和PCXO一起使用, 保存PCX的段地址 -

PCXO:Previous Context Pointer Offset Field,PCXO和PCXS组成PCX指针,指向之前上下文的CSA

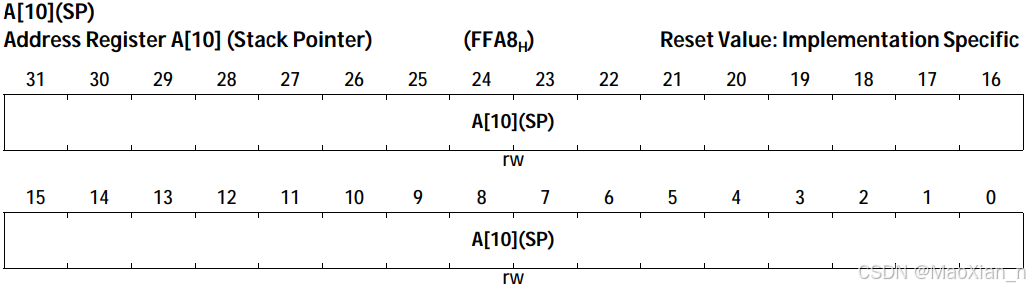

3.3.栈管理寄存器

TriCore架构的栈管理支持一个用户栈和一个中断栈,栈管理会用到地址寄存器A[10]、中断栈指针ISP和PSW寄存器中的一位

-

A[10]用作栈指针,初始值一般由RTOS创建Task时提供,同时允许为每个Task分配专用的堆栈区域 -

ISP用于防止中断服务例程ISR访问专用堆栈区域,从而避免干扰普通用户程序的上下文,TriCore架构支持处理中断前将堆栈由用户堆栈自动切换至ISP -

PSW.IS位指示了中断发生时具体使用哪个堆栈

在处理中断且需要使用中断专属的堆栈时(PSW.IS == 0),会保存用户堆栈的内容以及被中断任务的上下文,随后加载A[10](SP)以及ISP堆栈(从用户程序进入中断服务程序)

在处理中断或Trap,且已产生的中断任务正在使用专用堆栈(PSW.IS == 0)时,不会再次加载A[10](SP),中断服务例程ISP继续使用当前堆栈,但保留其中已入栈的值(中断嵌套)

一般只需要在预初始化阶段初始化一次ISP,但是根据应用程序的需要,ISP可以在程序执行时被修改,需要注意的是,没有指令或程序可以阻止ISR或者系统服务例程在专用堆栈上执行

注意:在ISR中使用A[10](SP)由程序员自己决定

栈指针寄存器 - A[10] (SP)

-

A[10] (SP):Address Register A[10] (Stack Pointer),栈指针寄存器

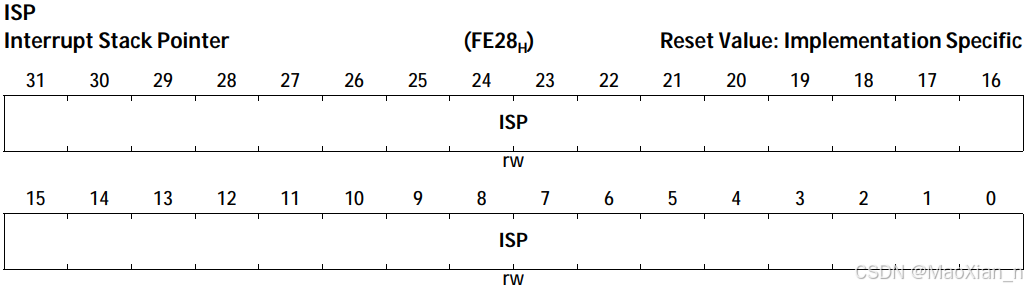

中断栈指针寄存器 - ISP

注意:该寄存器受ENDINIT保护

-

ISP:Interrupt Stack Pointer,中断栈指针寄存器

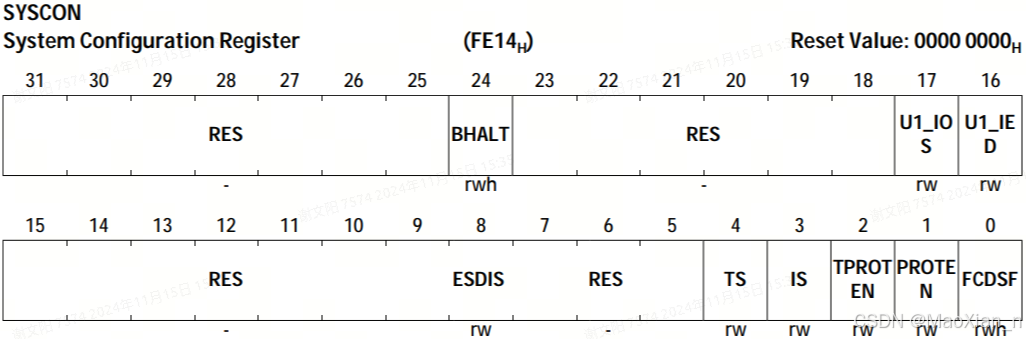

系统控制寄存器 - SYSCON

系统配置寄存器有如下几个功能:

-

时间保护系统(

Temporal Protection System, TPS)使能位 -

内存保护系统使能位

-

中断处理程序中

PSW.S初始状态指示位 -

Trap处理程序中PSW.S初始状态指示位 -

使能

User-1I/O模式外设访问 -

禁用

User-1I/O模式控制中断的权限 -

BootHalt状态和释放位 -

指示空闲上下文列表是否已使用完

注意:除了FCDSF位,该寄存器的其他位均受SAFETY_ENDINIT保护

-

BHALT:Boot halt status and release,CPU复位后可能会立即进入HALT状态,此时BHALT位会置1,在该位置0前CPU会一直保持HALT状态,将该位从1置0后,CPU会从程序定义的PC地址开始执行,手动向该位写1的操作会被忽略 -

U1_IOS:User-1 Peripheral access as supervisor,允许User-1模式下的Task访问外设(如同在Supervisor模式下),使得User-1可以访问所有外设寄存器 -

U1_IED:User-1 Instruction execution disable,User-1I/O模式下禁用User-1模式的指令,禁用User-1使能/禁用中断的能力 -

ESDIS:Emulator Space Disable,禁用内核调试使用的模拟空间 -

TS:Initial state of PSW.S bit in trap handler,Trap执行时PSW.S位的初始状态 -

IS:Initial state of PSW.S bit in interrupt handler,中断执行时PSW.S位的初始状态 -

TPROTEN:Temporal Protection Enable,使能/禁用时间保护系统-

0:禁用时间保护系统 -

1:使能时间保护系统

-

-

PROTEN:Memory Protection Enable,使能/禁用内存保护,该功能由内存保护寄存器组进行控制,初始化内存保护寄存器组之前需要将PROTEN位置1-

0:禁用内存保护 -

1:使能内存保护

-

-

FCDSF:Free Context List Depleted Sticky Flag,用于指示自上次软件清除该位后,是否产生过FCD(Free Context List Depleted)类型的Trap-

0:自上次软件清除该位后,未发生过FCDTrap -

1:自上次软件清除该位后,有FCDTrap产生

-

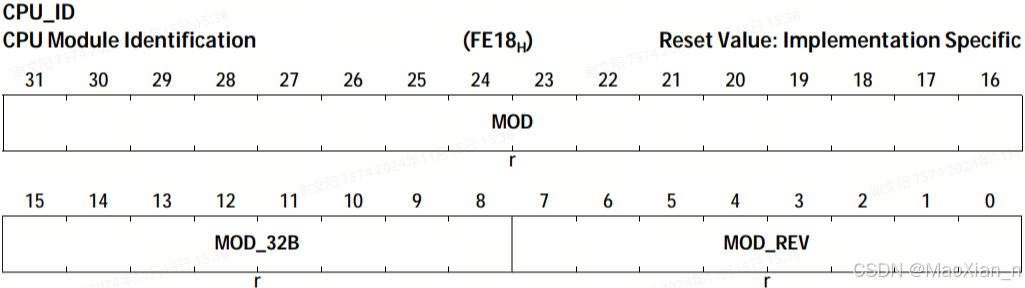

CPU ID寄存器 - CPU_ID

CPU ID寄存器指示了CPU的类型和版本

-

MOD:Module Identification Number,用于标识模块

-

MOD_32B:32-Bit Module Enable,如果其值为

0xC0,则为32位模式 -

MOD_REV:Module Revision Number,校订版本,其值范围为

01~FF

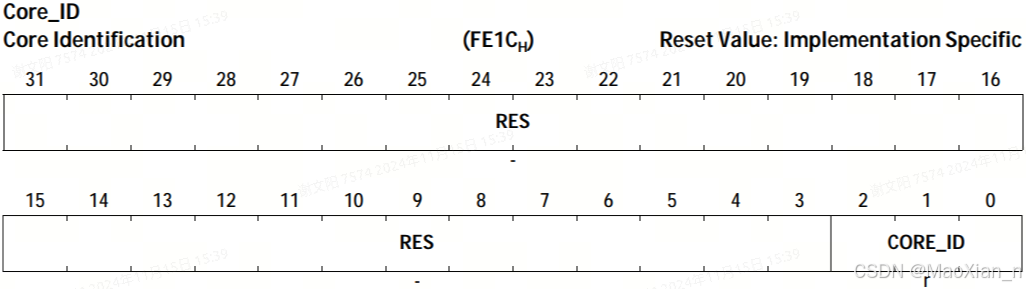

Core ID寄存器 - CORE_ID

多核处理器系统中,每个内核都有一个唯一的编号,其值保存在CODE_ID寄存器中

-

CORE_ID:Core Identification Number,内核ID

3.4.兼容模式寄存器 - COMPAT

COMPAT寄存器用于控制系统是否强制兼容之前的版本,其内容以各平台具体实现而定

注意:该寄存器受SAFETY_ENDINIT保护

-

Implementation Specific:Implementation Specific,以各平台具体实现而定

3.5.权限控制寄存器

SIST模式权限控制寄存器 - SMACON

使用SMACON寄存器可以控制系统测试软件(Software in System Test, SIST)的运行,该寄存器的实现依平台而定

注意:该寄存器受SAFETY_ENDINIT保护

-

Implementation Specific:Implementation Specific,以各平台具体实现而定

3.6.中断寄存器

TriCore架构中,一个典型的服务/中断请求包含独立的控制位,用于使能/禁用请求、分配优先级编号以及将服务请求发送给对应的服务提供者(CPU/DMA),参考内核特殊功能寄存器CSFR

3.7.内存保护寄存器

内存保护寄存器组的数量取决于平台的具体实现,最多可以有8个寄存器组(每个组包含一组数据和一组代码),每个寄存器组由若干组寄存器(也称为Range Table Entries)构成

每个范围表项包含一个段保护寄存器对,以及一个通用模式寄存器内的位字段,寄存器对指定了受保护内存的上下边界

内存保护寄存器受内核特殊功能寄存器CSFR的控制

3.8.Trap寄存器

Trap寄存器受内核特殊功能寄存器CSFR的控制

3.9.内存配置寄存器

内存配置寄存器由架构定义,但具体实现依平台而定

3.10.内核调试控制寄存器

TriCore寄存器支持调试功能

3.11.浮点寄存器

参考FPU_TRAP_CON寄存器的具体实现

3.12.内核特殊功能寄存器的权限

CSFR使用MFCR(Move From Core Register)指令进行读取操作,使用MTCR(Move To Core register)指令进行写入操作,用户程序一般不需要更新CSFR,因此,CSFR的实现不依赖于硬件结构,从而避免更新这些寄存器导致的意外情况,执行MTCR指令更新CSFR之后插入一条ISYNC指令可以避免因更新而产生的意外情况,ISYNC指令可以确保执行后续指令前,所有CSFR均已完成更新

MTCR指令访问未定义的寄存器时无效,MFCR指令读取未定义的寄存器会返回未定义的数据

1675

1675

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?