1.1 计算机系统基础知识

1.1.1 计算机系统硬件基本组成

计算机硬件系统由运算器、控制器、存储器、输入设备和输出设备5大部件组成。

- 运算器和控制器集中在一起被称为中央处理单元(CPU),是硬件系统的核心,用于数据的加工处理,能完成各种算术、逻辑运算及控制功能。

- 存储器是计算机系统中的记忆设备,分为内部存储器和外部存储器。前者速度髙、容量小,一般用于临时存放程序、数据及中间结果。而后者容量大、速度慢,可以长期保存程序和数据。

- 输入设备和输出设备合称为外部设备(简称外设),输入设备用于输入原始数据及各种命令,而输出设备则用于输出计算机运行的结果。

1.1.2 中央处理单元

CPU是计算机系统的核心部件负责获取程序指令、对指令进行译码并加以执行。

1、功能

(1)程序控制

(2)操作控制

(3)时间控制

(4)数据处理

2、组成

(1)运算器 ❤❤❤

由算数逻辑单元、累加寄存器、数据缓冲器寄存器和状态条件寄存器组成,运算器所有操作都是由控制器发出的控制信号来指挥的。功能主要是执行所有的算术运算,执行所有逻辑运算并运行逻辑测试。

- 算术逻辑单元ALU:执行算术运算和逻辑运算。

逻辑与:两数都为1,则结果1,否则0。

逻辑或:两数中一个为1,结果1,否则0。

逻辑异或:两数不同,结果1,否则0。

&&:都为真时为真,其余为假,

||:都为假时为假,其余为真,

!:表否定

算术左移,就是在原有的基础上*2

算术右移,就是在原有的基础上/2

- 累加寄存器AC:暂存数据,为ALU提供工作区。

- 数据缓冲寄存器DR

- 状态条件寄存器PSW归属有争议

(2)控制器 ❤❤❤❤

控制整个CPU的工作,决定了计算机运行过程的自动化。

指令控制逻辑组成部分: 取指令–》分析–》执行

-

指令寄存器(IR):执行指令时,先将它从内存储器中取到缓冲寄存器中,在放入IR暂存。

-

程序计数器(PC)

❤:有寄存信息和计数两种功能,又称指令计数器。程序执行前,存程序起始位置;程序执行 时,CPU自动更改,使其保持总是要执行的下一条指令地址。顺序执行时,修改过程通常只是对PC+1,转移指令时,根据位移量或者转移指令得到地址。

❤表示必考点/常考点 -

地址寄存器(AR):AR保持当前CPU所访问的内存单元的地址。

-

指令译码器(ID):包括操作码和地址码。

(3)寄存器组 ❤❤

分为专用寄存器和通用寄存器,用于暂时存储程序运行过程中的相关信息。其中,通用寄存器常用于暂存运算器需要的数据或运算结果,地址寄存器和数据寄存器用于访问内存时的地址和数据暂存,指令寄存器用于暂存正在执行的指令,程序计数器中存放待执行的指令的地址。

3 多核CPU

核心又称为内核,是CPU最重要的组成部分,主要厂商有AMD和Intel。

``

1.1.3 数据表示

计算机中使用二进制计数制,使用0,1表示,小数点则隐含表示而不占位置。机器数的编码方法成为码值,

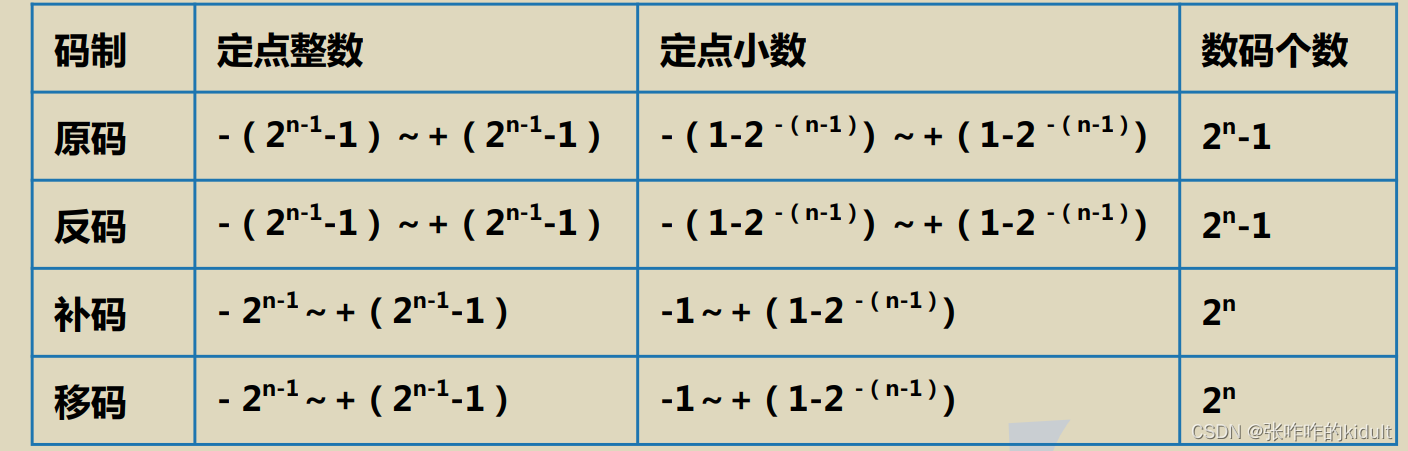

(1)源码、反码、补码和移码❤❤

补码和移码+-0的编码相同。

(2)定点数和浮点数❤❤

-

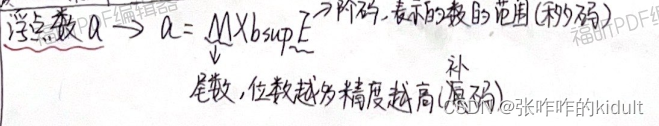

浮点数格式

❤阶码决定范围,阶码越长,范围越大;尾数决定精度,尾数越长,精度越高。

在IEEE754工业标准下:阶码使用移码表示,尾数使用原码表示。 -

浮点数运算过程

对阶→尾数计算→格式化;

❤对阶:小数像大数看齐,尾数右移。

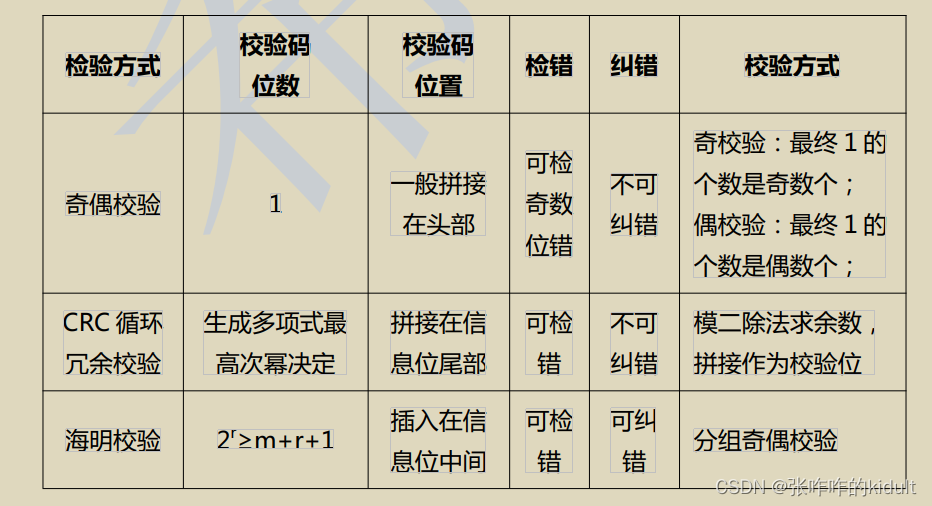

1.1.4 校验码 ❤❤❤❤

1、奇偶校验

2、CRC循环冗余校验

3、海明校验

如图:

1.2 计算机体系结构

1.2.1 计算机体系结构的发展

1、系统结构概述

发展过程,了解即可,这里就不记录了。

2、计算机体系分类 ❤❤❤

【内容很多,只记录常考点】

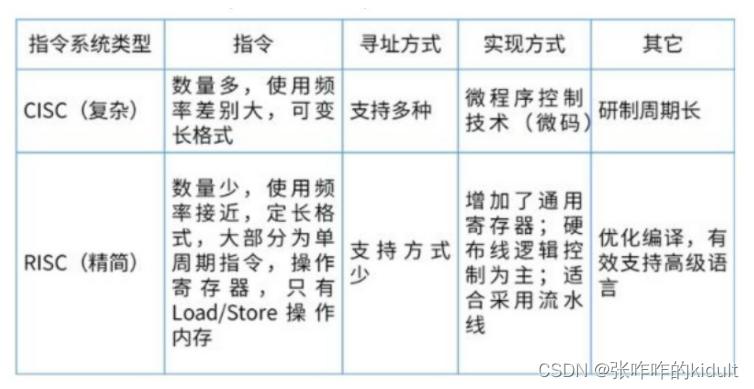

❤CISC和RISC

CISC:复杂指令集计算机,特点:指令数量多,指令频率差别大,变长,多种寻址方式,使用微码(微程序)实现。

RISC:精简指令集计算机,特点:指令数量少,频率接近,定长,单周期,多寄存器寻址,多通用寄存器,硬布线逻辑控制,适用于流水线。有效支持高级程序语言,优化编译。

1.2.2 存储系统

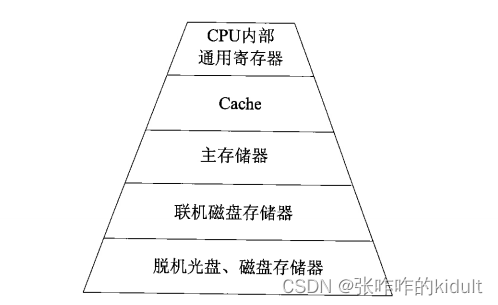

1、层次结构

2、存储器分类: ❤❤❤

- 按内容存取

相联存储器(如Cache)

在计算机的存储系统体系中,Cache是(除寄存器以外)访问速度最快的层次。解决CPU与主存之间速度容量不匹配问题。

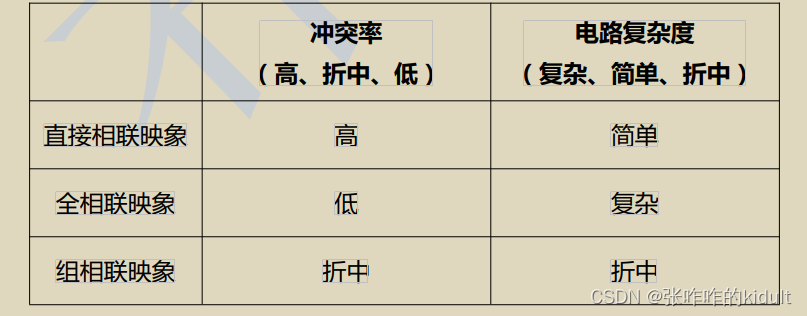

Cache与主存映射三种方式:

-

按地址存取

随机存取存储器(如内存)

顺序存取存储器(如磁带)

直接存取存储器(如磁盘) -

工作方式

随机存取存储器RAM(如内存DRAM)

只读存储器ROM(如BIOS)❤补充: -

存储速度:通用寄存器 > Cache > 内存 > 外存

-

主存的主要组成:DRMA,是间歇性刷新的

-

DMA:直接主存存取方式,允许主存储器与I/O设备之间通过DMA控制器进行数据转换,在硬件控制下数据传送,不需要通过CPU

-

采用 DMA方式传送数据时,每传送一个数据都需要占用一个(存储周期 )时间。

-

在CPU的寄存器中,( 指令寄存器)对用户是完全透明的。

1.2.3 输入/输出技术

1、微型计算机中最常用的内存与接口的编址方法

2、直接程序控制

程序控制(查询)方式:分为无条件传送和程序查询方式。方法简单,硬件开销小,但I/O能力不高,严重影响CPU的利用率。

3、中断方式 ❤❤❤

程序中断方式:与程序控制方式相比,中断方式因为CPU无需等待而提高了传输请求的响应速度。

❤中断处理(CPU无需等待也不必查询I/O状态):

(1)当I/O系统准备好以后,发出中断请求信号通知CPU;

(2)CPU接到中断请求后,保存正在执行程序的现场(保存现场),打断的程序当前位置即为断点;

(3)(通过中断向量表-保存中断服务程序的入口地址)

(4)转入I/O中的服务程序的执行,完成I/O系统的数据交换;

(5)返回被打断的程序继续执行(恢复现场)。

4、直接存储器存取方式 ❤❤❤

DMA方式:DMA方式是为了在主存与外设之间实现高速、批量数据交换而设置的。DMA方式比程序控制方式与中断方式都高效。

- 采用 DMA方式传送数据时,每传送一个数据都需要占用一个(存储周期 )时间。

5、输入输出处理机(IOP)

1.2.4 总线结构

分为数据总线、地址总线和控制总线。

1.3 安全性、可靠性与系统性能评测

1.3.1 计算机安全概述

1、计算机的安全等级

三类安全性指的是技术安全性、管理安全性和政策法律安全性。

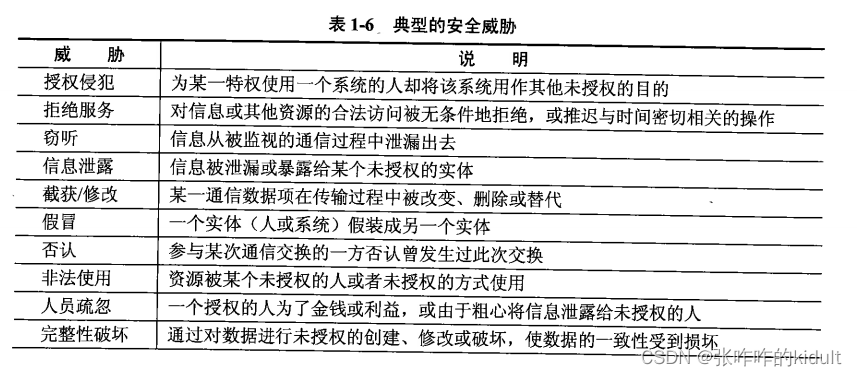

2、安全威胁

PS:如果后面没有讲到病毒,攻击,会在此处补充。

1.3.2 加密技术和认证技术 ❤❤❤

❤加密算法:

常见对称密钥加密算法(共享密钥加密技术):DES、3DES(三重DES)、RC-5、IDEA、AES算法。

常见非对称密钥加密算法(公开密钥加密技术):RSA、ECC常见的摘要算法:MD5(128位),SHA(160位)。

3DES:两个56位的密钥,长度加长

IDEA:长度128位

公钥体系中,私钥用于(解密和签名 ),公钥用于(加密和认证 ) 。 用公钥加密、私钥解密,可实现保密通信;用私钥加密、公钥解密,可实现数字签名。

❤加密技术应用:

数字信封:用接收方公钥加密使用的对称密钥。

数字签名:用发送方私钥签名,保证发送方身份真实性,发送者不可抵赖。与信息摘要结合,可防篡改。

信息摘要:单向散列值函数,防篡改,保证消息完整性。数字证书

数字证书的内容包括:CA签名、用户信息(用户名称)、用户公钥等。证书中的CA签名验证数字证书的可靠性、验证网站真伪。

用户公钥:客户端利用证书中的公钥加密,服务器利用自己的私钥解密。

1.3.3 计算机可靠性

1 计算机可靠性概述 ❤❤

可维修性:MTBF / (MTBF + MTRF)

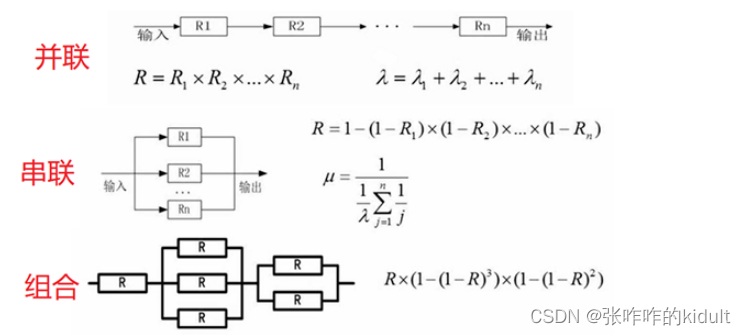

2 计算机可靠性模型❤❤

可靠性表示:MTTF/(1+MTTF)

❤❤❤

串联系统计算:R总=R1R2…*Rn;

并联系统计算:R总=1-(1-R1)(1-R2)…(1-Rn);

❤补充

-

❤流水线技术

流水线建立时间:第1条指令执行时间

流水线周期:指令分段后,最长段时间流水线执行时间(默认使用理论公式,无答案时考虑实践公式)

理论公式:流水线建立时间+(指令条数-1)流水线周期

实践公式:指令段数流水线周期+(指令条数-1)*流水线周期吞吐率=指令条数/流水线执行时间最大吞吐率=流水线周期的倒数。 -

❤局部性原理

时间局部性:指程序中的某条指令一旦执行,不久以后该指令可能再次执行,典型原因是由于程序中存在着大量的循 环操作。

空间局部性:指一旦程序访问了某个存储单元,不久以后,其附近的存储单元也将被访问,即程序在一段时间内所访问的地址可能集中在一定的范围内,其典型情况是程序顺序执行。 -

❤主存编址计算

-内存单元数个数=最大地址+1-最小地址内存编址内容:

按字编址(每个存储单元存放内容为机器字长—题干定义)按字节编址(每个存储单元内容为1字节即8bit)

内存总容量=内存单元数编址内容总容量=单位芯片容量总片数总片数=总容量/单位容量;

单位芯片容量=总容量/芯片片数。

1.3.4 计算机系统的性能评价

1、性能评测常用方法

- 时钟频率

- 指令执行速度

- 等效指令速度法

- 数据处理速率

- 核心程序法

994

994

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?