hls

#include<ap_int.h>

#define N 2

#define w 16

void foo(ap_int<w> a[N][N],ap_int<w*2> y[N][N],ap_int<w> look_weight[N][N]);

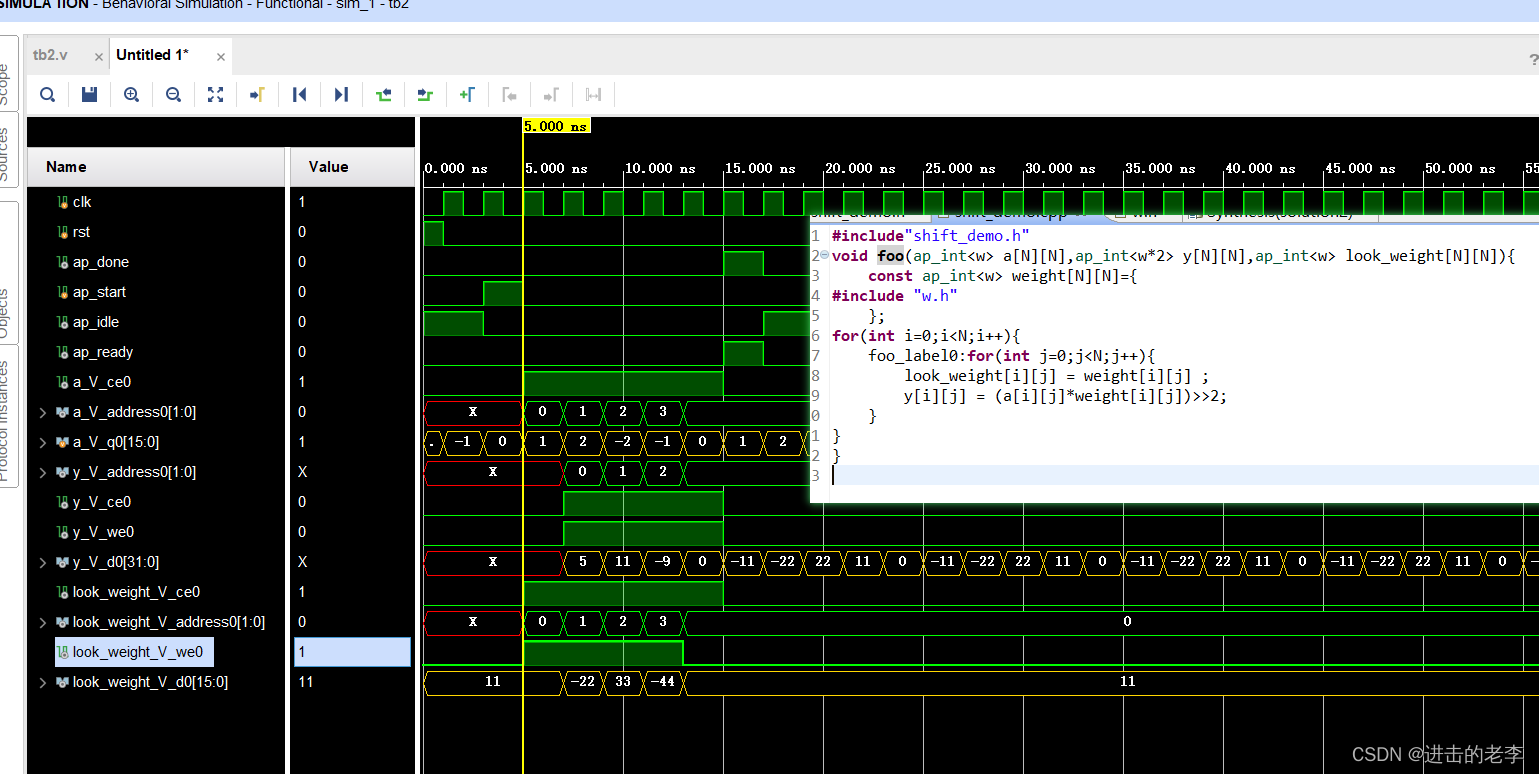

#include"shift_demo.h"

void foo(ap_int<w> a[N][N],ap_int<w*2> y[N][N],ap_int<w> look_weight[N][N]){

const ap_int<w> weight[N][N]={

#include "w.h"

};

for(int i=0;i<N;i++){

foo_label0:for(int j=0;j<N;j++){

look_weight[i][j] = weight[i][j] ;

y[i][j] = (a[i][j]*weight[i][j])>>2;

}

}

}

11,

-22,

33,

-44

tb

`timescale 1ns / 1ns

//

module tb2();

wire a_V_ce0,y_V_ce0,y_V_we0,look_weight_V_ce0,look_weight_V_we0;

wire ap_done,ap_idle,ap_ready;

wire [1:0] a_V_address0;

wire [1 : 0] y_V_address0;

wire [31 : 0] y_V_d0;

wire [1 : 0] look_weight_V_address0;

wire [15 : 0] look_weight_V_d0;

reg clk = 0;

always #1 clk = ~clk;

reg rst = 1;

reg ap_start = 0;

reg signed [15 : 0] a_V_q0=-2;

always @(posedge clk)begin

if(a_V_q0 == 2)begin

a_V_q0<=-2;

end else begin

a_V_q0<=a_V_q0+1;

end

end

foo_0 your_instance_name (

.a_V_ce0(a_V_ce0), // output wire a_V_ce0

.y_V_ce0(y_V_ce0), // output wire y_V_ce0

.y_V_we0(y_V_we0), // output wire y_V_we0

.look_weight_V_ce0(look_weight_V_ce0), // output wire look_weight_V_ce0

.look_weight_V_we0(look_weight_V_we0), // output wire look_weight_V_we0

.ap_clk(clk), // input wire ap_clk

.ap_rst(rst), // input wire ap_rst

.ap_start(ap_start), // input wire ap_start

.ap_done(ap_done), // output wire ap_done

.ap_idle(ap_idle), // output wire ap_idle

.ap_ready(ap_ready), // output wire ap_ready

.a_V_address0(a_V_address0), // output wire [1 : 0] a_V_address0

.a_V_q0(a_V_q0), // input wire [15 : 0] a_V_q0

.y_V_address0(y_V_address0), // output wire [1 : 0] y_V_address0

.y_V_d0(y_V_d0), // output wire [31 : 0] y_V_d0

.look_weight_V_address0(look_weight_V_address0), // output wire [1 : 0] look_weight_V_address0

.look_weight_V_d0(look_weight_V_d0) // output wire [15 : 0] look_weight_V_d0

);

initial begin

#1

rst <= 0;

#2

ap_start <= 1;

#2

ap_start <= 0;

end

endmodule

initial用<=

就是这个样子

写到这

突然想吃烧麦

不写了

1061

1061

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?