不赘述原理了,直接代码

设计代码:

module running_lamp_2th(

input clk, //50MHZ

input rst_n,//复位信号

output reg[3:0] LED = 4'b0111,//由VCC驱动所以低电平有效

output reg clk_division = 0 //分频时钟,要初始化,否则出于未知状态,无法反向

);

reg [22:0] cnt = 23'd0;//log2(5000000)==22.2535

always@(posedge clk or negedge rst_n)begin

if(!rst_n)begin

cnt<=23'd0;

clk_division<=0;

end

//每0.1s反向一次,所以信号的周期是0.2s

else if(cnt >= 'd5000000)begin

cnt<=0;

clk_division<=~clk_division;//反向

end

else

cnt<=cnt+1'b1;

end

always@(posedge clk_division or negedge rst_n)begin

if(!rst_n)

LED <= 4'b0111;

else

LED <= {LED[0],LED[3:1]};//0.2s转化一次状态

//大括号可以拼接

end

endmodule

测试代码:

`timescale 1ns / 1ps

//1个时间单位就是10^(-9)s

module tb;

reg clk;

reg rst_n;

wire [3:0] LED;

running_lamp_2th running_lamp_2th(

.clk(clk),

.rst_n(rst_n),

.LED(LED),

.clk_division(clk_division)

);

initial begin

clk = 0;

rst_n = 1;

#1000000000 rst_n = 0;//1s后

#1200000000 rst_n = 1;//经过实验,发现是再次经过1.2s,这里的语句是顺序执行

end

//50MHZ对应一个周期是20ns,一次反转是10ns

always #10 clk = ~clk;

endmodule

就是这样,还有点缺陷,那就是置1的时候不能立刻切回初始状态,以后再改一改

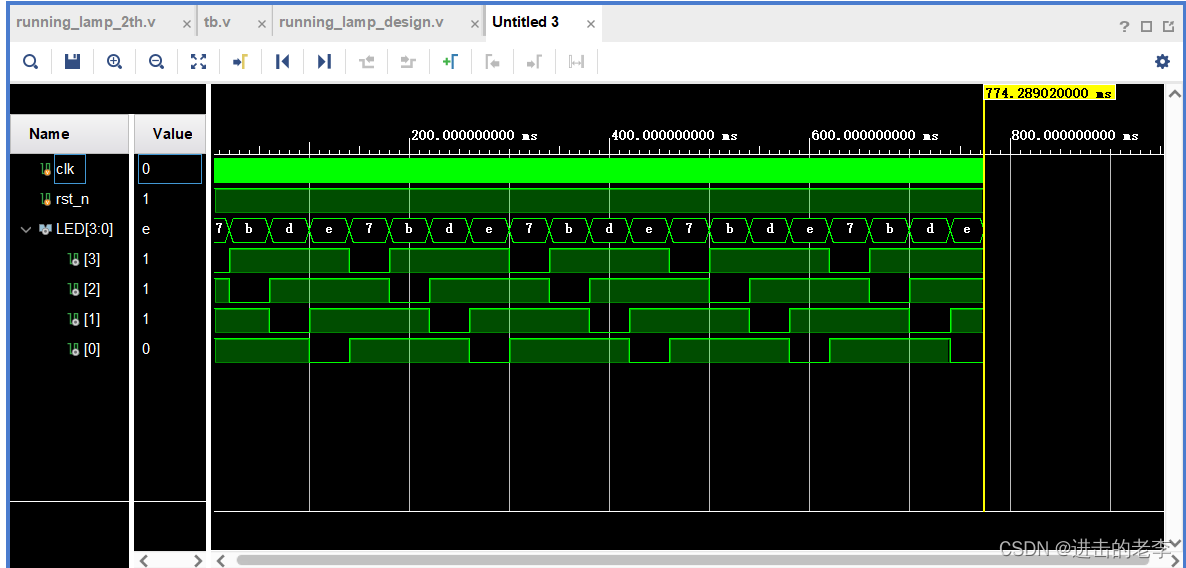

仿真时序图:

5845

5845

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?