计算机最核心的只有两部分:CPU、内存

CPU指令结构

内部结构分为三个单元:

控制单元:

控制单元是整个CPU的指挥控制中心,由指令寄存器、指令译码器、操作控制器等组成,对协调整个电脑有序工作极为重要。

运算单元:

运算单元是运算器的核心。可以执行算术运算、逻辑运算。相对控制单元而言,运算单元所进行的全部操作都是由控制单元发出的控制信号来指挥的。

数据单元:

存储单元包括缓存Cache、寄存器,是CPU中暂存数据的地方,里面保存着那些等待处理的数据,或已经处理过的数据,CPU访问寄存器用时比访问内存短。

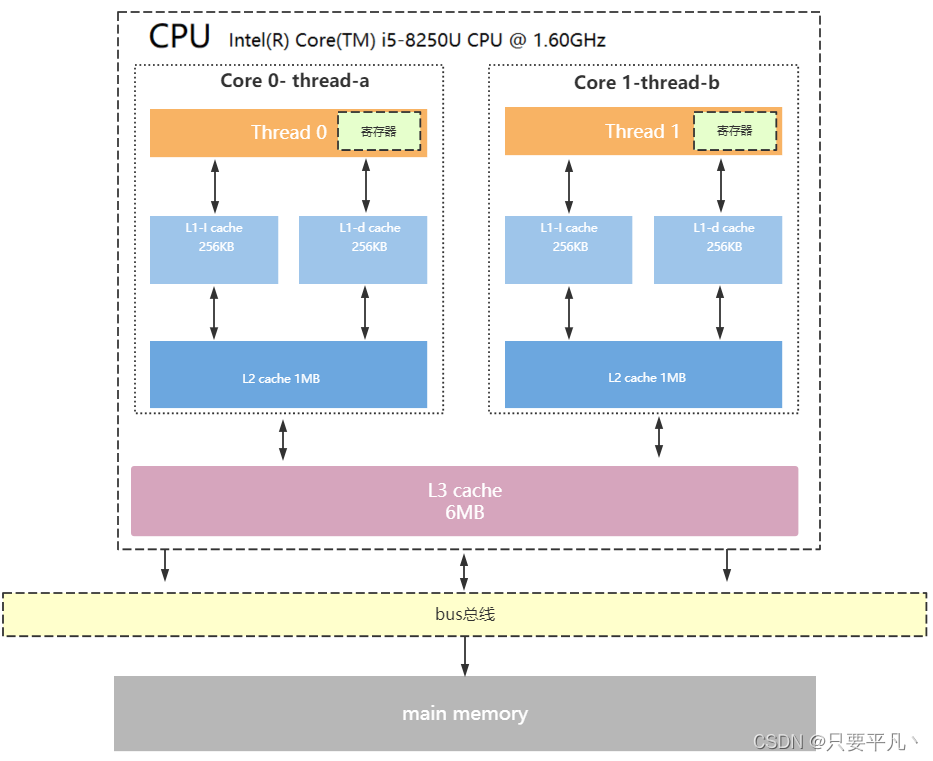

CPU缓存结构

为了提升执行效率,减少CPU与内存的交互,一般在CPU上集成了三级缓存结构

L1 Cache:物理上是一块,但逻辑上分为数据缓存和指令缓存

L2 Cache:物理核独占

L3 Cache:所有物理核共享

存储器存储空间大小:内存>L3>L2>L1>寄存器;

存储器速度快慢排序:寄存器>L1>L2>L3>内存;

缓存是由最小的存储区块-缓存行(cacheline)组成,缓存行大小通常为64byte。

CPU读取存储器数据过程

1、CPU取寄存器X的值,只需要一步:直接读取。

2、CPU取L1的值,需要1-3步(或者更多):把cache行锁住,把某个数据拿来,解锁。

3、CPU取L2的值,先要到L1里取,L1当中不存在,在L2里,L2开始加锁,加锁以后,把L2里的数据复制到L1,再执行取L1的过程,再解锁。

4、CPUL3的也是一样,只不过先由L3复制到L2,从L2复制到L1,从L1到CPU。

5、CPU取内存的值:通知内存控制器占用总线带宽,通知内存加锁,发起内存读请求,返回的数据保存到L3,再从L3到L2,再到L1,再从L1到CPU,之后解除总线锁定。

CPU高速缓存

在CPU访问存储设备时,无论是存取数据抑或存取指令,都聚集在一片连续的区域中,被称为局部性原理,基于这个原理来实现高速缓存。

时间局部性: 如果一个信息项正在被访问,那么在近期它很可能还会被再次访问。

比如循环、递归、方法的反复调用等

空间局部性: 如果一个存储器的位置被引用,那么将来他附近的位置也会被引用。

比如顺序执行的代码、连续创建的两个对象、数组等。

操作系统内存

执行空间保护

操作系统有用户空间与内核空间概念,目的是为了做到系统程序和用户程序运行安全隔离与稳定。

4G内存的机器可能有1G供内核使用,3G供用户使用,用户程序运行在用户方式下,而系统调用运行在内核方式下。

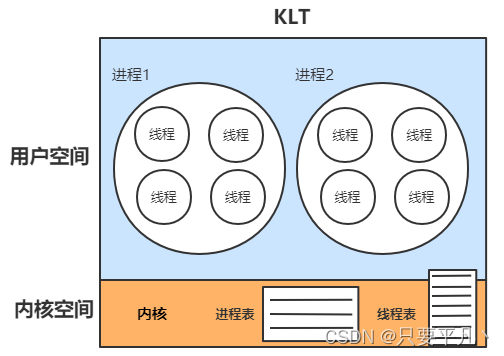

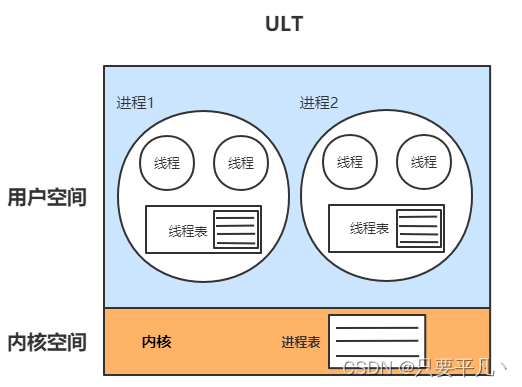

从空间上可以把CPU线程划分为两大模型:

内核线程模型(KLT)

由系统内核管理线程,内核保存线程的状态和上下文信息,线程阻塞不会引起进程阻塞。线程的创建、调度和管理由内核完成。

用户线程模型(ULT)

由用户程序自己管理线程,不依赖操作系统核心,应用提供创建、同步、调度和管理线程的函数来控制用户线程。但线程阻塞进程也阻塞。

进程

启动一个Java程序,操作系统就会创建一个Java进程。进程是操作系统资源分配的最小单位。

线程

操作系统调度CPU的最小单元,也叫轻量级进程,一个进程里可以创建多个线程,这些线程都拥有各自的计数器、堆栈和局部变量等属性,并且能够访问共享的内存变量。CPU在这些线程上高速切换,让使用者感觉到这些线程在同时执行,即并发的概念。

虚拟机指令集架构

虚拟机指令集架构主要分两种:

栈指令集架构

指令集中的指令大部分是零地址指令,执行过程依赖操作栈,不依赖硬件,可移植性更好,更好实现跨平台。

寄存器指令集架构

指令集往往都以一地址指令、二地址指令和三地址指令为主,完全依赖硬件,可移植性差,但性能更高效

Java是栈指令集架构

904

904

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?