博客内容来源为网络下载ppt,侵删

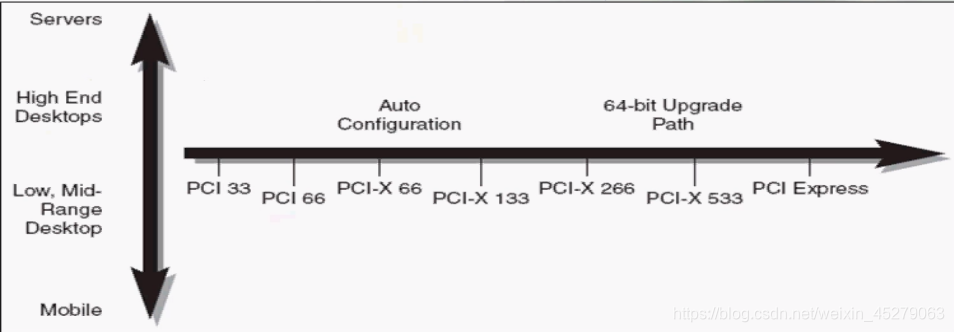

PCI的发展

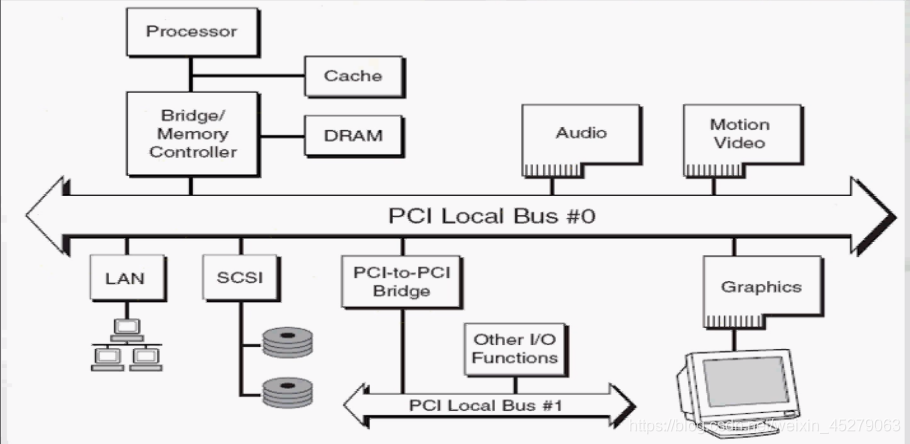

PCI Local Bus 示意图

NoteBook上常见的PCIE Device:SSD DGPU WLAN LAN CardReader。

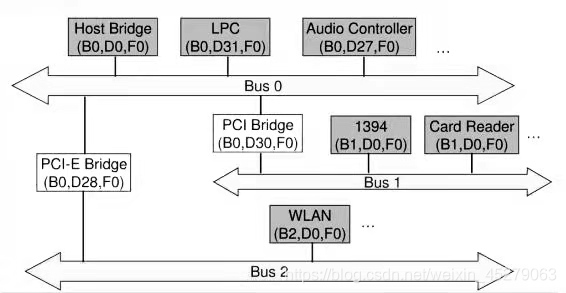

通过总线扩展出来的PCIE Bridge可以外接设备等。如下所示:

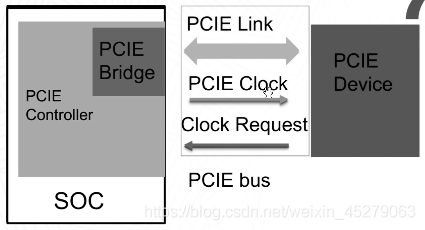

Bridge和Device之间通过Link进行沟通,同时Bridge发出Clock信号给Device,进行正常工作,但一直处于工作状态的话会占用资源,在Device不需要工作的时候,通过Request通知Bridge提供Clock,当然移除Request也是可行的。 Clock Request在项目中为了达到省电的目的,会设置Clock Request,当device 处于idle 状态时,Host不发送Clock 信号,当Device 需要work时,通过Clock Request pin通知Host发Clock信号。所以在项目中需要为每一个PCI/PCIE device配Clock Request 信号。

Project中所使用的PCIE device都是通过PCIE Bridge扩展出来。 PCIE Link宽度常见的有: x1, x2, x4, x8, x16,PCIE device工作在HW上需要有clock信号。 并非所有device都需要Expansion ROM,Expansion ROM通常包在BIOS ROM里面, PSOT过程中加载进去

PCIE结构框图:

每个PCIEcontroller/bridge和device 的位置都可以通过Bus,Device,Function来确定。

Bus: 0 ~ 255 Device: 0 ~ 31 Function: 0 ~ 7

Access PCI

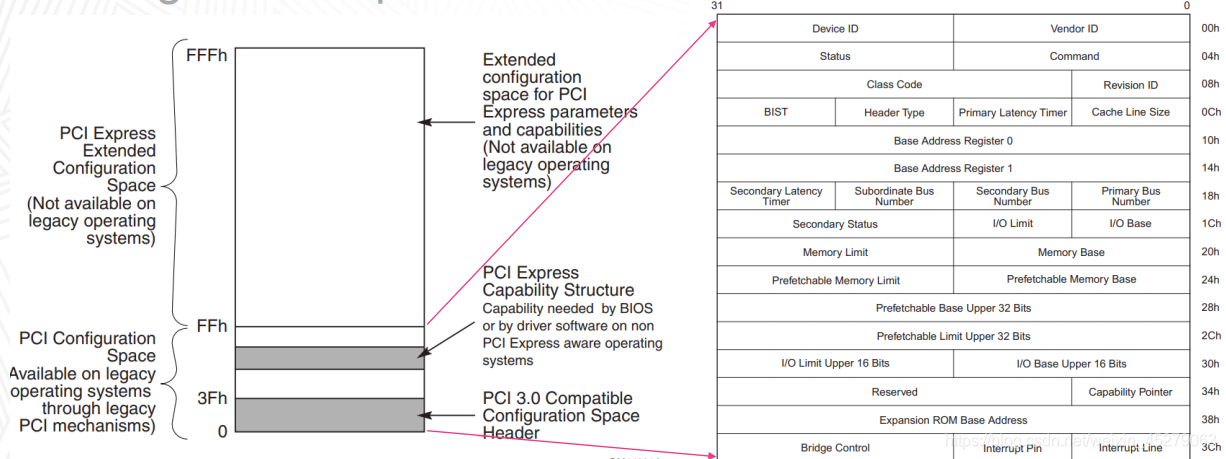

Configuration Space (配置空间)是PCIE controller和PCIE device的主要寄存器区域

Total Space大小为4K(0 ~ FFFh)

其中0~FFh为PCI和PCIE公用区域

PCI Configuration Space: 0 ~ FFh (256 Bytes)

PCIE Extended Configuration Space: FFh ~ FFFh (4K – 256 Bytes)。

Vendor ID(Offset 00h~01h) 记录PCI厂商识别码, 如Intel ID是 8086. 0FFFFh 是一个无效的Vendor ID, 如果读到0FFFFh, 可认为该处没有设备

Device ID(Offset 02h~03h) 记录该Vendor生产的PCI设备的识别码, Vendor ID + Device ID 的组合在所有PCI/PCIe设备中是唯一的。

Command (04~05h) 用于enable/disable Memory & I/O Space. [0] - I/O Space, [1] – Memory Space通过01打开关闭访问权限

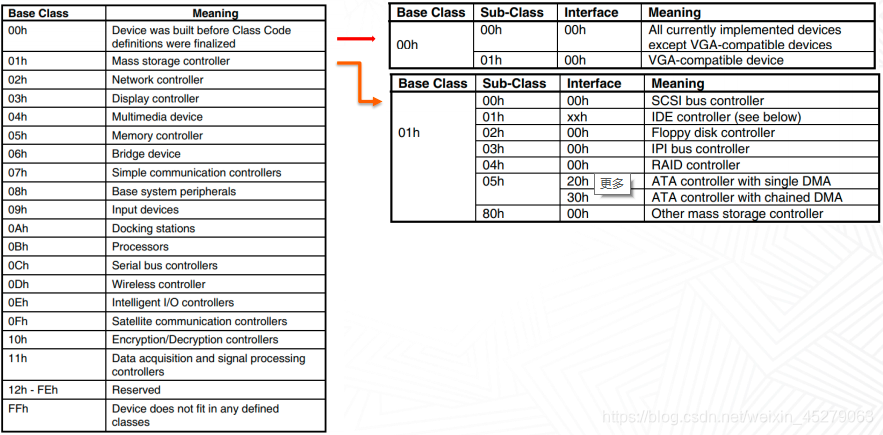

Class Code(Offset 09h~0Bh)是一个24位只读的寄存器, 用于定义PCIE device的类型, 由3个Byte组成。

基本类别 (Base Class)

子类别 (Sub Class)

程序界面 (Programming Interface)

比如 00 00 00h则证明这个是个VGA设备,下表为部分对照参考。

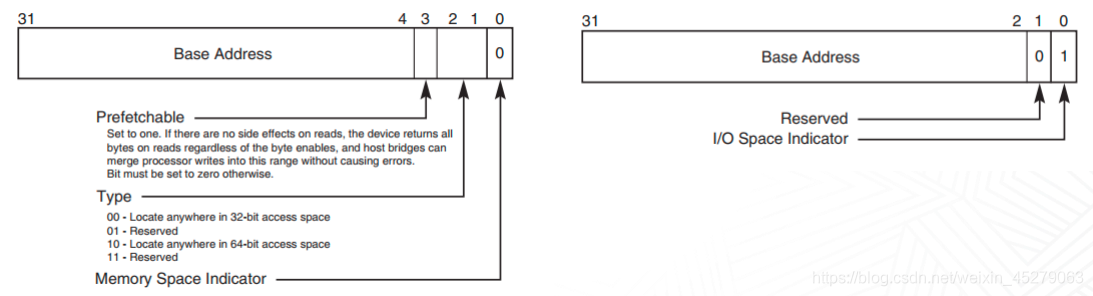

Bass Address(Offset 10h~27h) 该设备所使用的内存或者I/O资源

Subsystem Vendor ID (Offset 2Ch~2Dh)

Subsystem Device ID (Offset 2Eh~2Fh)

- 即SSID, 一般由BIOS根据不同的OEM来进行设定, 用于在OS驱动识别device究竟是在哪个产品型号上用

Capabilities register定义了PCIE扩展功能寄存器。0-3F定义的寄存器是每个PCIE设备都必须实现的,而PCIE的一些扩展功能,不是每个设备都必须实现的,可以根据自己的需要来实现其中一部分特性。这部分寄存器的组织结构叫做Capabilities寄存器,用链表的方式组织起来,称为Capabilities List。

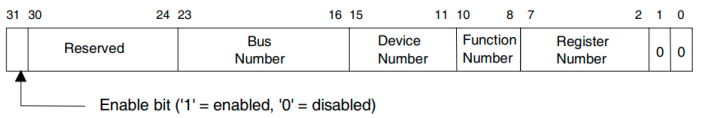

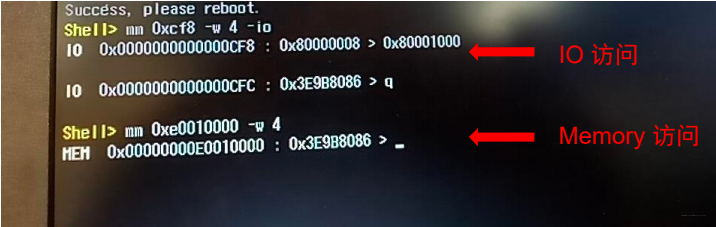

Configuration Space访问方法

- IO 访问

- Write CONFIG_ADDRESS to 0xCF8

- Read/Write CONFIG_DATA from 0xCFC

CONFIG_ADDRESS = 80000000h + (bus <<16) + (device <<11) + (function << 8) + (offset)

- Memory 访问

每一个PCIE device 的配置空间的寄存器会被映射到系统的物理内存空间,内存地址(PCIE_ADDRESS)算法如下:

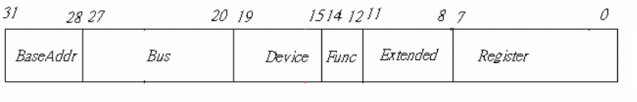

(PCIE spec 3.0 7.2.2 Table7-1)

PCIE_ADDRESS =BaseAddr + (Bus << 20) + (Device << 15) + (Func << 11) + offset

BaseAddr: Host Bridge Controller (Device 0, Function 0) PCI Configuration Space Offset 60h (32bit)

• 以读取device(B0:D2:F0) DID/VID为例:

CONFIG_ADDRESS = 0x80000000 + (0<<16) + (2<<11) + (0<< 8) + 0

= 0x80001000;

PCIE_ADDRESS = 0xE0000000+ (0<<20) + (2<<15) + (0<<11) + 0

= 0xE0010000;

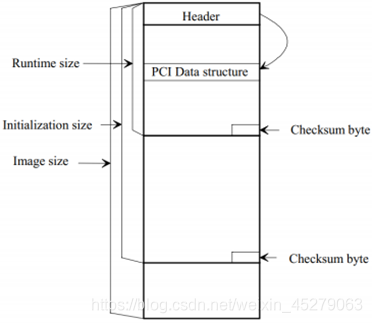

Expansion ROM 介绍

Expansion ROM又叫Option ROM。它是用于设备初始化和系 统boot的code。有的PCI Option ROM被存放在板卡上,而有的则

保存在BIOS 的binary里面。BIOS 在POST阶段,会扫描设备是否有 Expansion ROM,有的话将其拷贝到RAM中执行。

NB上常见的Expansion ROM有VBIOS, LAN PXE ROM, Raid ROM等。

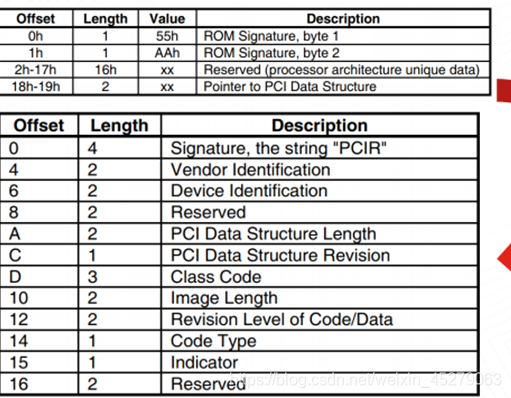

PCI Expansion ROM Header Format

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?