基于UDP协议的千兆以太网视频显示系统和心率数据传输

文章目录

前言

1.采用器件

xc7a100tfgg484-2、VITESSE VSC8601

2.参考的手册

- ug471_7Series_SelectIO

- VSC8601-DS-r41-VMDS-10210

3.前置知识

以太网基础

https://gitcode.csdn.net/65e6ef3d1a836825ed788b02.html?dp_token=eyJ0eXAiOiJKV1QiLCJhbGciOiJIUzI1NiJ9.eyJpZCI6ODE5MjYzLCJleHAiOjE3MTAzMjExMDYsImlhdCI6MTcwOTcxNjMwNiwidXNlcm5hbWUiOiJ3ZWl4aW5fNDUyODQ4NzEifQ.QyyEsiEGoJplLK0C4DQ87YV0GCjqwP4ZOeowcl9x4Zo

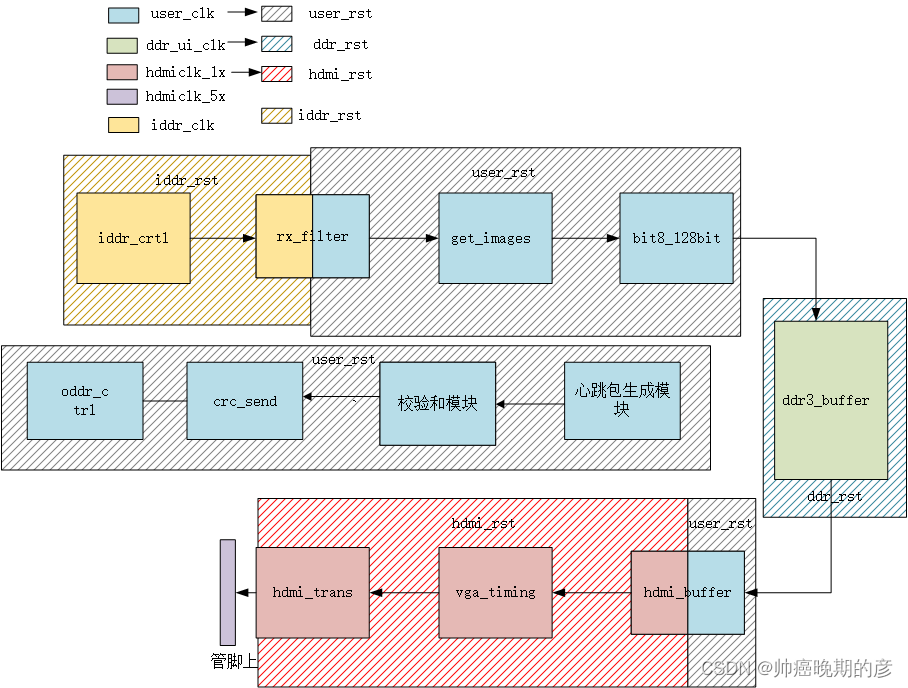

设计方案

整体模块的时钟和复位

根据分级复位设计,以及各模块需要时钟,设计整体的项目架构

其中整体的复位选择mig给到用户的复位信号和pll的locked信号两者的结合,将其在每个时钟域下的每个模块进行异步复位同步释放给过去。

跨时钟域的部分,采用异步fifo来解决,整体采用流水级的设计方案

iddr模块

看我的文章

https://blog.csdn.net/weixin_45284871/article/details/136879839

千兆以太网的接收和crc校验

请查看我的文章

https://blog.csdn.net/weixin_45284871/article/details/137057599?spm=1001.2014.3001.5502

get_image

主要就是把裸数据抠出来

bit8to128_buffer

该模块有两个功能

- 对像素数据进行高低位反转,因为以太网来的每个16位像素,是先发的高位,再发的低位,fpga先接收的像素的高位,所以每接收到2个字节就反转一下变成[高8位,低8位]写进fifo

- 数据位宽的转换,因为ddr的写是突发的,所以要个fifo来进行位宽转换。

- 作为缓冲,编写输入输出条件使两端的带宽对等,千兆来的数据带宽和ddr写的数据带宽不一样,所以要个fifo来缓冲,缓存深度调成2次ddr突发写的深度就行,因为ddr写的速度更快。

- 完成ddr的写控制信号产生,等一次突发写结束后,才能开始下一次突发写。

当fifo里面的数满足一次突发长度的值时,就启动读给ddr,所以fifo的深度使用的2次ddr突发写的深度就行

ddr控制器的设计

请查看我的文章

hdmi_buffer

该模块的功能主要是

- 完成跨时钟域的读写

- 完成数据位宽的转换。hdmi的读为16bit,ddr的写为128

- 作为缓冲,使得写入读出带宽对等,hdmi的读数据带宽为102476860*24,大概1.1Gbit/s,ddr的带宽更大。

- 完成ddr的读控制信号产生,等一次突发读结束后,才能开始下一次突发读。

当fifo里面的数据不够图像的一行数据时,就可以从ddr中突发读,所以让FIFO的深度满足2行数据就行。

心跳包的发送模块

请查看我的文章

https://blog.csdn.net/weixin_45284871/article/details/137057819?spm=1001.2014.3001.5502

对项目进行时序约束,分析,优化

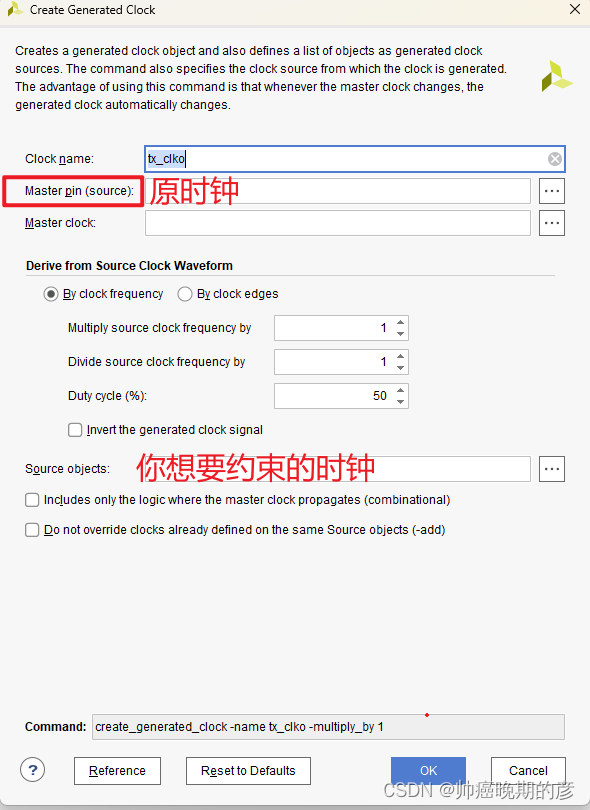

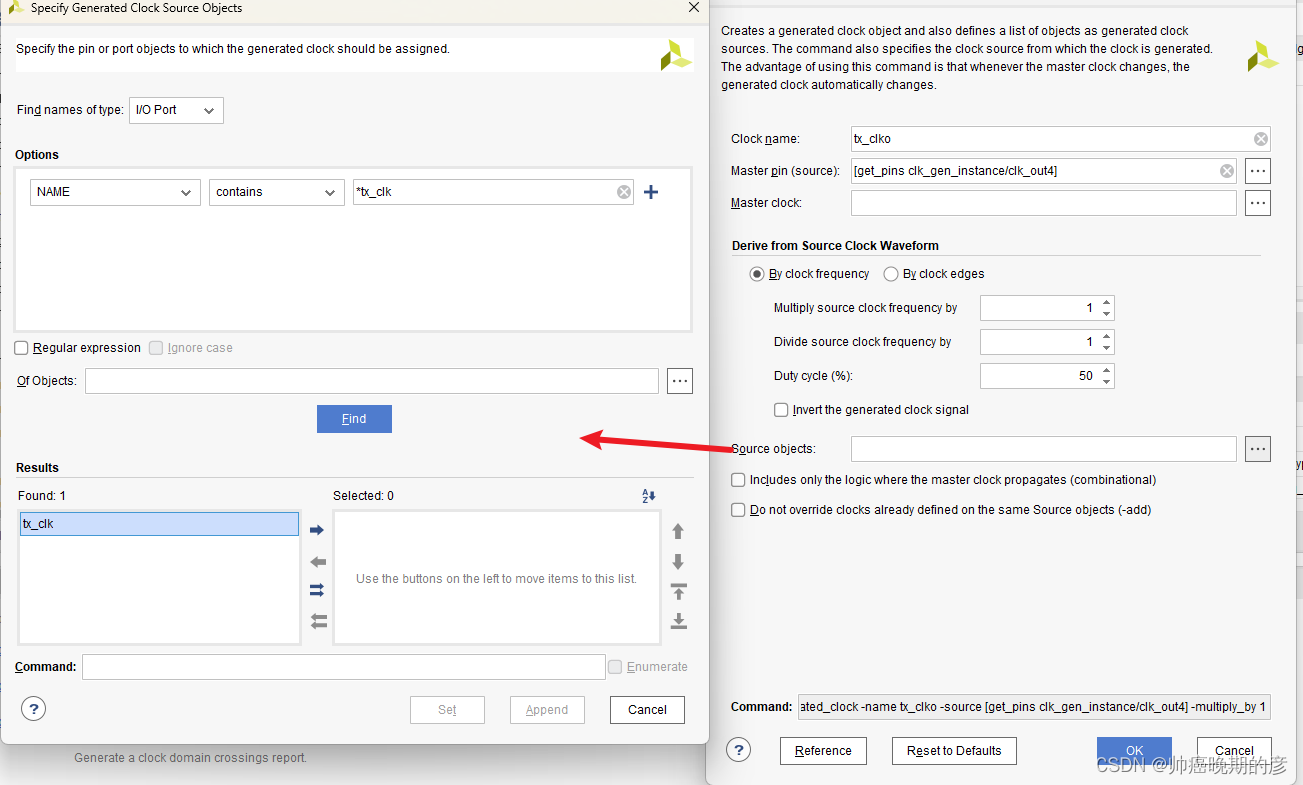

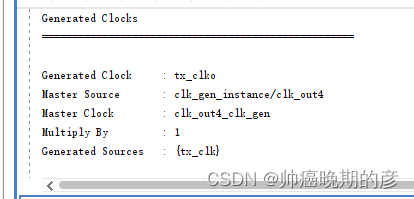

时钟的约束

首先将生成时钟约束了,因为项目的管脚进来的时钟都经过pll,就不需要基准时钟约束了,所以要完成生成时钟约束

就只有oddr的输出的时钟需要约束,把它约束成生成时钟。因为要分析output delay。生成时钟的源可以是生成时钟

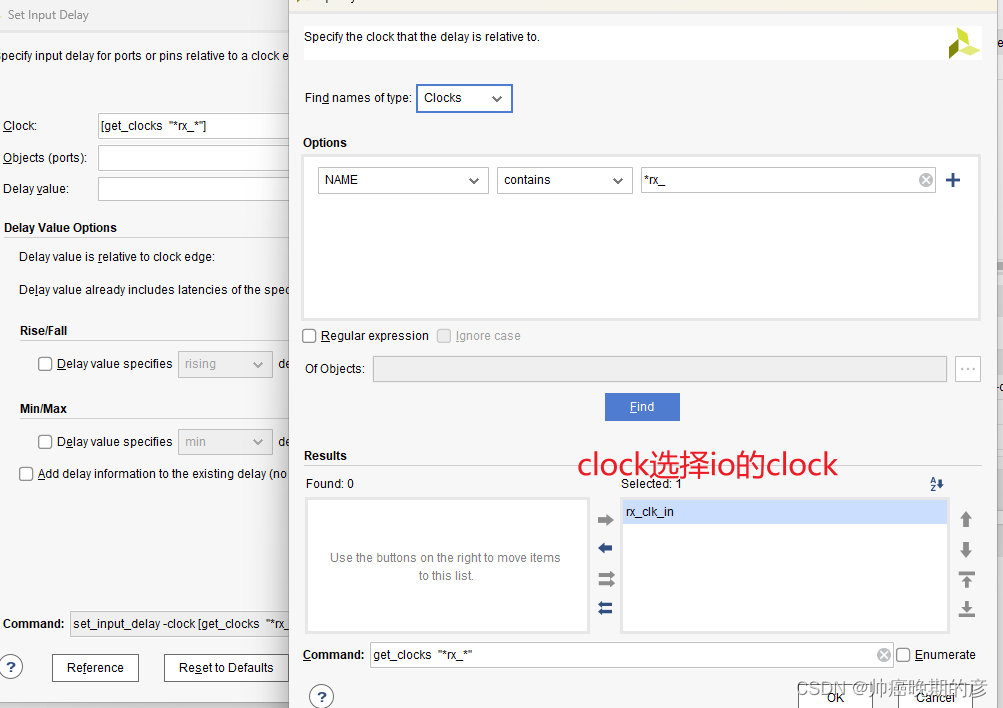

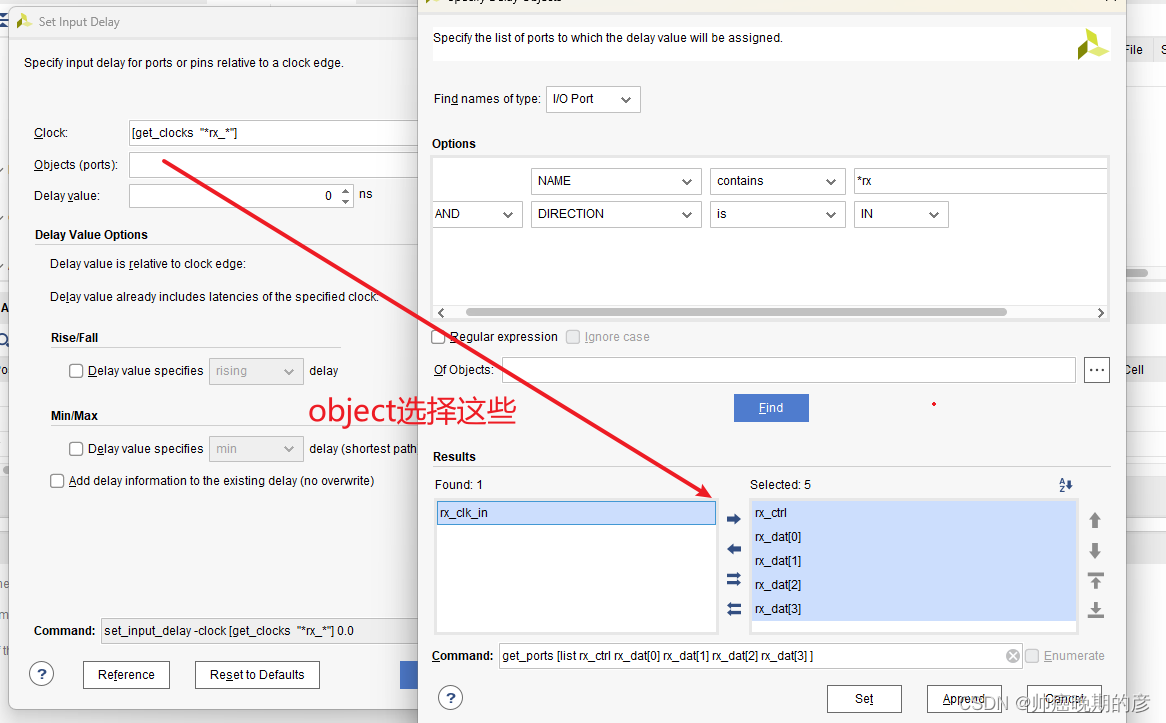

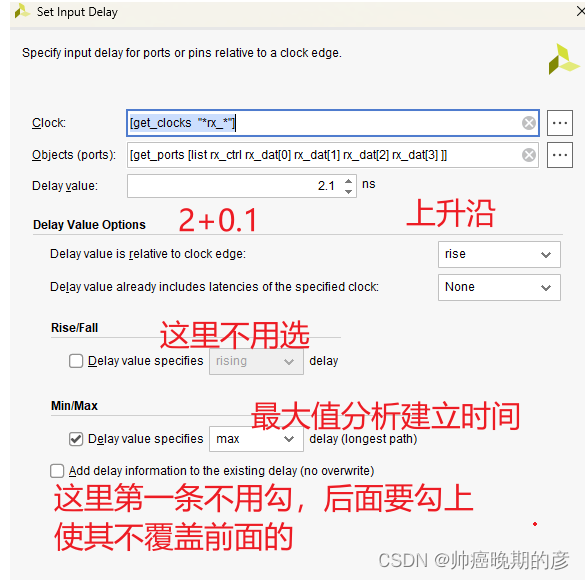

简易的input delay的约束

这里做的是简易的input delay,即忽略了板间时钟和数据的延时

input delay目的是为了告诉fpga芯片过来的输入引脚上的时钟和数据的相位关系——即时钟发射沿到数据间的延迟,这里过来的时钟和数据的关系已经是定了的,他们是从上一个模块传递过来的,如果你把这个约束告诉了fpga后,它布局布线还是有问题,不满足引脚数据到fpga芯片第一级寄存的建立时间和保存时间,那么你要么通过pll调整引脚时钟的相位,要么通过ilogic的IDELAYE2原语来调数据的延迟(建立时间slack多,保持时间slack少。就延迟数据)

首先约束的时候我忽略了板间的延时,约束输入引脚时钟和数据到达fpga芯片时刻,时钟发射沿到数据间的延迟。

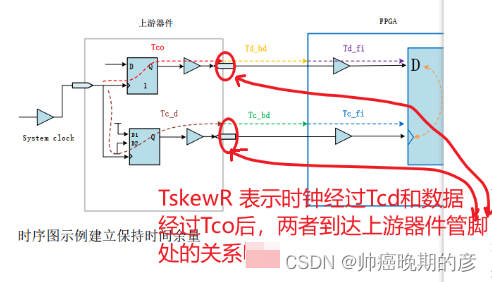

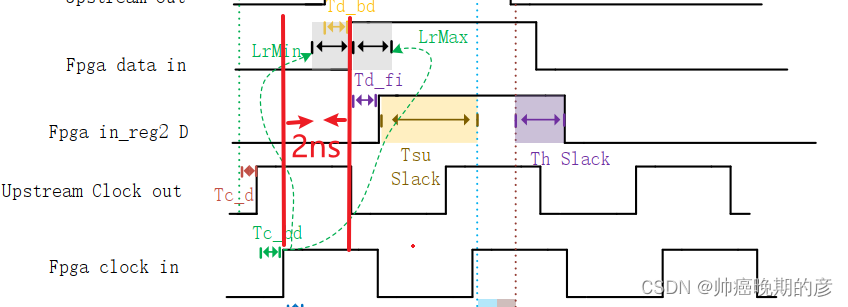

之前在phy芯片中,设置了时钟与数据输出到phy芯片管脚两者间的关系为Tskew=2ns

数据线之间的 skew 数据手册未提供,我们假设一个 0.2ns 的偏移范围,一般专用芯片这个数据之间的 skew 很小,几乎是数据周期的 1/40 左右, 比如 8ns 周期, data skew=8/40=0.2ns

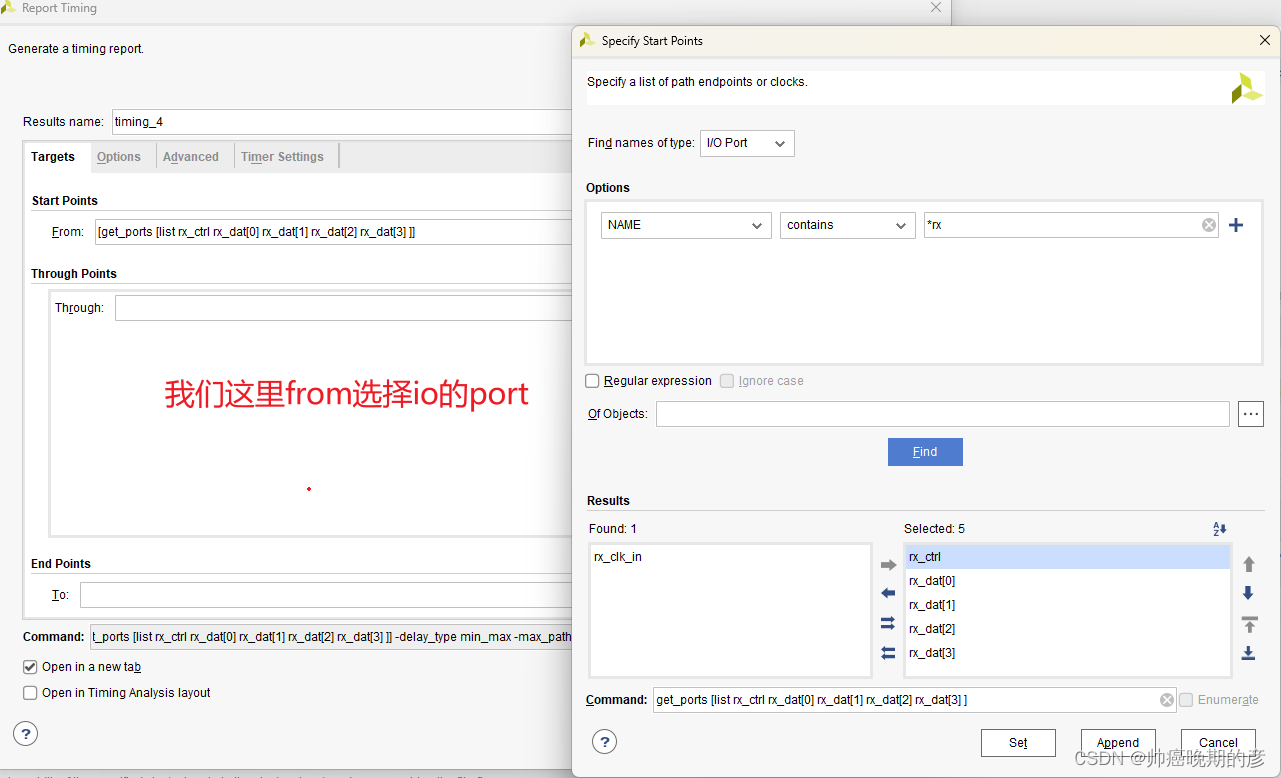

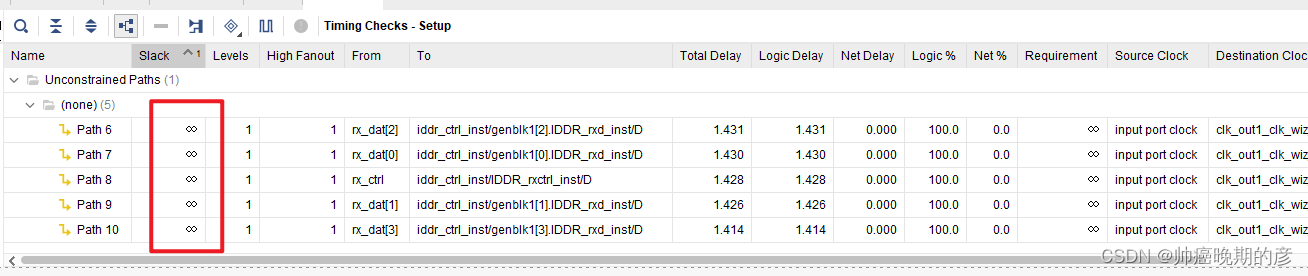

我们可以先看看不约束是什么效果

可以看到输入管脚到fpga芯片第一级寄存器的slack是无穷大的

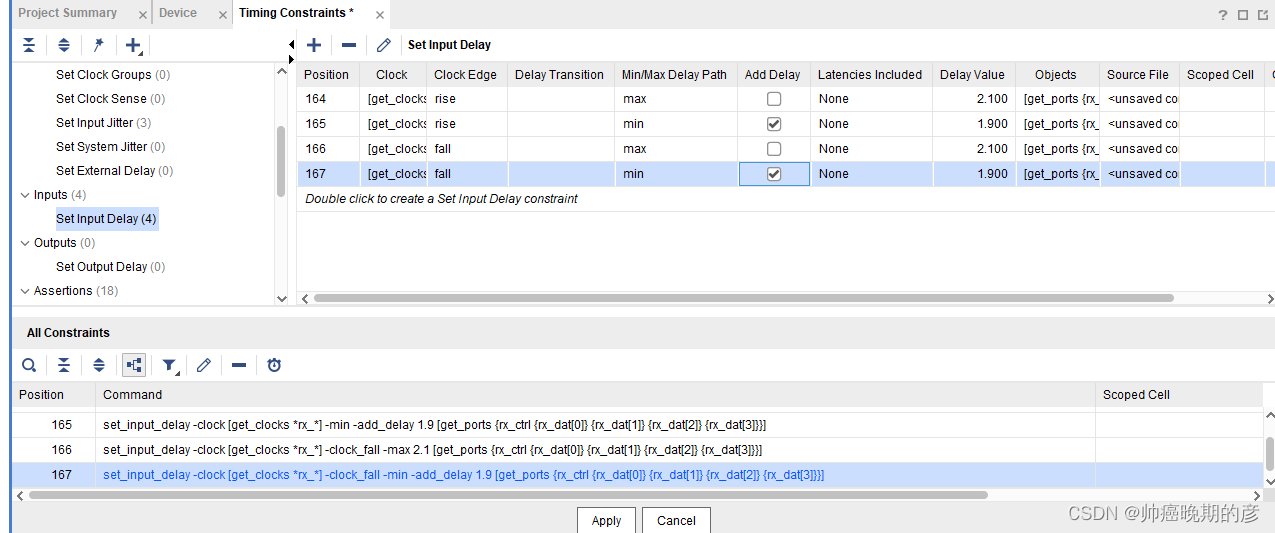

现在来约束,首先iddr的时钟是双沿采样,所以对于上升沿要进行建立时间约束(max delay)和保持时间约束(min delay)

后面将上升沿和下降沿的max min delay都约束上

简易的output delay的约束

这里做的是简易的output delay的约束,即忽略板间延时,假设不知道目标端的建立时间和保持时间要求的情况下做的约束,告诉仿真工具输出时钟的采样沿是和数据中心对齐的

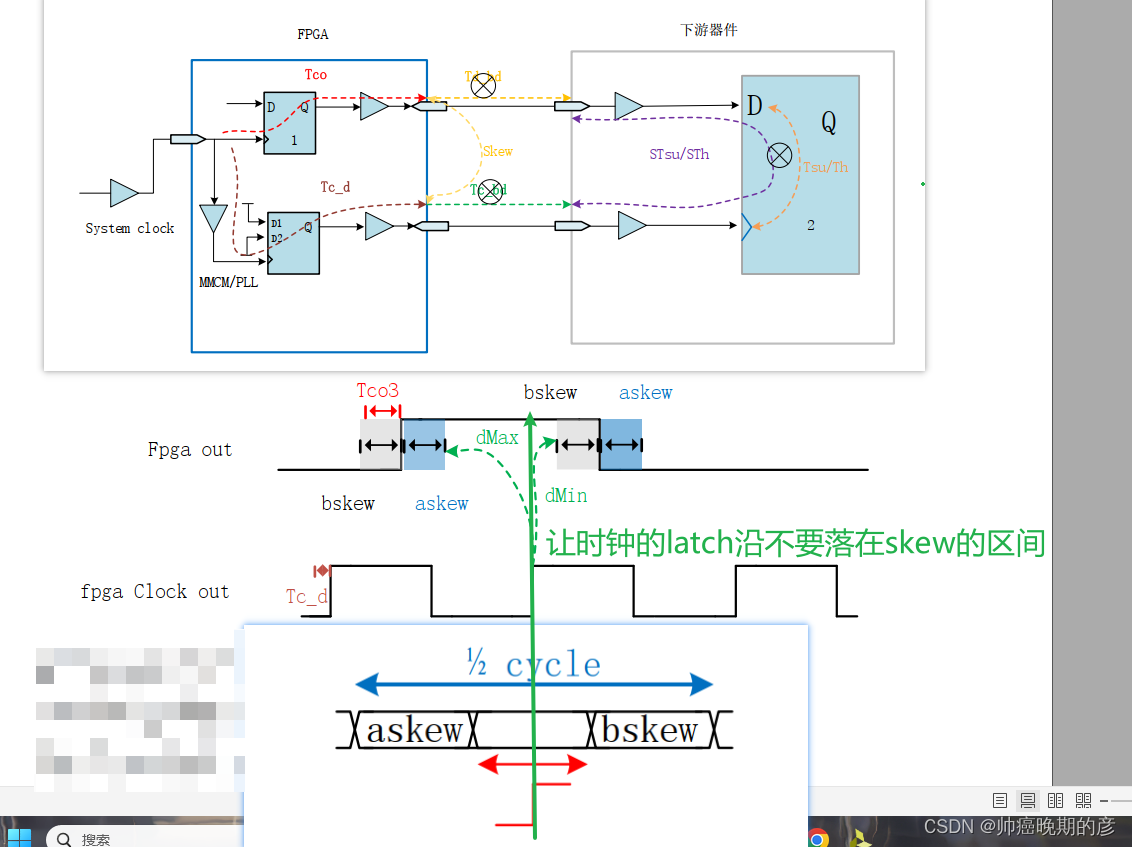

output delay是我们fpga芯片把时钟和数据输出到下一个模块的,因此时钟和数据间的关系需要我们自己来调整,这是与inputdelay不一样的地方。怎么调整呢?通过约束来调整,就是通过约束告诉这个布局布线工具发出的时钟latch沿不要落在skew区,来保证时钟的latch沿和数据中心对齐。如果通过约束告诉这个布局布线工具发出的时钟latch沿不要落在skew区之后,工具布局布线还是落在了skew区,说明你得调一下时钟的相位,或者调一下数据的延时

在不知道目标端的建立时间和保持时间要求的情况下,约束时钟和数据从fpga芯片出去的相位关系,时钟锁存沿到数据间的延迟。

这里cycle/2是因为双沿采样

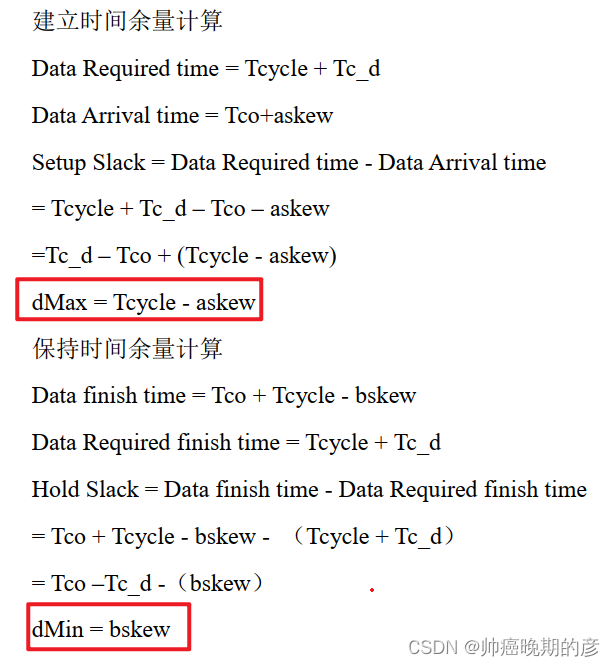

通过调整skew 的值使时钟latch沿在一个中心位置。如图数据fpga_out是到达fpga芯片正常的一个情况,askew是after skew,就是数据们中最晚到达的那个数据,用来分析建立时间,

bskew是beforeskew,是数据们最早结束的那个数据,用来分析保持时间

根据这两个公式来算

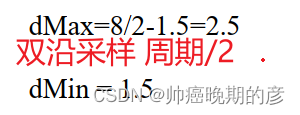

askew=bskew=1.5,

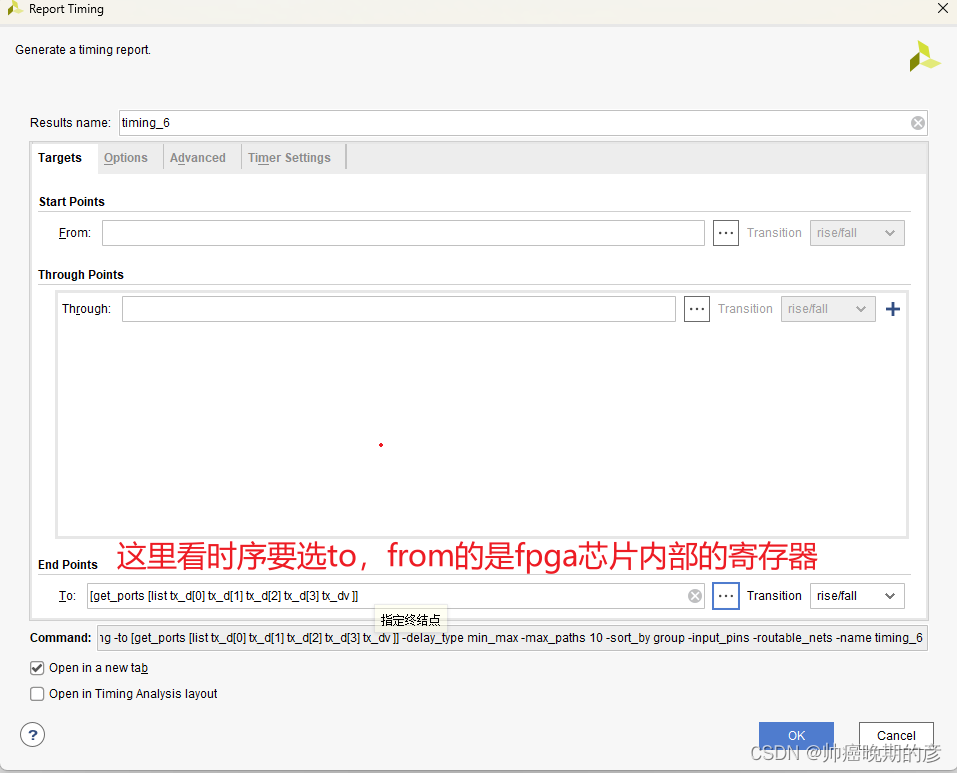

开始约束,首先要保证对管脚上的tx_c创建生成时钟 generate clock ,原因是从 tx_c 从 oddr 输出时, 综合分析工具并不知道此路为时钟信号, 所以我们需要约束。 时钟源为 PLL 的输出, 目的端是芯片的 tx_clk 引脚。

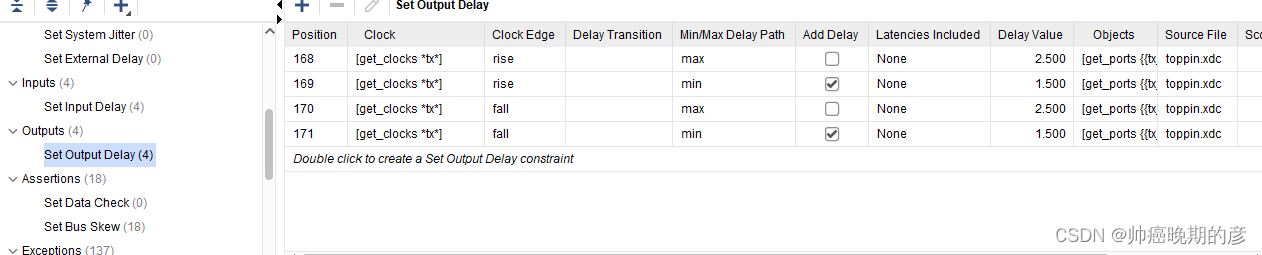

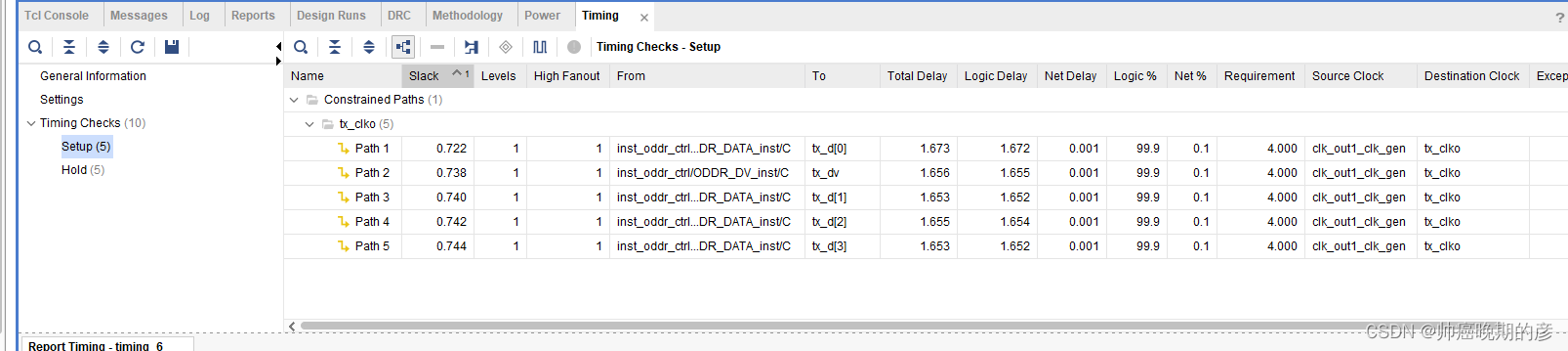

约束好生成时钟后,开始约束outputdely,和input delay一样的操作,把时钟的上升沿和下降沿一起约束好,约束好之后看一下时序报告,当前我设置的时钟是0度,如果时序报错,就需要相移时钟,使其达到最佳相位。

可以看到时序都非常的不错,说明时钟0相位是ok的

调试遇到的困难

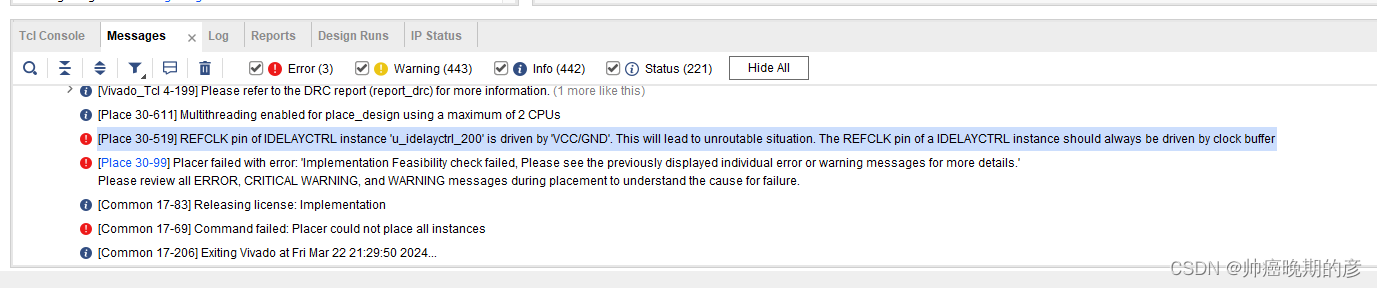

发现是没有输入mig核的200MHz时钟

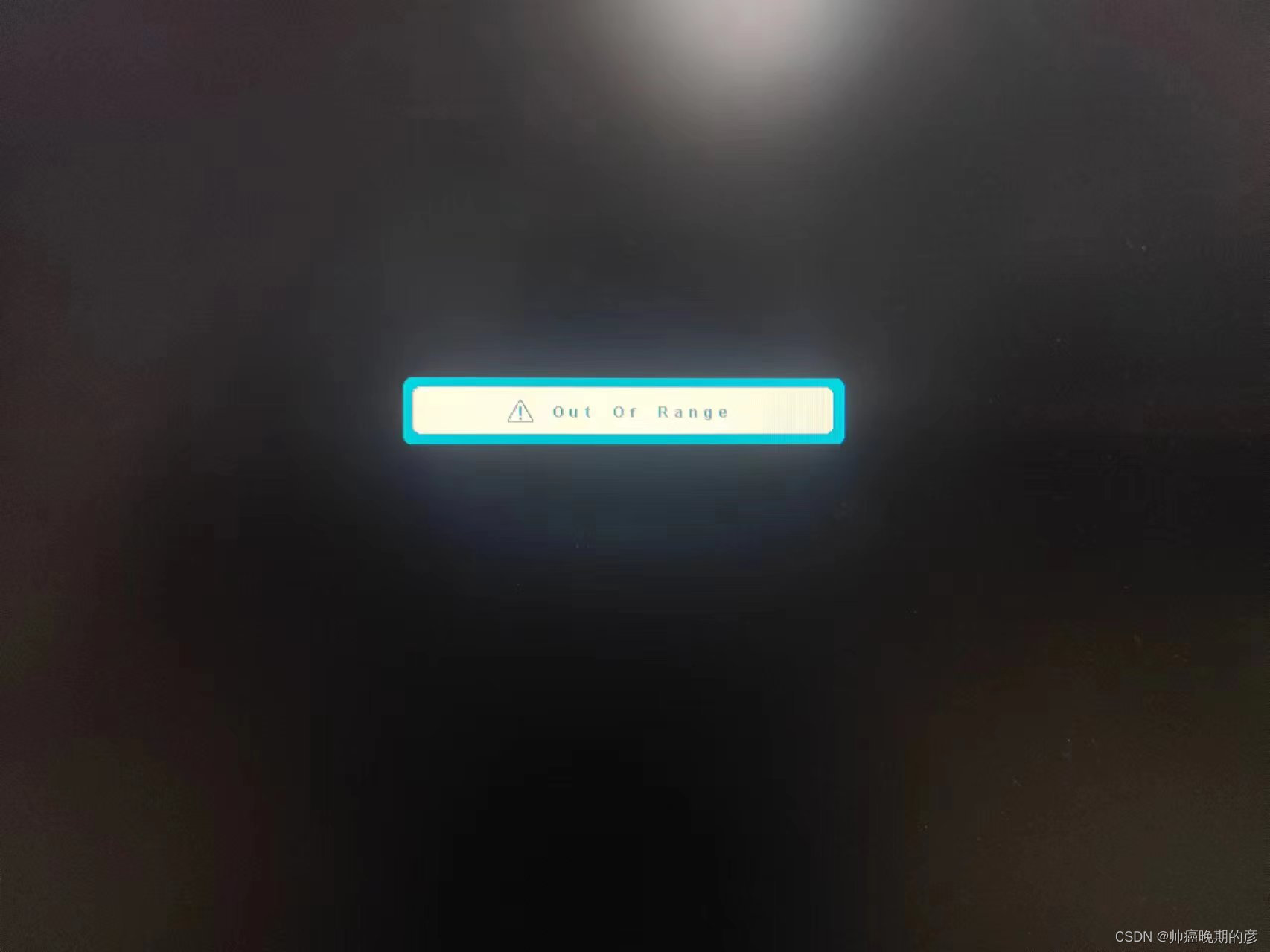

测试千兆视频输出到hdmi,发现显示屏收不了数据

这是因为我的分辨率核刷新率设置的不对。设置成1920108060帧了

测试效果

这里的,可以看到以太网的下发能到达800Mbit/s左右的速率

观看网址

【千兆网和串口下发视频和图片-哔哩哔哩】

https://b23.tv/ppBg8XH

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?