RGMII 接口和 IDDR 原语的使用 和phy芯片

什么是RGMII

-

RGMII 是 Reduced GMII(吉比特介质独立接口)。 RGMII 均采用 4 位数据接口,工作时钟 125MHz,并且在上升沿和下降沿同时传输数据,同时兼 容 MII 所 规 定 的 10/100 Mbps 工 作 方 式 , 支 持 传 输 速 率 :10M/100M/1000Mb/s ,其对应 clk 信号分别为: 2.5MHz/25MHz/125MHz。RGMII 数据结构符合 IEEE 以太网标准,接口定义见 IEEE 802.3-2000。因此传输速率可达 1000Mbps。

-

相较于GMII少了4根数据线,因为是双沿采样。

-

他是phy芯片和fpga芯片连接的接口协议标准

什么是IDDR

属于IOB资源中的挨着接口的ILOGIC,即输入信号处理逻辑

iddr有3种工作模式,使用SAME_EDGE_PIPELINED,一个时钟上升沿下降沿采出的数据q1和q2是对齐的。

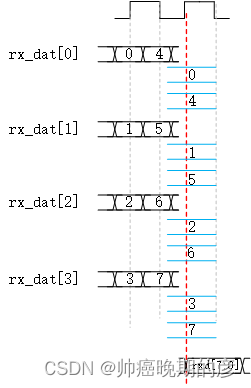

这里给到fpga的线有4根数据线,1根控制线,所以对于每个phy芯片传递过来的时钟,要例化5个iddr原语来采样4根数据线和1根控制使能。数据线 0bit 和 4bit 为一组, 1bit 和 5bit 为一组,2bit 和 6bit 为一组, 3bit 和 7bit 为一组。

代码如下:

generate

genvar i;

for(i=0;i<4;i=i+1) begin

IDDR #(

.DDR_CLK_EDGE("SAME_EDGE_PIPELINED"), // "OPPOSITE_EDGE", "SAME_EDGE"

// or "SAME_EDGE_PIPELINED"

.INIT_Q1(1'b0), // Initial value of Q1: 1'b0 or 1'b1

.INIT_Q2(1'b0), // Initial value of Q2: 1'b0 or 1'b1

.SRTYPE("SYNC") // Set/Reset type: "SYNC" or "ASYNC"

) IDDR_rxd_inst (

.Q1(rxd[i]), // 1-bit output for positive edge of clock

.Q2(rxd[i+4]), // 1-bit output for negative edge of clock

.C(i_rx_clk), // 1-bit clock input

.CE(1'b1), // 1-bit clock enable input

.D(rx_dat[i]), // 1-bit DDR data input

.R(1'b0), // 1-bit reset

.S(1'b0) // 1-bit set

);

end

endgenerate

控制使能:

IDDR #(

.DDR_CLK_EDGE("SAME_EDGE_PIPELINED"), // "OPPOSITE_EDGE", "SAME_EDGE"

// or "SAME_EDGE_PIPELINED"

.INIT_Q1(1'b0), // Initial value of Q1: 1'b0 or 1'b1

.INIT_Q2(1'b0), // Initial value of Q2: 1'b0 or 1'b1

.SRTYPE("SYNC") // Set/Reset type: "SYNC" or "ASYNC"

) IDDR_rxctrl_inst (

.Q1(rxdv), // 1-bit output for positive edge of clock

.Q2(rxerr), // 1-bit output for negative edge of clock

.C(i_rx_clk), // 1-bit clock input

.CE(1'b1), // 1-bit clock enable input

.D(rx_ctrl), // 1-bit DDR data input

.R(1'b0), // 1-bit reset

.S(1'b0) // 1-bit set

);

phy芯片

- 芯片的型号为VITESSE VSC8601

- PHY 芯片配置:可以通过MDIO对phy芯片中的寄存器进行配置PHY Address,可以配置成不同的网络模式,也可以通过CMODE Pin 对应不同电阻配置 PHY Address 及 PHY 模式

- VSC8601 芯片上电后需要进行复位配置, 该芯片复位信号需要在上电保持一段时间后(不少于4ms)才能将复位信号置为高

- 发射端和接收端分别有 6 个引脚与 FPGA 相连,分别有一个时钟引脚、一个数据控制使能引脚,四个数据引脚。

fpga芯片接收到是否收到phy芯片数据的检验

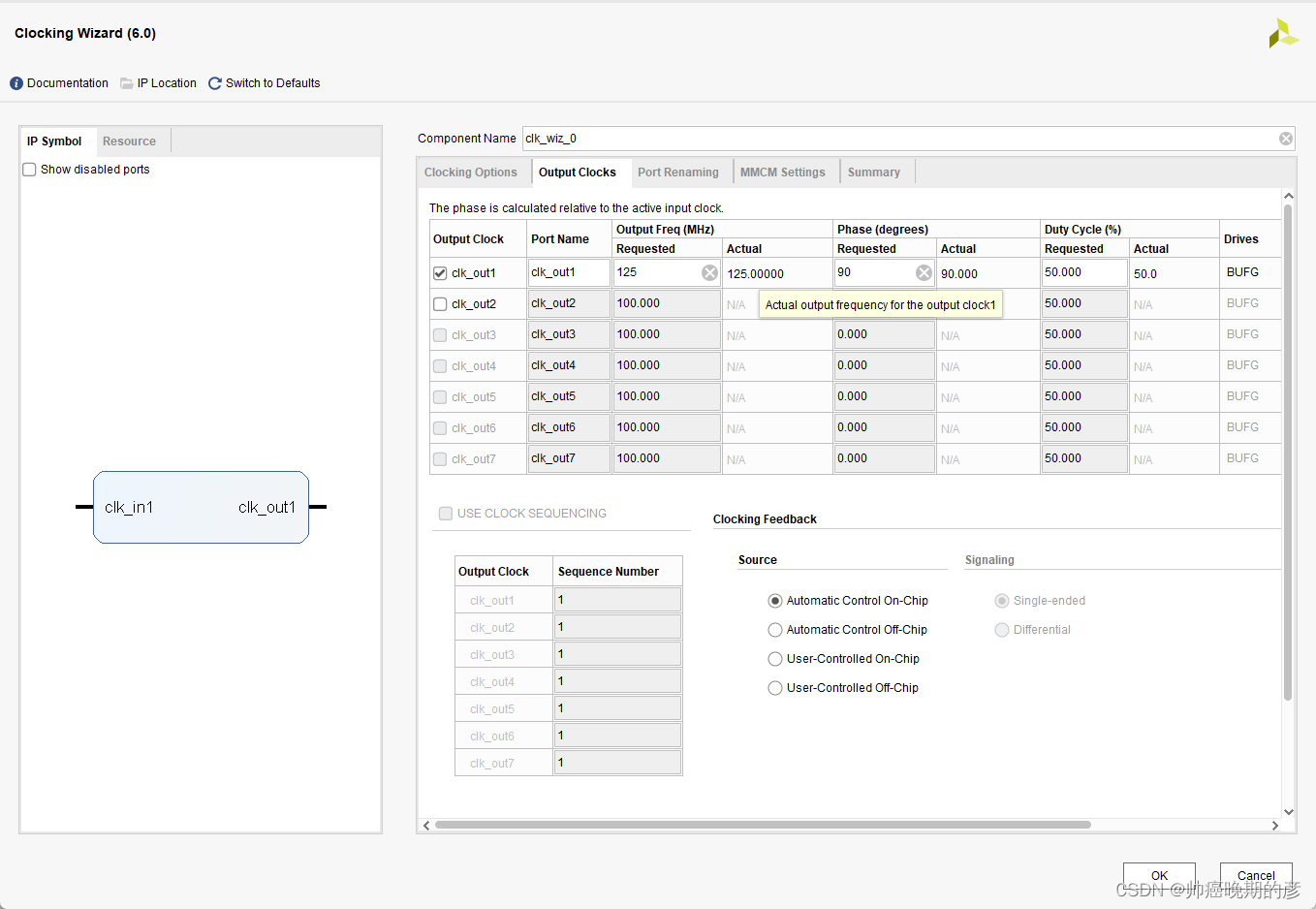

首先phy芯片传过来的时钟和数据达到fpga芯片不一定对的很齐,所以需要把时钟相移一下(后续可以通过约束input delay来解决),然后我们上板去检验是否有抓到arp包,包的正确性,来确定相位

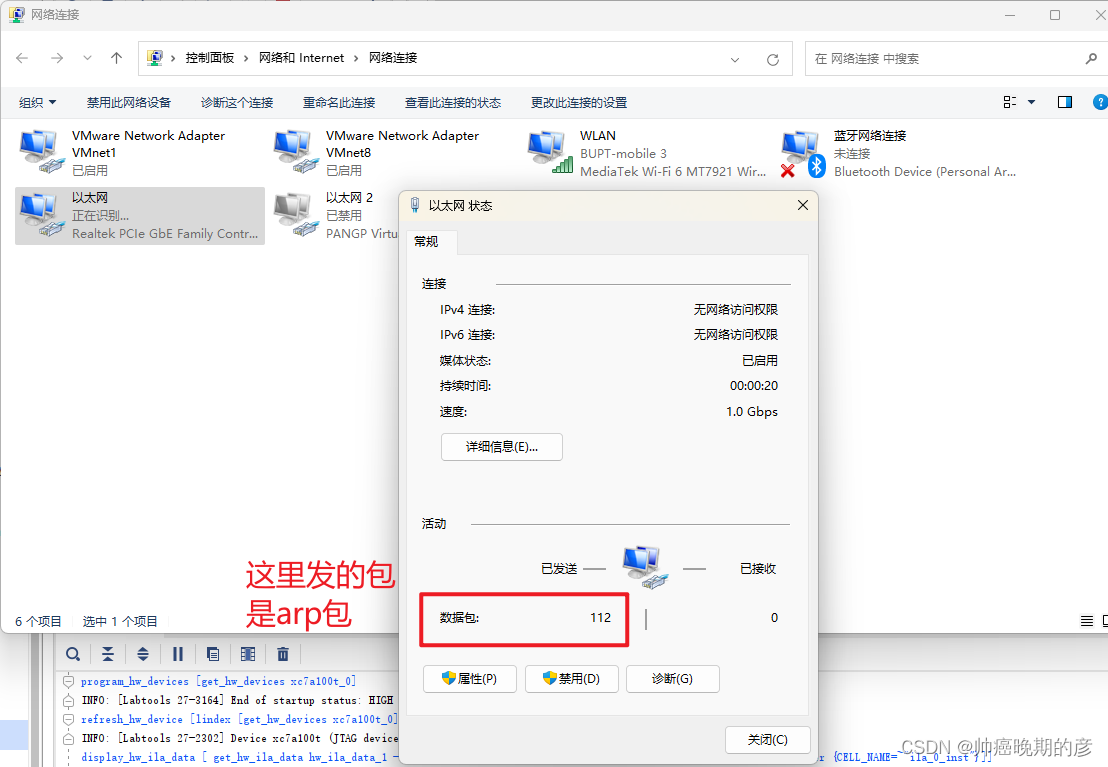

将程序下载后,首先是phy芯片工作,fpga板卡和电脑已经相连

打开网络连接控制面板可以看到,电脑一直在发arp包

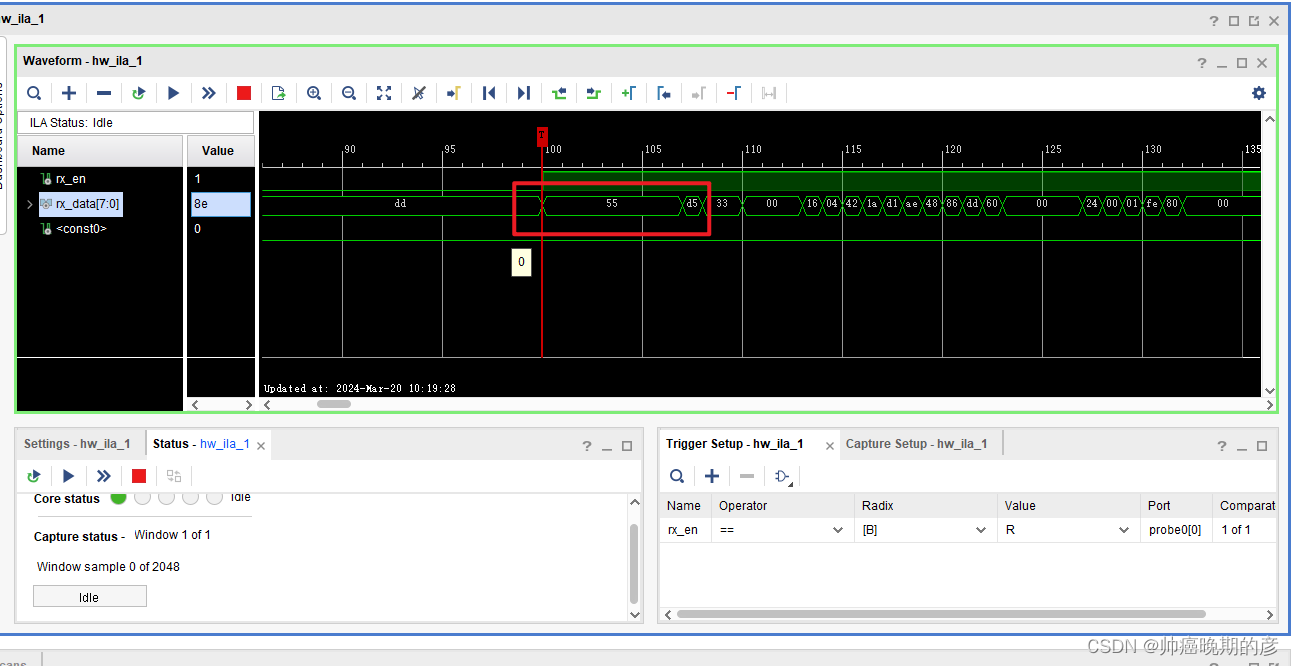

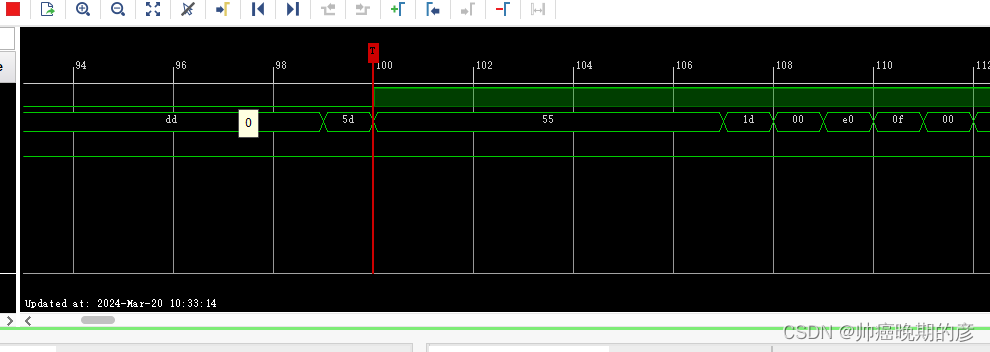

用ila抓一下,看是否能抓到arp包

可以看到抓到了7个55,一个d5的前导序列和sfd,说明我们的iddr捕获时钟的上下沿的数据捕获成功,时钟和数据对齐情况良好,能采集到

现在把时钟的相位调成180,看看能不能成功捕获到

可以看出明显转包错误,说明时钟和数据没有对齐好

1255

1255

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?