MSP430F169——CLOCK

时钟在单片机上十分重要,尤其是以低功耗盛名的TI MSP430系列单片机上,更显得尤为重要,何出此言?我们知道,频率越低,功耗越低,在满足各种设计需要的情况下,我们尽可能将单片机工作频率降低,此时单片机的功耗也就随之降低。MSP430系列单片机之所以有如此低的功耗,正是因为其有一个强大的时钟系统!

那么在430f169这款单片机上,我们该如何去学习它的时钟系统呢?

接下来,我将带领大家学习这个时钟系统,让大家对msp430f169的时钟系统有一定了解。

- 时钟系统模块设计要求:

高频率:用于系统硬件需求和外部事件的快速反应

低频率:用于降低电流消耗

稳定的频率:以满足定时应用,如实时时钟RTC

低成本:用于时钟精度要求不高的场景 - MSP430F169单片机时钟系统概述:

一、三种时钟信号源

1.低频LFXT1CLK(32.768KHz)

可以使用标准晶振,振荡器或者外部时钟源输入4MHz~32MHz。XT1CLK可以作为内部FLL模块的参考时钟。

低频晶振(32.768KHz)经过XIN和XOUT引脚直接连接到单片机,不需要其他外部器件(内部有12pF的负载电容)。此时LFXT1振荡器工作于低频模式(XTS=0)。

如果单片机外接高速品体振荡器或谐振器时,0SCOFF=0可使LFXT1振荡器工作于高频模式(XTS=1)。此时高速品体振荡器或谐振器经过XIN和XOUT引脚连接,并且需要外接电容,电容的大小根据晶体振荡器或谐振器的特性来选择。

如果LFXT1CLK信号没有用作SMCLK或MCIK信号,可用软件将OSCOFF=1以禁止LFXT1工作,从而减少单片机耗电。

BCSCTL1:

XTS(BIT6)——LFXT1高/低速模式选择。0:LFXT1工作在低速晶振模式(默认);1:LFXT1工作在高速晶振模式。

2.高频XT2CLK(8MHz)

可以使用标准晶振,振荡器或者外部时钟源输入4MHz~32MHz。

XT2振荡器产生XT2CLK时钟信号,它的工作特性与LFXT1振荡器工作在高频模式时类似。如果XT2CLK没有用作MCLK和SMCLK时钟信号,可用控制位XT2OFF禁止XT2振荡器。

BCSCTL1:

XT2OFF(BIT7)——XT2高速晶振控制。0:XT2高速晶振开;1:XT2高速晶振关。

3.内部振荡器DCOCLK(1MHz)

通过FLL模块来稳定。

当振荡器失效时,DCO会被自动选为MCLK的时钟源。

DCO振荡器的频率可通过软件对DCOx. MODx和RSEL.x位的设置来调整。当DCOCLK信号没有用作SMCLK和MCLK时钟信号时,可以用控制位SCGO禁止直流发生器。

在PUC信号之后,DCOCLK被自动选作MCLK时钟信号,根据需要,MCLK的时钟源可以另外设置为LFXT1或者XT2。设置顺序如下:

(1)让OSCOFF=1;

(2)让OFIFG=0;

(3)延时等待至少50ps;

(4)再次检查OFIFG,如果OFIFG=1,重复(3) ,(4)步骤,直到OFIFG=0为止。

DCOCTL:

DCOx(BIT7、BIT6、BIT5)——DCO频率选择,选择8种频率,可分段调节DCOCLK频率。该频率选择是建立在RSELx选定的频段上。DCOx、RSELx与内部时钟的关系如图:

MODx(BIT4、BIT3、BIT2、BIT1、BIT0)——DAC调制器设定。控制切换DCOx和DCOx+1选择的两种频率,来微调DCO的输出频率。如果DCOx常数是7,表示已经选择最高频率,此时MODx失效,不能用来进行频率调整。

BCSCTL1:

RSELx(BIT2、BIT1、BIT0)——DCO振荡器的频段选择,该3位控制某个内部电阻以决定标称频率。0:选择最低的标称频率…7:选择最高的标称频率。

BCSCTL2:

DCOR(BIT0)——选择DCO振荡电阻。0:内部电阻;1:外部电阻。

二、三种时钟源

1.ACLK 辅助时钟

ACLK 是LFXT1CLK经1、2、4、8分频后得到的。可作为各个外围模块的时钟信号,一般用于低速外设。

BCSCTL1:

DIVAx(BIT5、BIT4)——ACLK分频选择,分频选择关系如下图:

宏定义:DIVA_0(1分频/不分频)、DIVA_1(2分频)、DIVA_2(4分频)、DIVA_3(8分频)

2.MCLK 系统主时钟

MCLK可由LFXT1CLK、XT2CLK、DCOCLK三者其一经1、2、4、8分频后得到,常用于CPU运行、程序的执行和其他使用高速时钟的模块。

BCSCTL2:

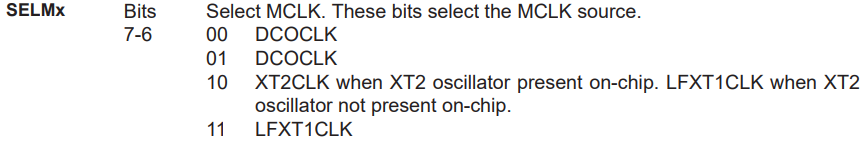

SELMx(BIT7、BIT6)——选择MCLK时钟源,时钟选择关系如下图:

宏定义:SELM_0(DCOCLK默认)、SELM_1(DCOCLK)、SELM_2(XT2CLK)、SELM_3(LFXT1CLK)

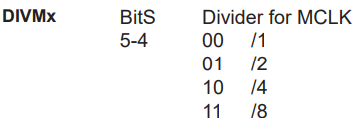

DIVMx(BIT5、BIT4)——MCLK分频选择,分频选择关系如下图:

宏定义:DIVM_0(1分频/不分频)、DIVM_1(2分频)、DIVM_2(4分频)、DIVM_3(8分频)

3.SMCLK 子系统时钟

SMCLK可由XT2CLK、DCOCLK二者其一经1、2、4、8分频后得到,常用于高速外围模

块。

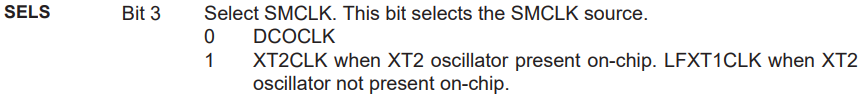

BCSCTL2:

SELSx(BIT3)——选择MCLK时钟源,时钟选择关系如下图:

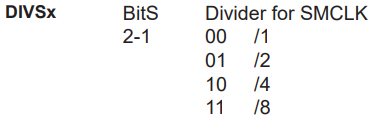

DIVSx(BIT2、BIT1)——SMCLK分频选择,分频选择关系如下图:

宏定义:DIVS_0(1分频/不分频)、DIVS_1(2分频)、DIVS_2(4分频)、DIVS_3(8分频)

三、三种寄存器

1.DCO控制寄存器——DCOCTL

2.基本时钟系统控制寄存器1——BCSCTL1

3.基本时钟系统控制寄存器2——BCSCTL2

四、代码示例

#include <msp430f169.h>

#include "BoardConfig.h

本文介绍了MSP430F169单片机的时钟系统,包括三种时钟信号源:LFXT1CLK、XT2CLK和DCOCLK,以及三种时钟源:ACLK、MCLK和SMCLK。详细讨论了各时钟源的特性和使用,如高低频模式选择、分频控制,并提到了相关的控制寄存器DCOCTL、BCSCTL1和BCSCTL2。文章旨在帮助读者理解并掌握MSP430F169的时钟系统配置。

本文介绍了MSP430F169单片机的时钟系统,包括三种时钟信号源:LFXT1CLK、XT2CLK和DCOCLK,以及三种时钟源:ACLK、MCLK和SMCLK。详细讨论了各时钟源的特性和使用,如高低频模式选择、分频控制,并提到了相关的控制寄存器DCOCTL、BCSCTL1和BCSCTL2。文章旨在帮助读者理解并掌握MSP430F169的时钟系统配置。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

680

680

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?