由cmos到基本逻辑门

cmos

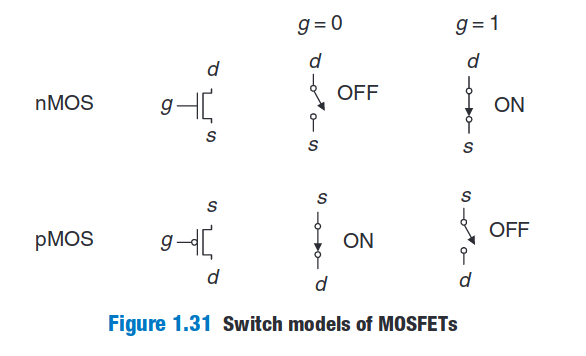

如图所示, g = 0 g=0 g=0时,p管连通,n管断开;否则相反。

Not gate

p p p管在上, n n n管在下;当 A = 1 A=1 A=1, p p p断开, n n n接通, Y Y Y输出GND,即为0。否则 Y Y Y输出 V D D V_{DD} VDD,即为1。

NAND gate

p p p管并联, n n n管串联;根据与非的逻辑, A , B A,B A,B只要有任何一个为0,就会输出1;只有全1,才会输出0。

NOR gate

p p p管串联, n n n管并联;根据或非的逻辑, A , B A,B A,B只要有任何一个为1,就会输出0;只有全0,才会输出1。

参考资料

[1] Digital Design and Computer Architecture RISC-V Edition by Sarah Harris, David Harris

937

937

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?