测试仿真流程

测试仿真环境为win系统下的quartus prime + modelsim

测试仿真流程参照我之前的教程

Verilog数字系统设计教程第4版夏宇闻——第三部分练习一

模块源代码

//----------P_S.v----------

`define YES 1

`define NO 0

module P_S(Dbit_out,link_S_out,data,nGet_AD_data,clk);

input clk; //主时钟节拍

input nGet_AD_data; //负电平有效时取并行数据控制信号线

input[7:0] data; //并行输入的数据端口

output Dbit_out; //串行位流的输出

output link_S_out; //允许串行位流输出的控制信号

reg[3:0] state; //状态变量寄存器

reg[7:0] data_buf; //并行数据缓存器

reg link_S_out; //串行位流输出的控制信号寄存器

reg d_buf; //位缓存器

reg finish_flag; //字节处理结束标志

assign Dbit_out = (link_S_out)?d_buf:0;//给出串行数据

always@(posedge clk or negedge nGet_AD_data) //nGet_AD_data下降沿置数,寄存器清零,clk上跳沿送出位流

if(!nGet_AD_data)

begin

finish_flag <= 0;

state <= 9;

link_S_out <= `NO;

d_buf <= 0;

data_buf <= 0;

end

else

case(state)

9:

begin

data_buf <= data;

state <= 10;

link_S_out <= `NO;

end

10:

begin

data_buf <= data;

state <= 0;

link_S_out <= `NO;

end

0:

begin

link_S_out <= `YES;

d_buf <= data_buf[7];

state <= 1;

end

1:

begin

d_buf <= data_buf[6];

state <= 2;

end

2:

begin

d_buf <= data_buf[5];

state <= 3;

end

3:

begin

d_buf <= data_buf[4];

state <= 4;

end

4:

begin

d_buf <= data_buf[3];

state <= 5;

end

5:

begin

d_buf <= data_buf[2];

state <= 6;

end

6:

begin

d_buf <= data_buf[1];

state <= 7;

end

7:

begin

d_buf <= data_buf[0];

state <= 8;

end

8:

begin

link_S_out <= `NO;

state <= 4'b1111; //do nothing state

finish_flag <= 1;

end

default:

begin

link_S_out <= `NO;

state <= 4'b1111; //do nothing state

end

endcase

endmodule

//----------S_P.v----------

`timescale 1ns/1ns

`define YES 1

`define NO 0

module S_P(data,Dbit_in,Dbit_ena,clk);

output[7:0] data; //并行数据输出口

input Dbit_in,clk; //字节位流输出口

input Dbit_ena; //字节位流使能输出口

reg[7:0] data_buf;

reg[3:0] state; //状态变量寄存器

reg p_out_link; //并行输出控制寄存器

assign data = (p_out_link==`YES)?data_buf:8'bz;

always@(negedge clk)

if(Dbit_ena)

case(state)

0:

begin

p_out_link <= `NO;

data_buf[7] <= Dbit_in;

state <= 1;

end

1:

begin

data_buf[6] <= Dbit_in;

state <= 2;

end

2:

begin

data_buf[5] <= Dbit_in;

state <= 3;

end

3:

begin

data_buf[4] <= Dbit_in;

state <= 4;

end

4:

begin

data_buf[3] <= Dbit_in;

state <= 5;

end

5:

begin

data_buf[2] <= Dbit_in;

state <= 6;

end

6:

begin

data_buf[1] <= Dbit_in;

state <= 7;

end

7:

begin

data_buf[0] <= Dbit_in;

state <= 8;

end

8:

begin

p_out_link <= `YES;

state <= 4'b1111;

end

default: state <= 0;

endcase

else

begin

p_out_link <= `YES;

state <= 0;

end

endmodule

//----------sys.v----------

module sys(databus,use_p_in_bus,Dbit_out,Dbit_ena,nGet_AD_data,clk);

input nGet_AD_data; //取并行数据的控制信号

input use_p_in_bus; //并行总线用于输入数据的控制信号

input clk; //主时钟

inout[7:0] databus; //双向并行数据总线

output Dbit_out; //字节位流输出

output Dbit_ena; //字节位流输出使能

wire clk;

wire nGet_AD_data;

wire Dbit_out;

wire Dbit_ena;

wire[7:0] data;

assign databus = (!use_p_in_bus)?data:8'bzzzz_zzzz;

P_S m0(.Dbit_out(Dbit_out),.link_S_out(Dbit_ena),.data(databus),.nGet_AD_data(nGet_AD_data),.clk(clk));

S_P m1(.data(data),.Dbit_in(Dbit_out),.Dbit_ena(Dbit_ena),.clk(clk));

endmodule

测试模块代码

//----------sys.vt----------

`timescale 1 ns/ 1 ns

module sys_vlg_tst();

reg clk;

reg[7:0] data_buf;

reg nGet_AD_data;

reg D_Pin_ena; //并行数据输入sys模块的使能信号寄存器

wire[7:0] data;

wire clk2;

wire Dbit_ena;

assign data = (D_Pin_ena)?data_buf:8'bz;

initial

begin

clk = 0;

nGet_AD_data = 1; //置取数据控制信号初始值为高电平

data_buf = 8'b1001_1001; //假设数据缓存器的初始值,可用于模拟并行数据的变化

D_Pin_ena = 0;

end

initial

begin

repeat(100)

begin

#(100*14+{$random}%23) nGet_AD_data=0; //取并行数据并开始

#(112+{$random}%12) nGet_AD_data=1; //保持一定时间低电平后恢复高电平

#({$random}%50) D_Pin_ena=1; //并行数据输入sys模块的使能信号有效

#(100*3+{$random}%5) D_Pin_ena=0; //保持三个时钟周期后让出总线

#333 data_buf=data_buf+1; //假设数据变化,可为下次取得不同的数据

#(100*11+{$random}%1000);

end

end

always #(50+$random%2) clk = ~clk; //主时钟的产生

sys i1 (

.Dbit_ena(Dbit_ena),

.Dbit_out(Dbit_out),

.clk(clk),

.databus(data),

.nGet_AD_data(nGet_AD_data),

.use_p_in_bus(D_Pin_ena)

);

endmodule

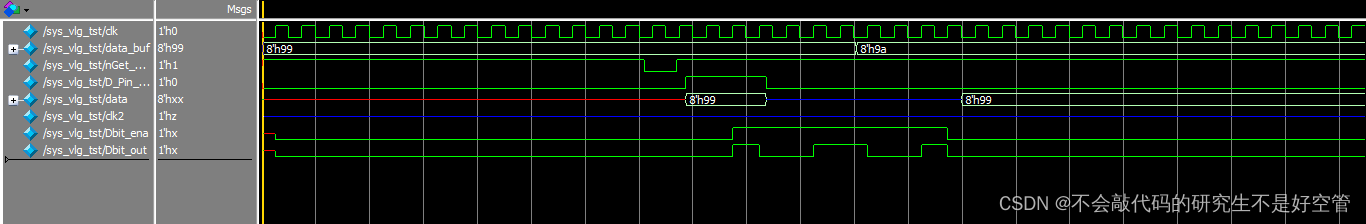

结果波形

3483

3483

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?