计算机系统概述

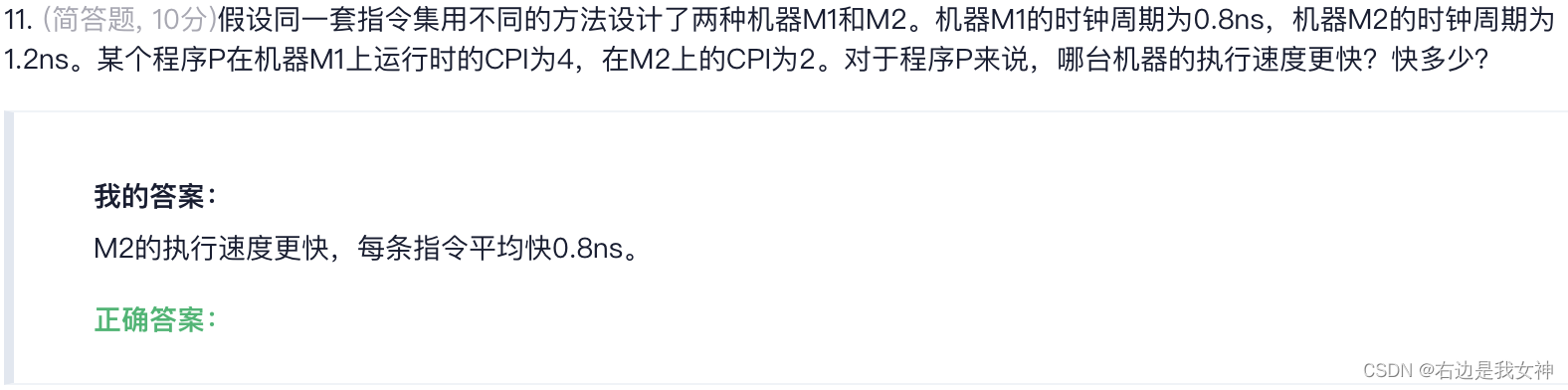

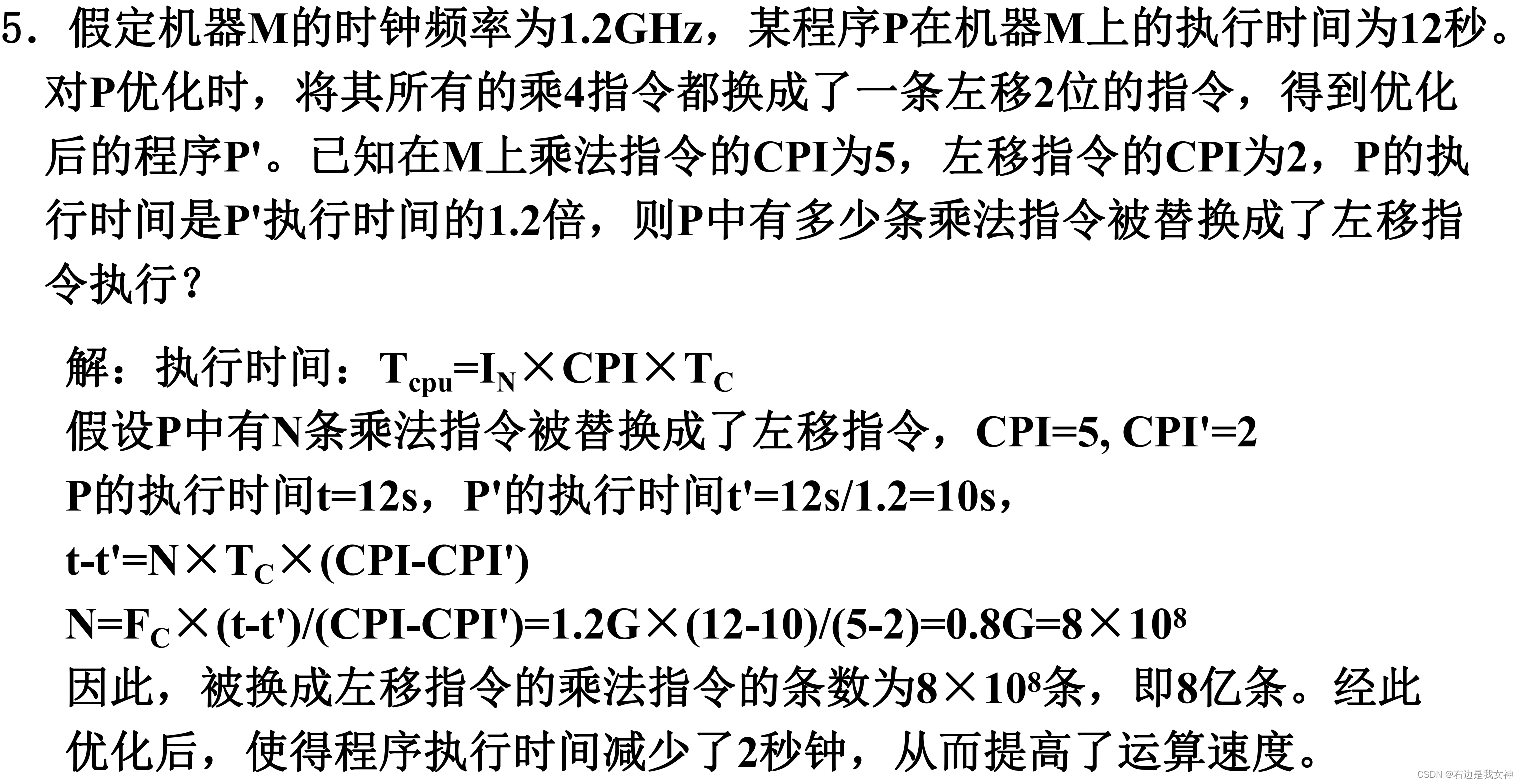

MIP CPI Tc Fc相关的各种运算。

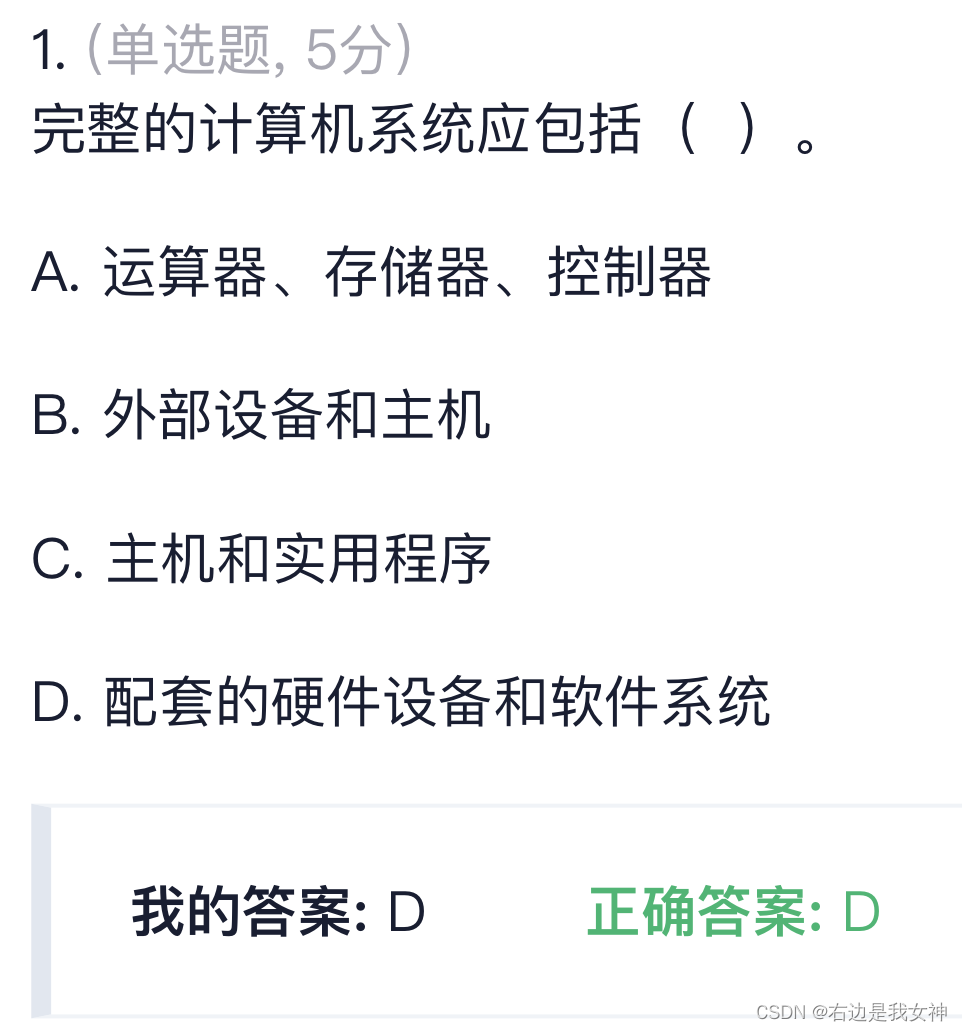

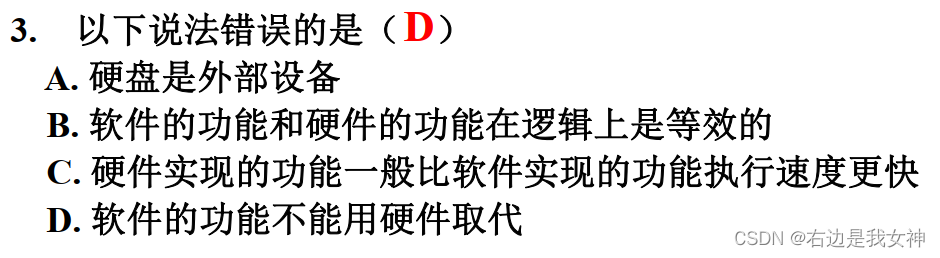

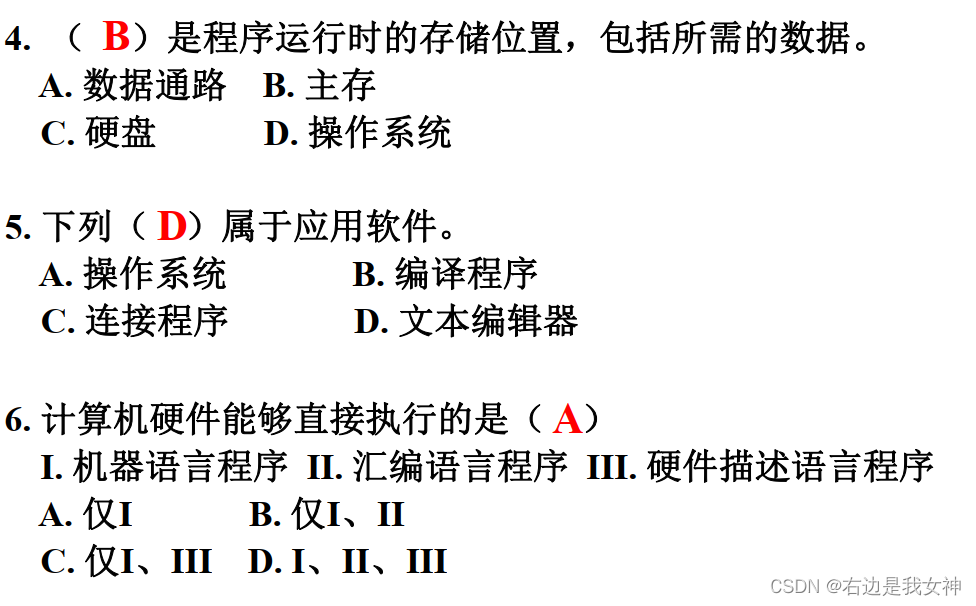

计算机系统硬件组成有:运算器、控制器、存储器、输入设备、输出设备。

冯诺伊曼机的特点有:

- 包含…五个部分;

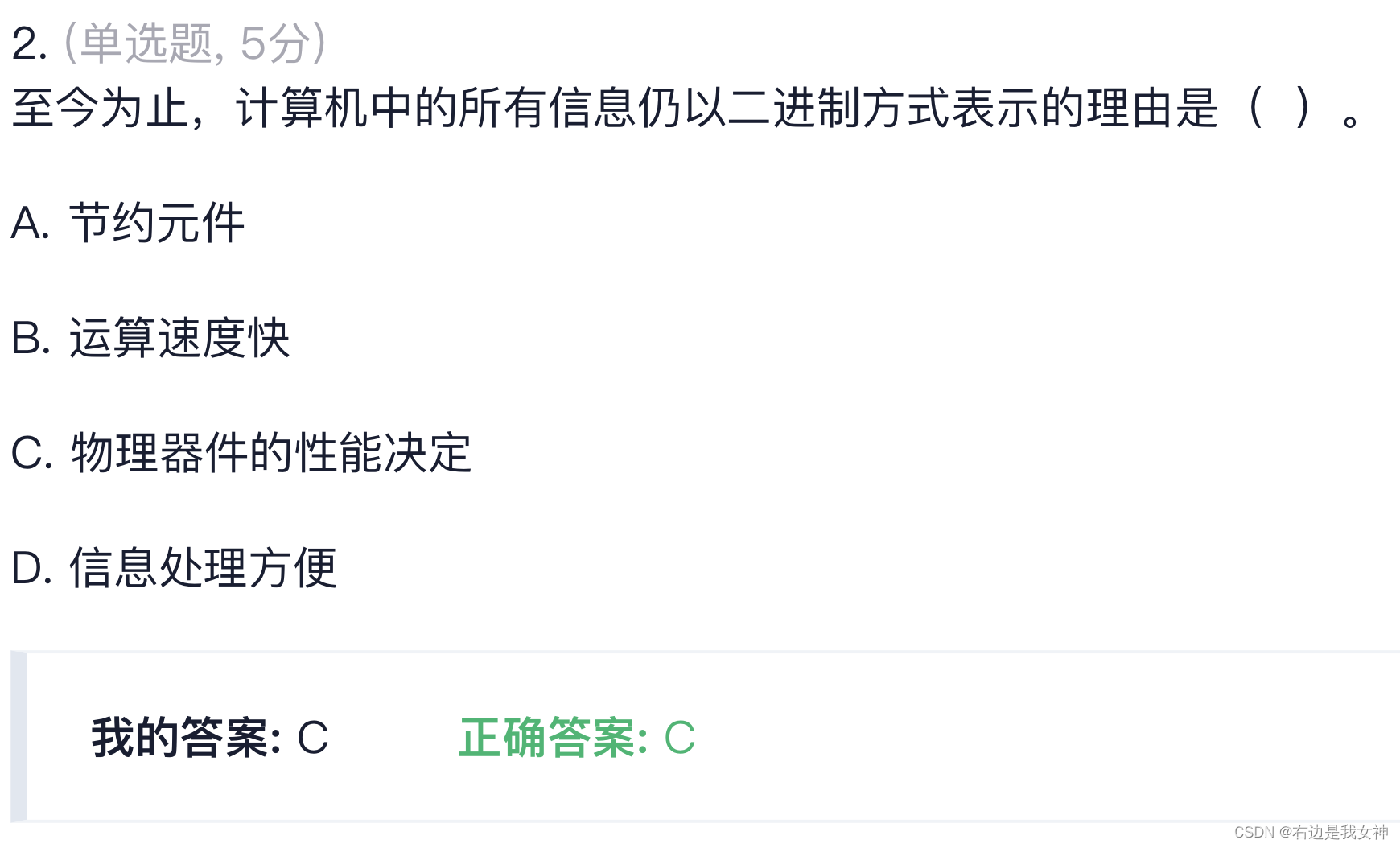

- 以二进制代码表示程序和数据;

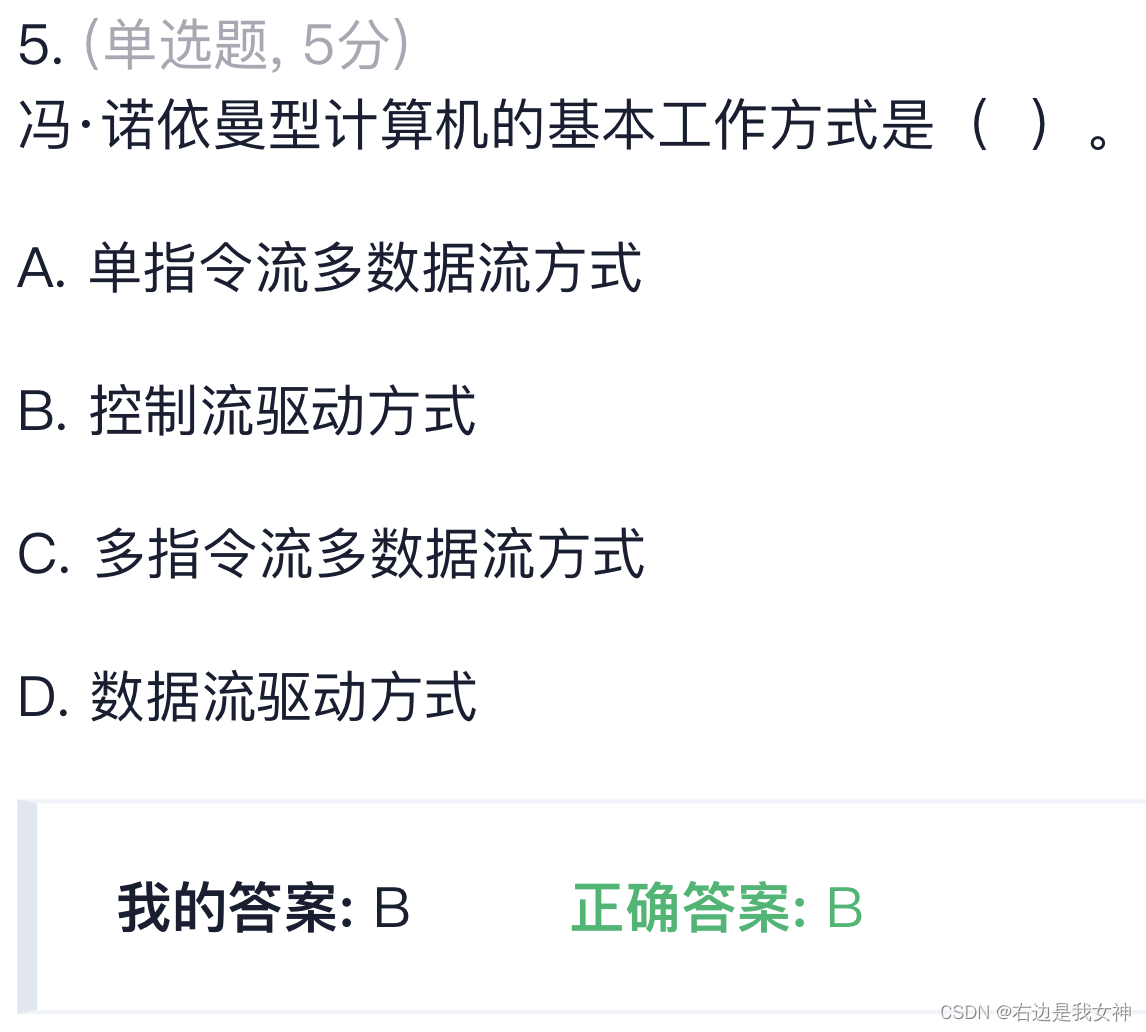

- 采用存储程序的工作方式:程序和数据事先放在同一存储器中,由指令组成的程序可以修改;

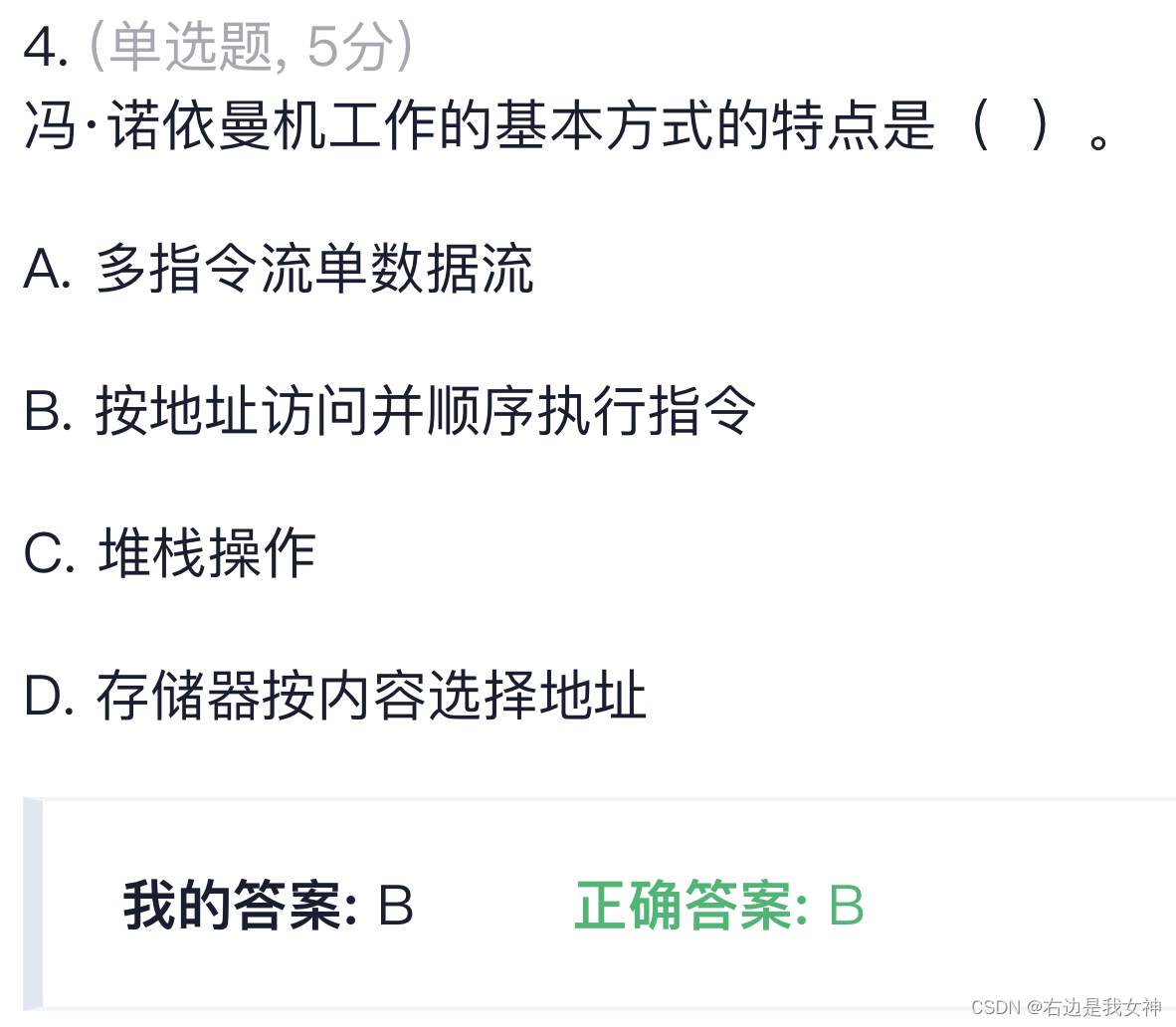

- 指令在存储器中按执行顺序存放,由指令计数器指明要执行的指令所在的单元地址,一般按顺序递增;

- 机器以运算器为中心,数据传送都经过运算器。

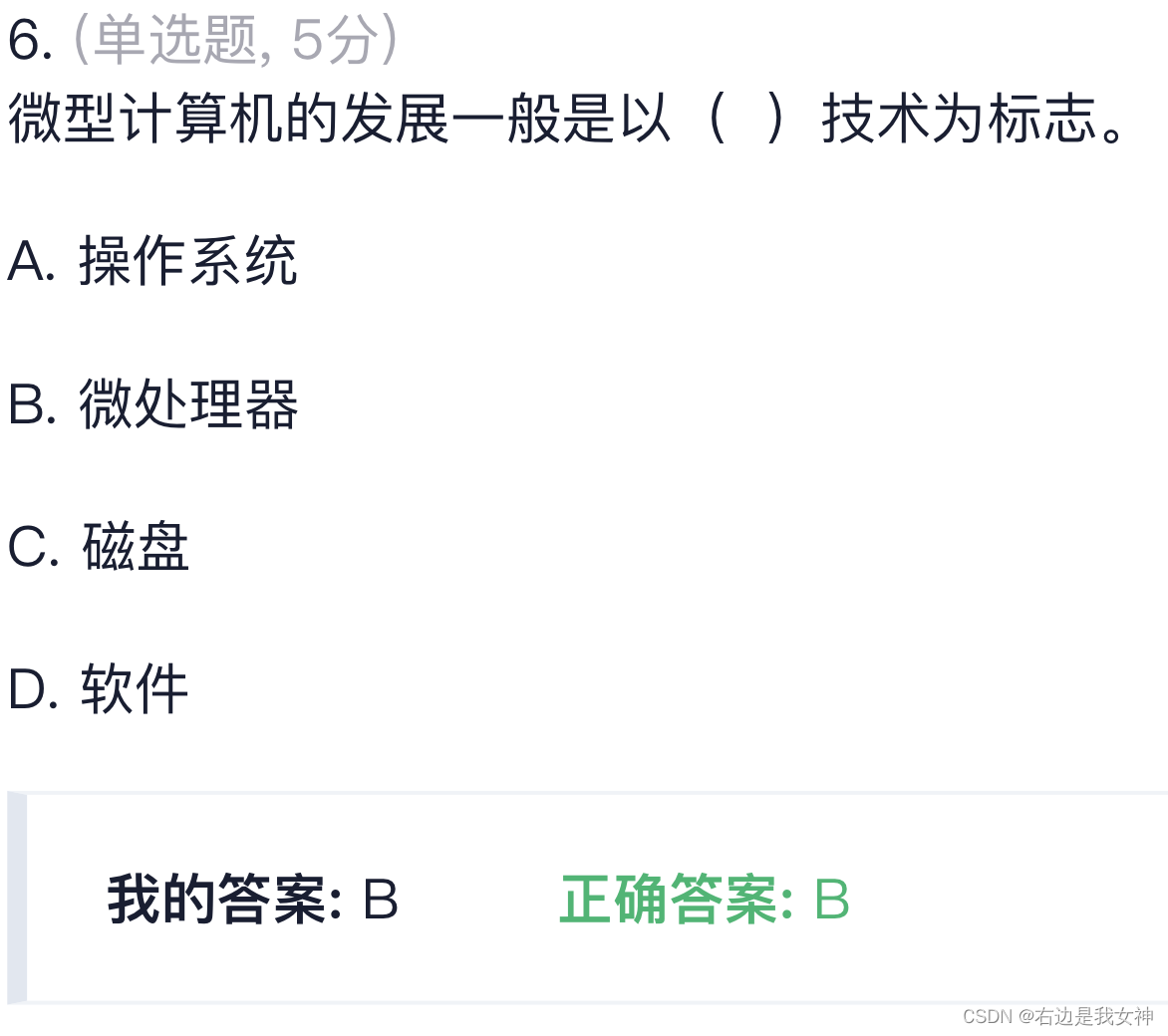

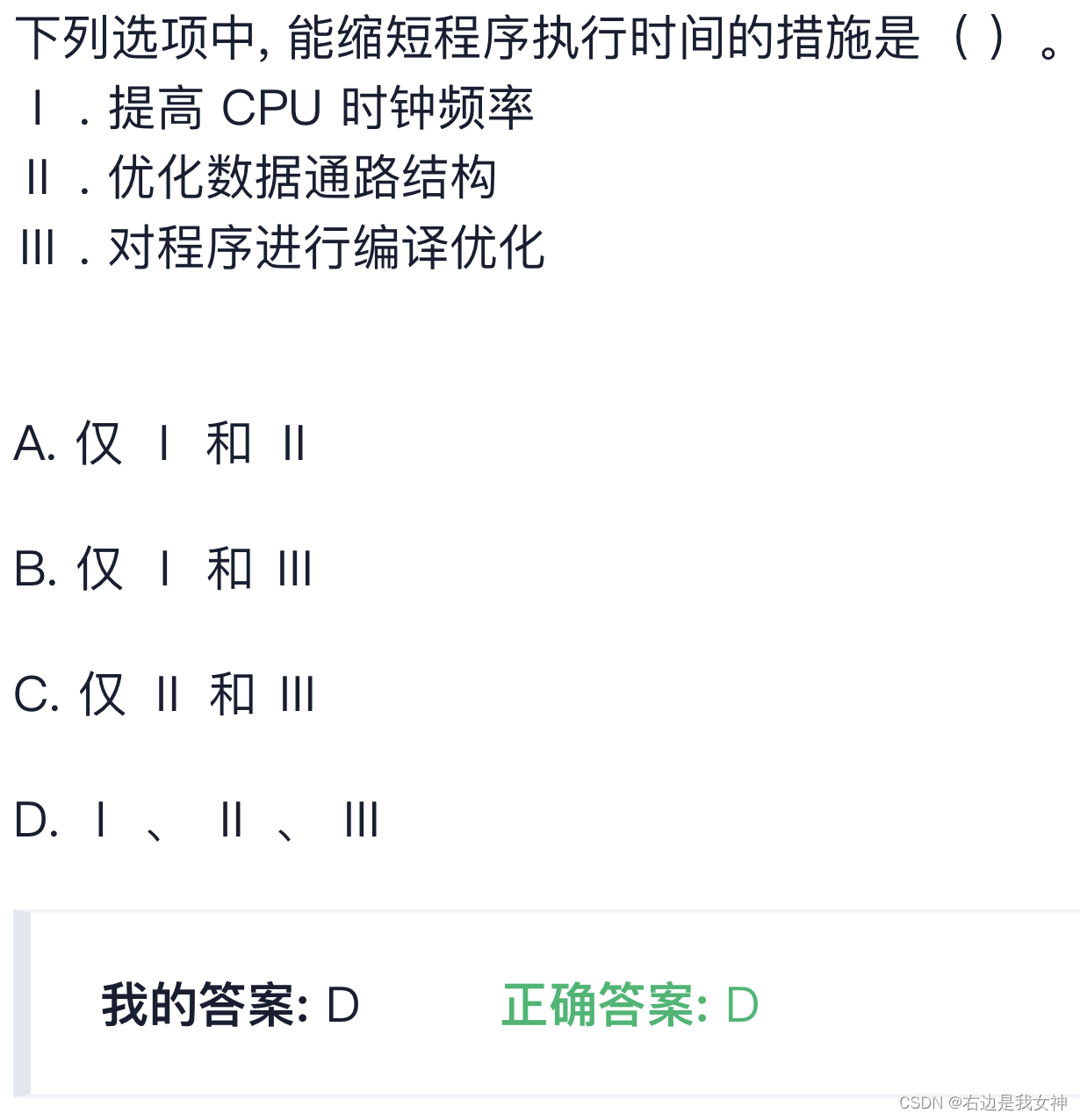

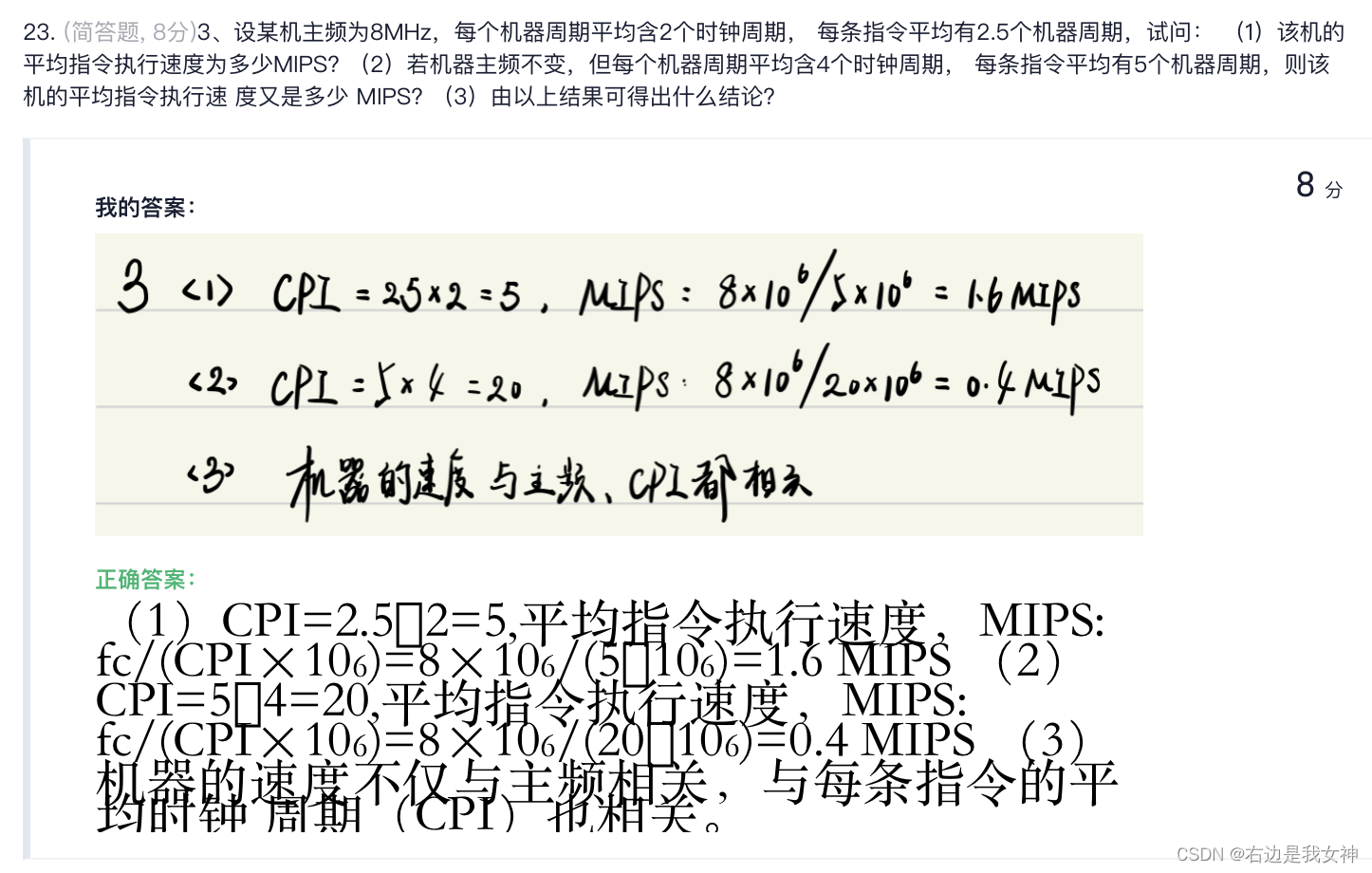

主频,即CPU内核工作的时钟频率,影响实际的运算速度,但并不起决定作用。

CPU主频记为 F c F_c Fc;

CPU时钟周期:主频的倒数, T c = 1 F c T_c=\frac{1}{F_c} Tc=Fc1;

CPI:执行一条指令所需要的平均时钟周期数;

CPU执行时间: T C P U = I N × C P I × T C T_{CPU}=I_N\times CPI\times T_C TCPU=IN×CPI×TC;

MIPS:CPU每秒钟平均执行的整数指令条数(百万条) I N T C P U × 1 0 6 \frac{I_N}{T_{CPU}\times10^6} TCPU×106IN

C P I = ∑ i = 1 n ( C P I i × I i ) I N CPI=\frac{\sum_{i=1}^n(CPI_i\times I_i)}{I_N} CPI=IN∑i=1n(CPIi×Ii)

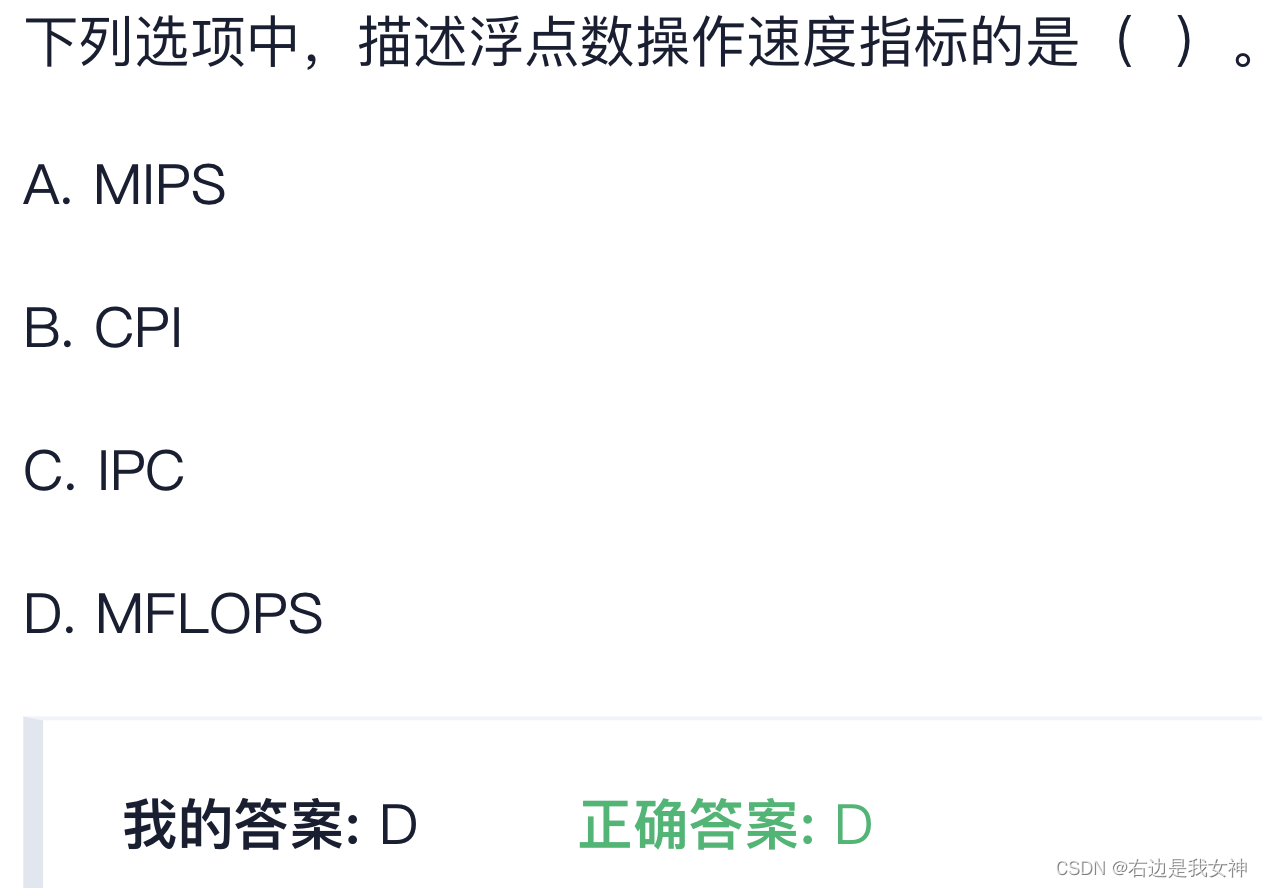

MFLOPS: I f N T C P U × 1 0 6 \frac{I_{fN}}{T_{CPU}\times 10^6} TCPU×106IfN

主存容量:主存中存放的二进制代码的总位数 =存储单元个数*存储字长。

比较每条指令的运行时间即可。

数据的表示和运算

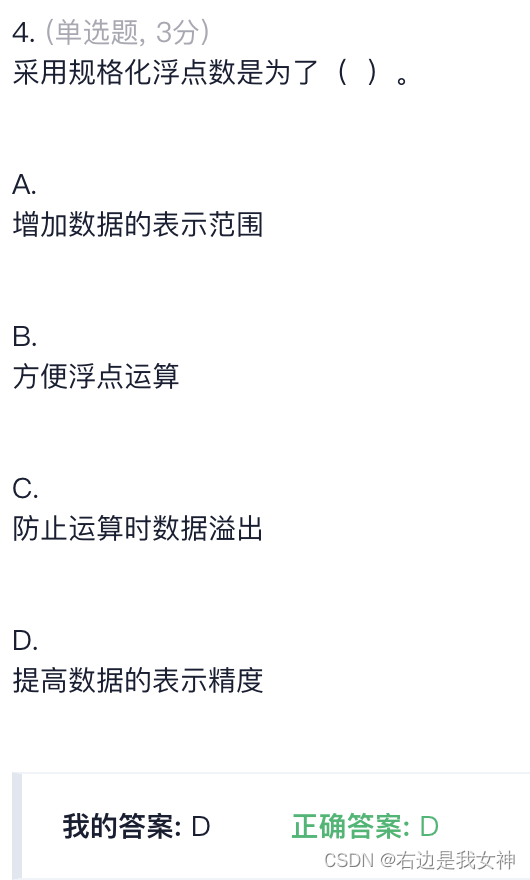

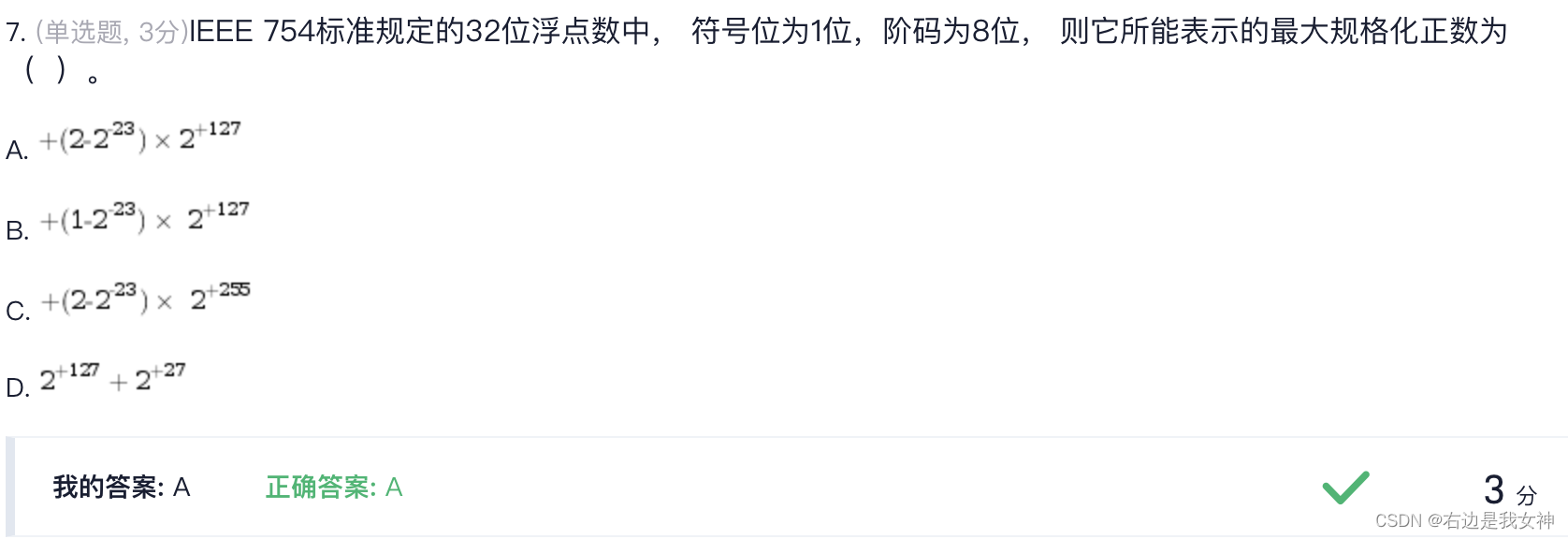

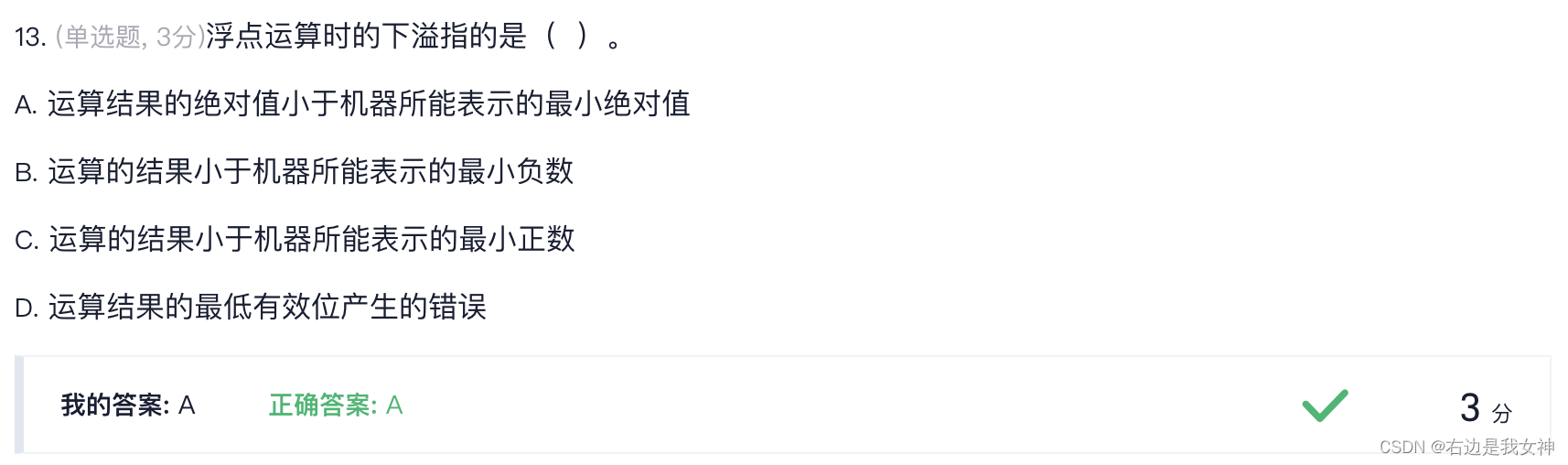

定点数的乘法、浮点数的加法、IEEE745的表示。

因为被规约了,所以阶码的范围在-126~127。

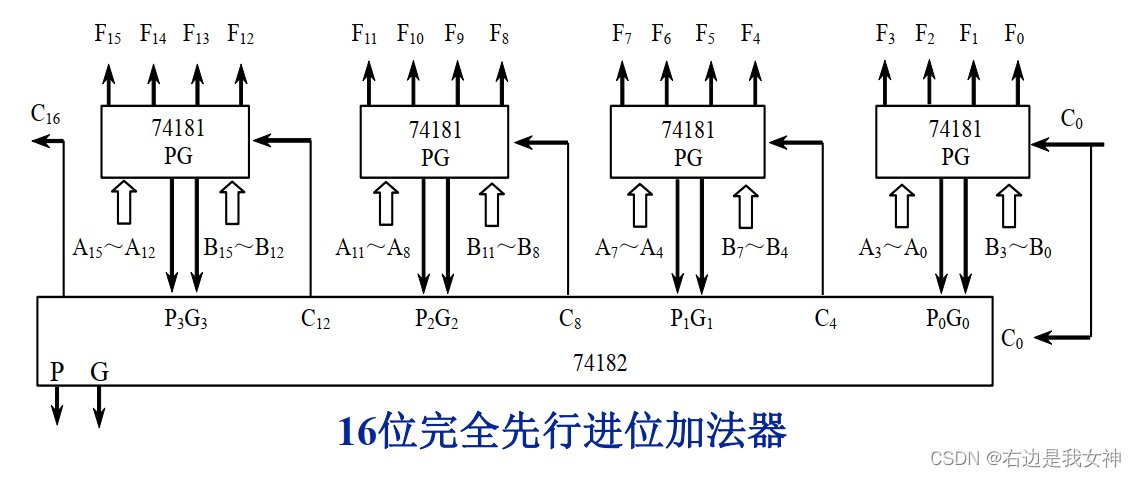

4片74181电路可以组成16位ALU,片内为并行进位,片间为串行进位。

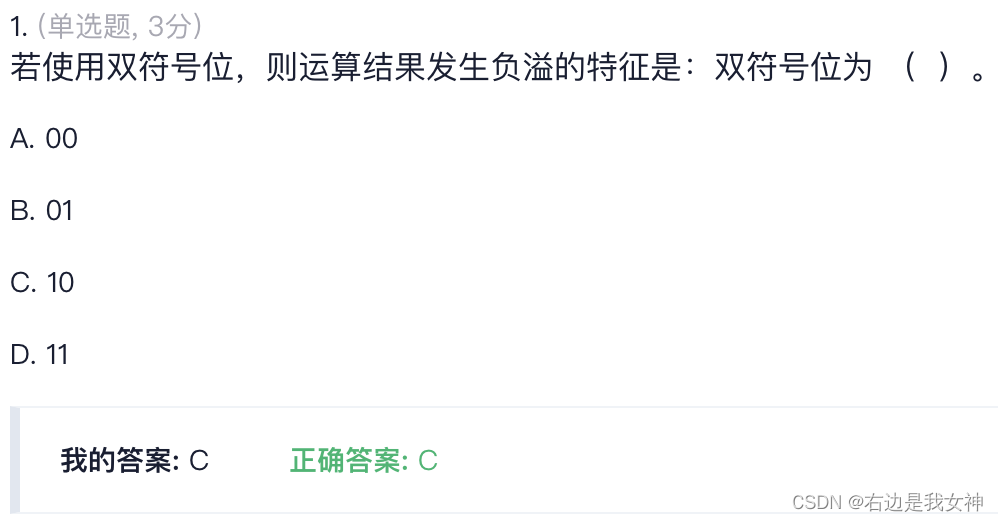

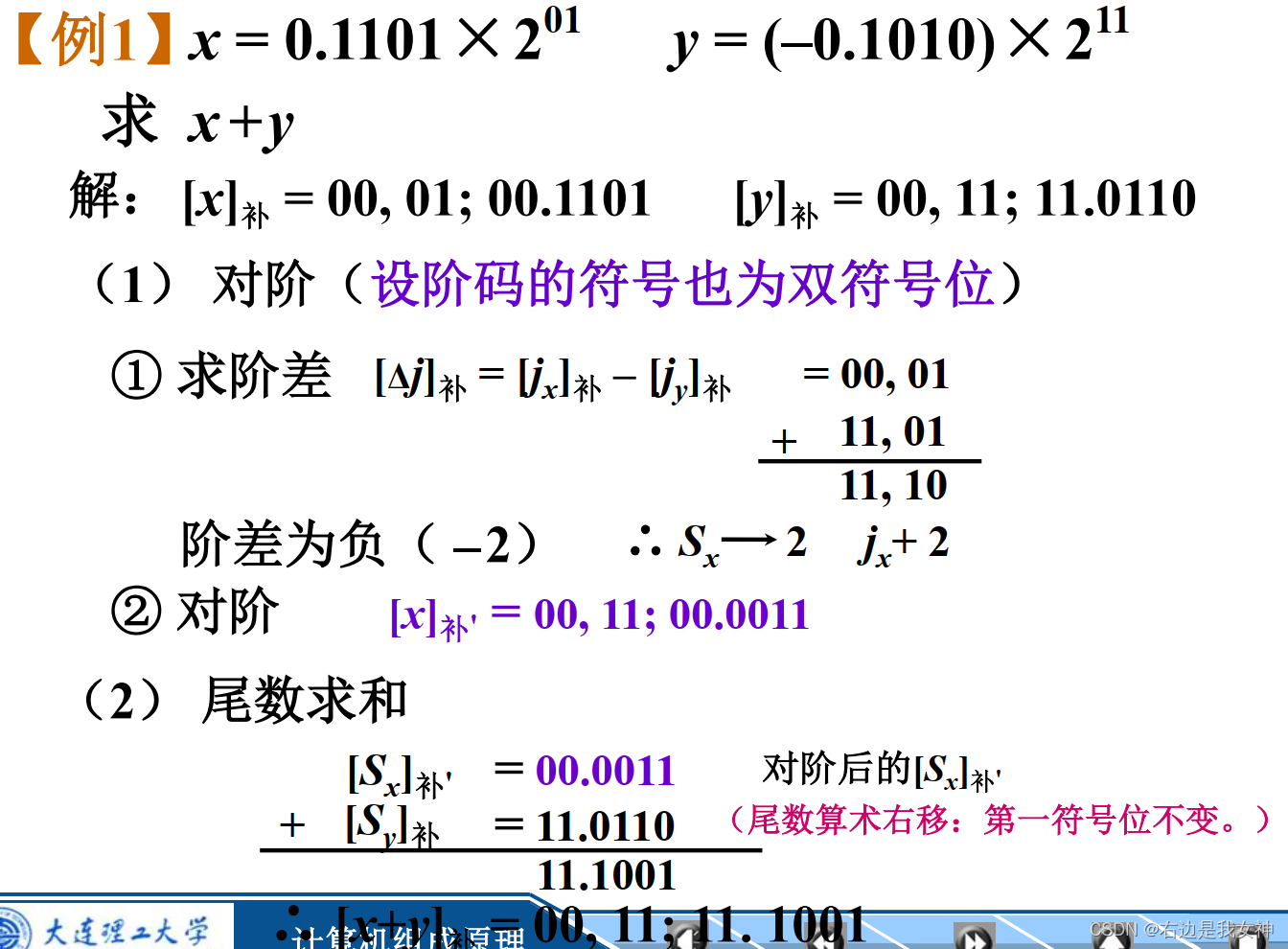

先表示为补码形式,务必双符号位。

然后求阶差,负则前数的尾数右移,阶数加。

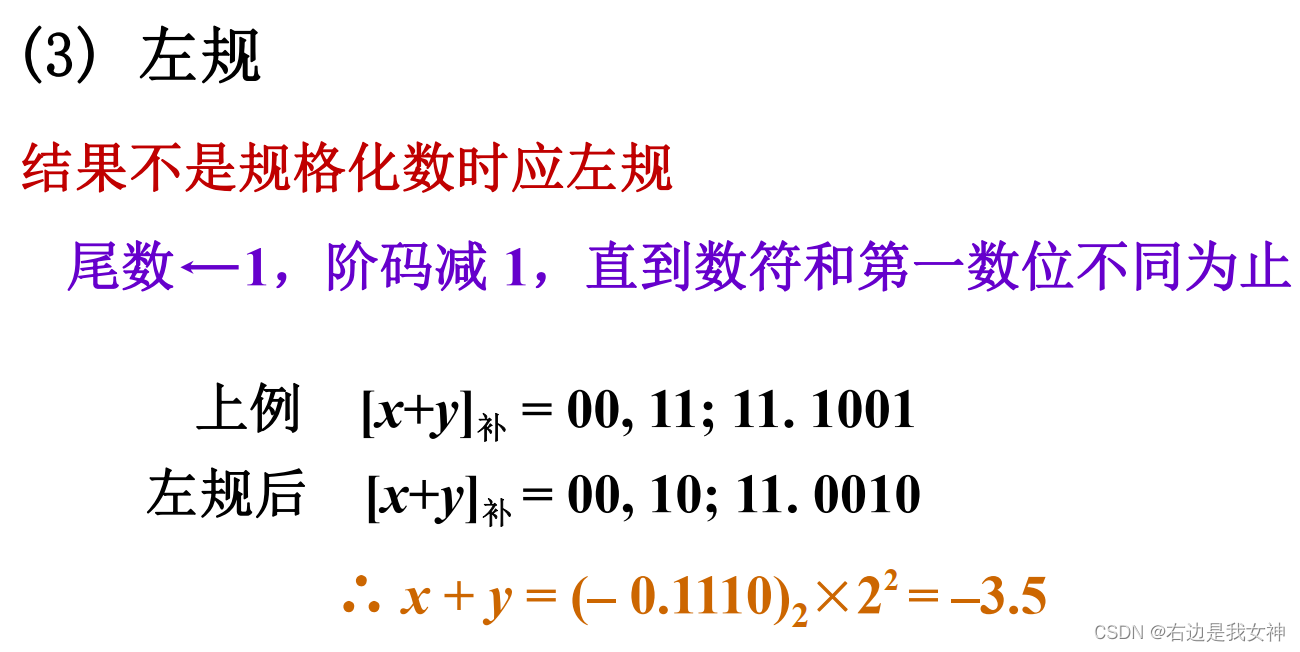

之后尾数求和,根据结果进行规格化。

左规:尾数左移,阶数减;

右规:尾数右移,阶数加。

符号位参与加减法运算。

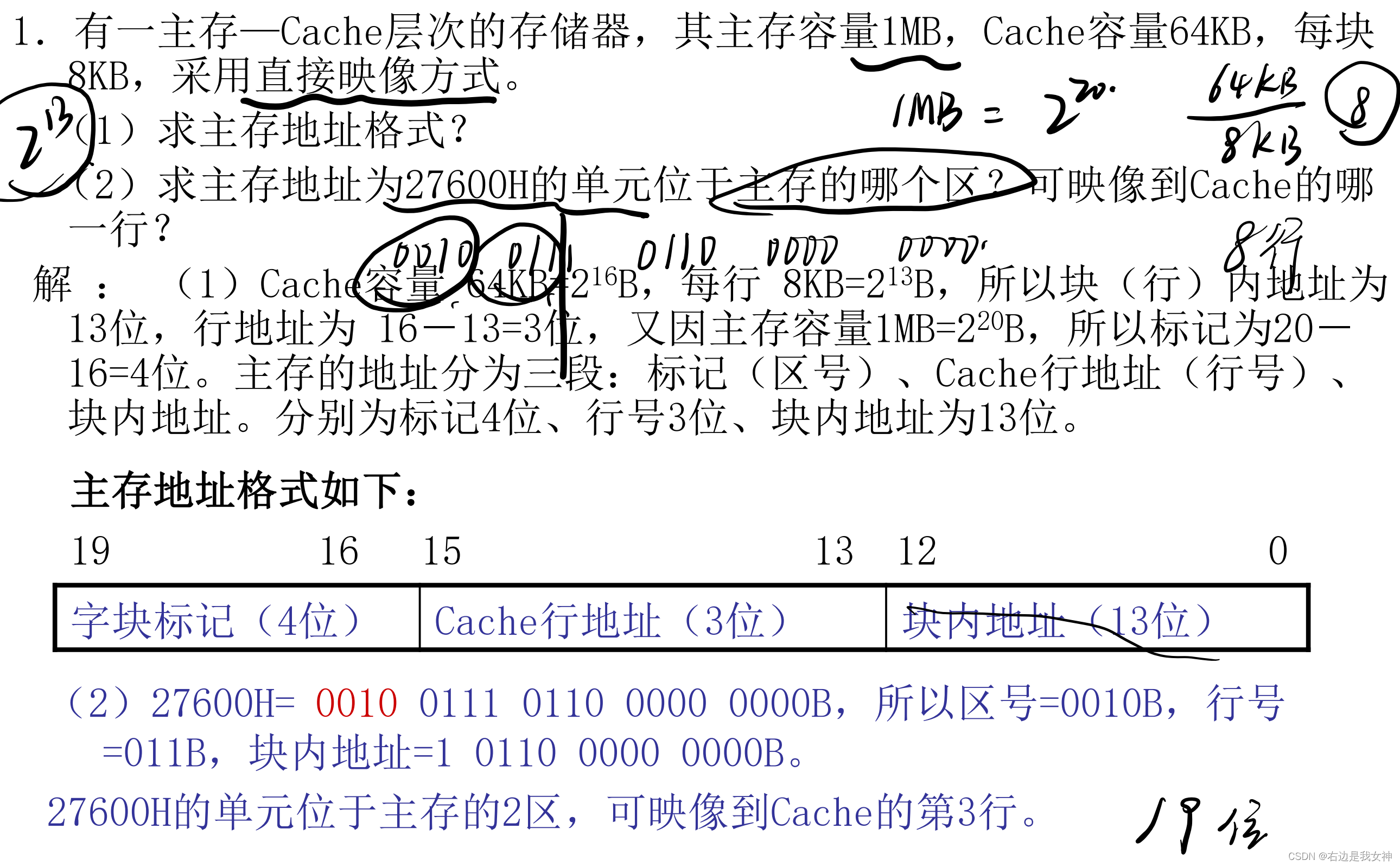

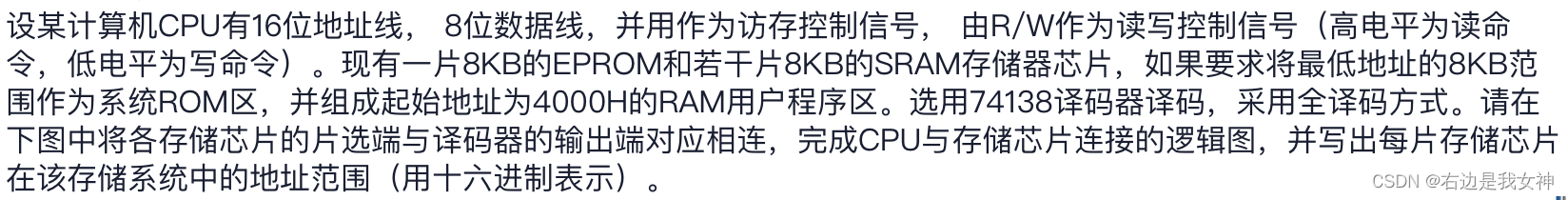

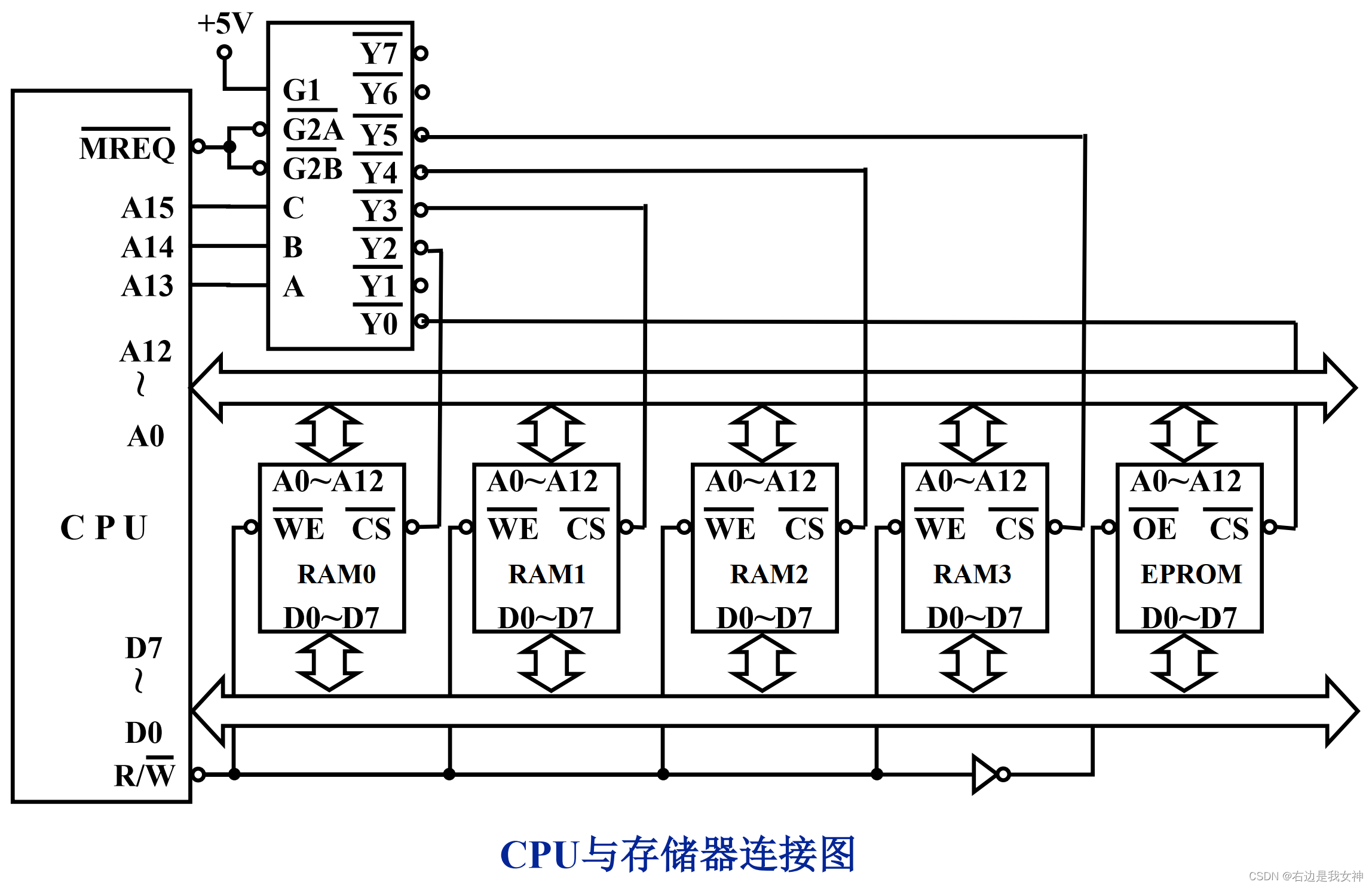

存储器系统

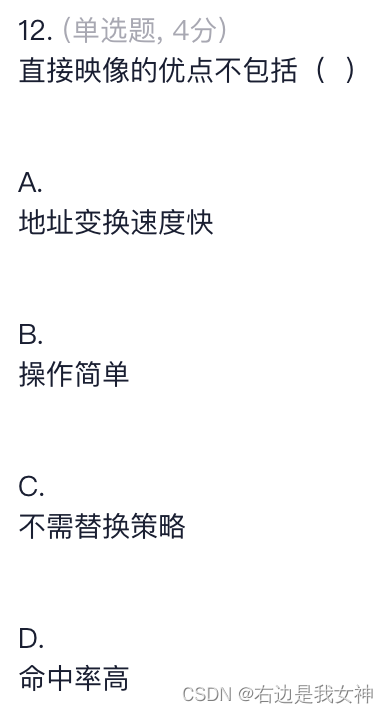

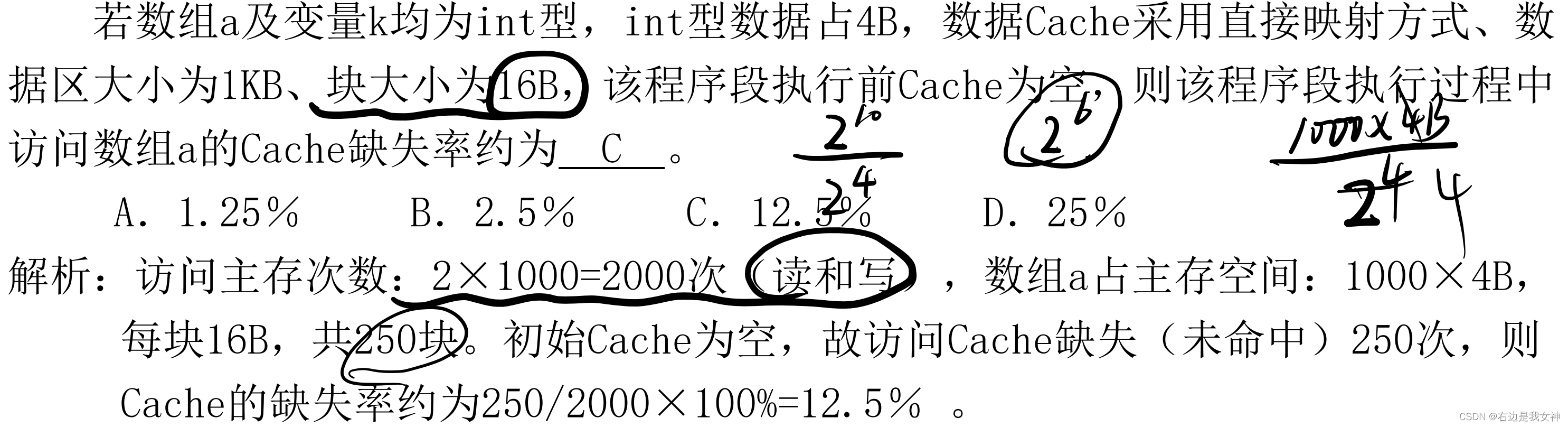

主存地址的划分、特定块的区号、组号、命中率的计算

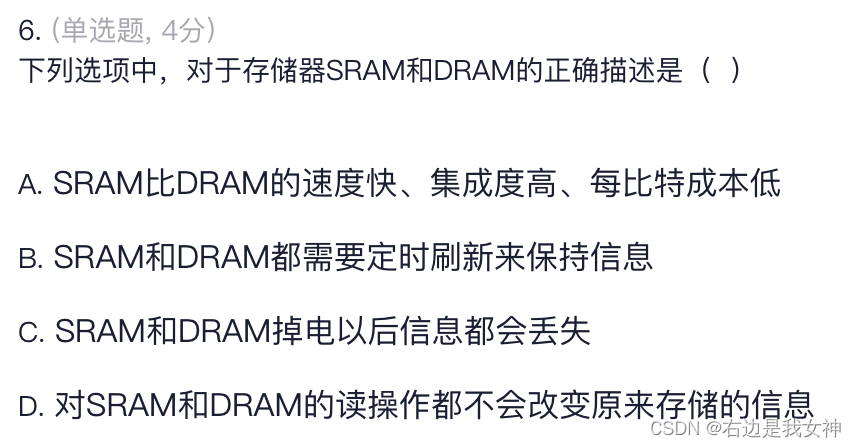

SRAM存储原理:双稳态电路内部的交叉反馈机制。

DRAM存储原理:电容存储电荷的原理。

刷新一块芯片所需的刷新周期数由芯片矩阵的行数决定。

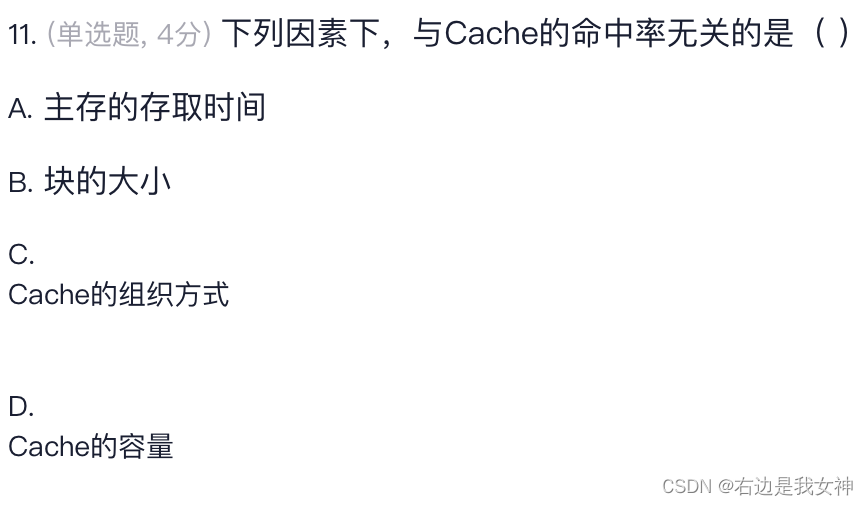

选C。

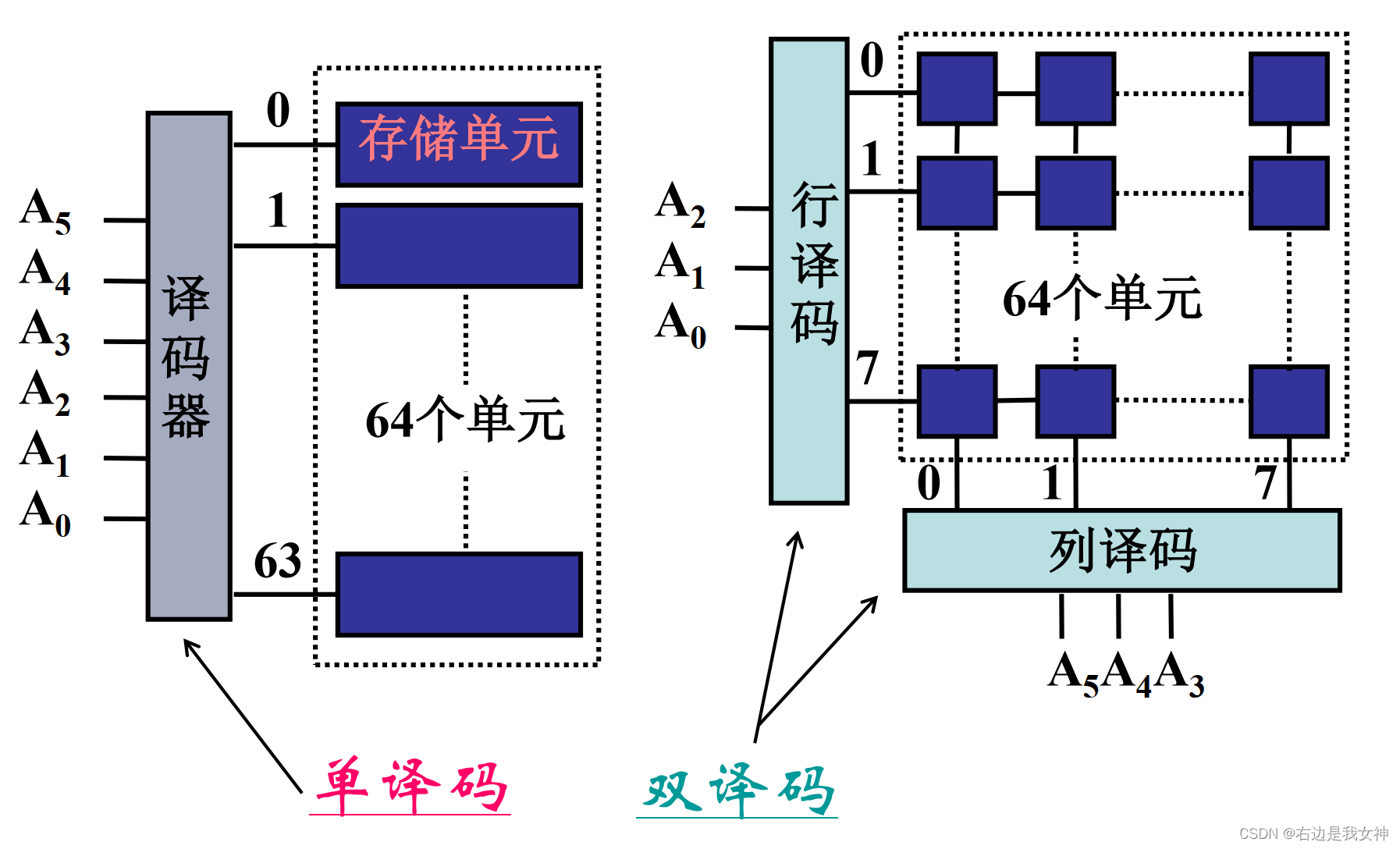

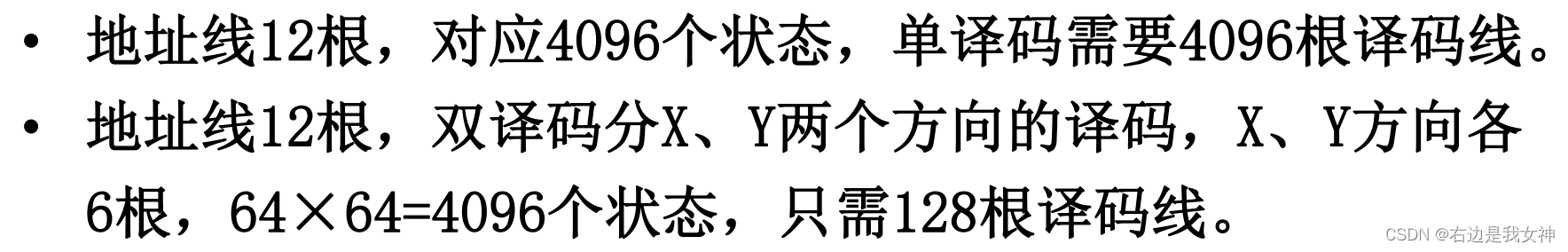

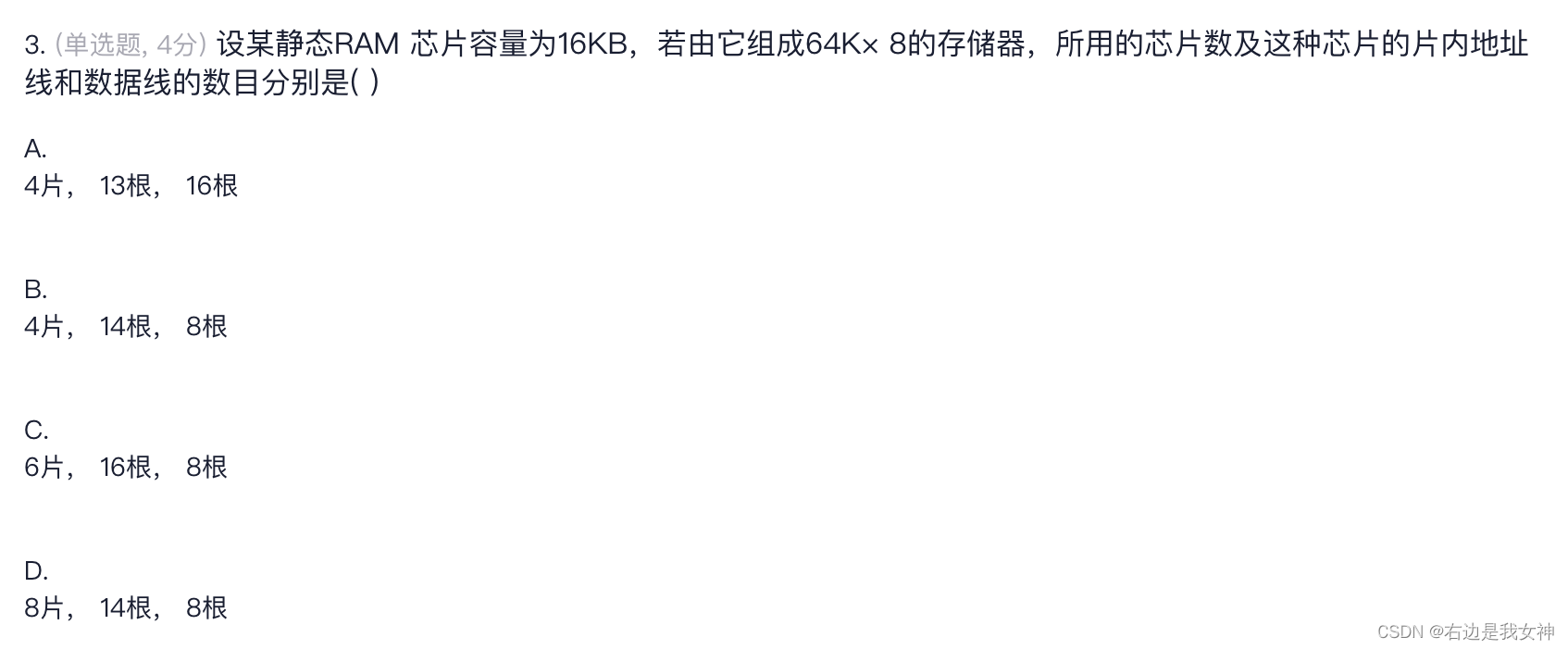

区分好地址线和译码输出线。

选B。

位扩展,在位数方向上进行操作。

字扩展,在存储单元上进行操作。

字位扩展。

选D。

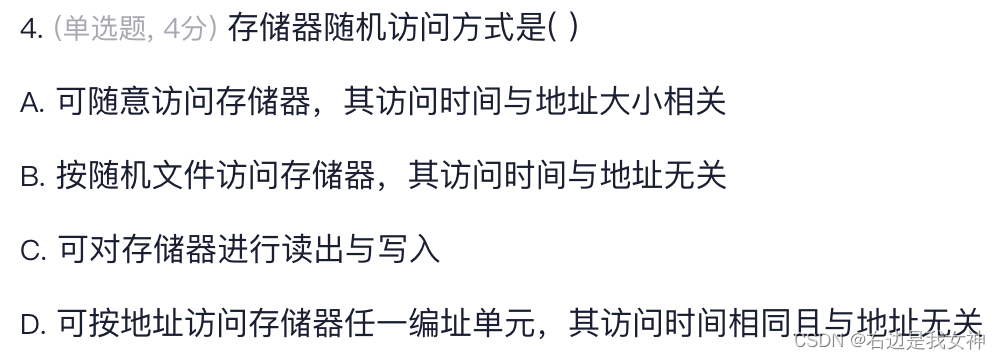

选C。

选C。

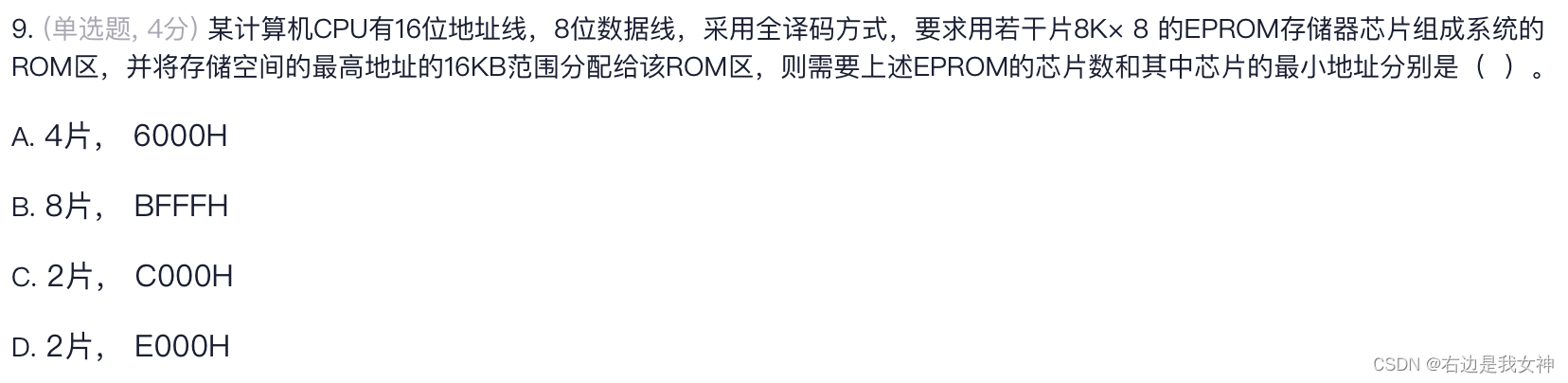

16位地址线说明其能表明64K个单元,且8位地址线表明其字长为8 即64Kx8.

另外 0000H到1FFFH有8192 2^13。

选A。

命中率 = Cache完成存取的总次数/(主存完成存取的总次数+Cache完成存取的总次数

选D。

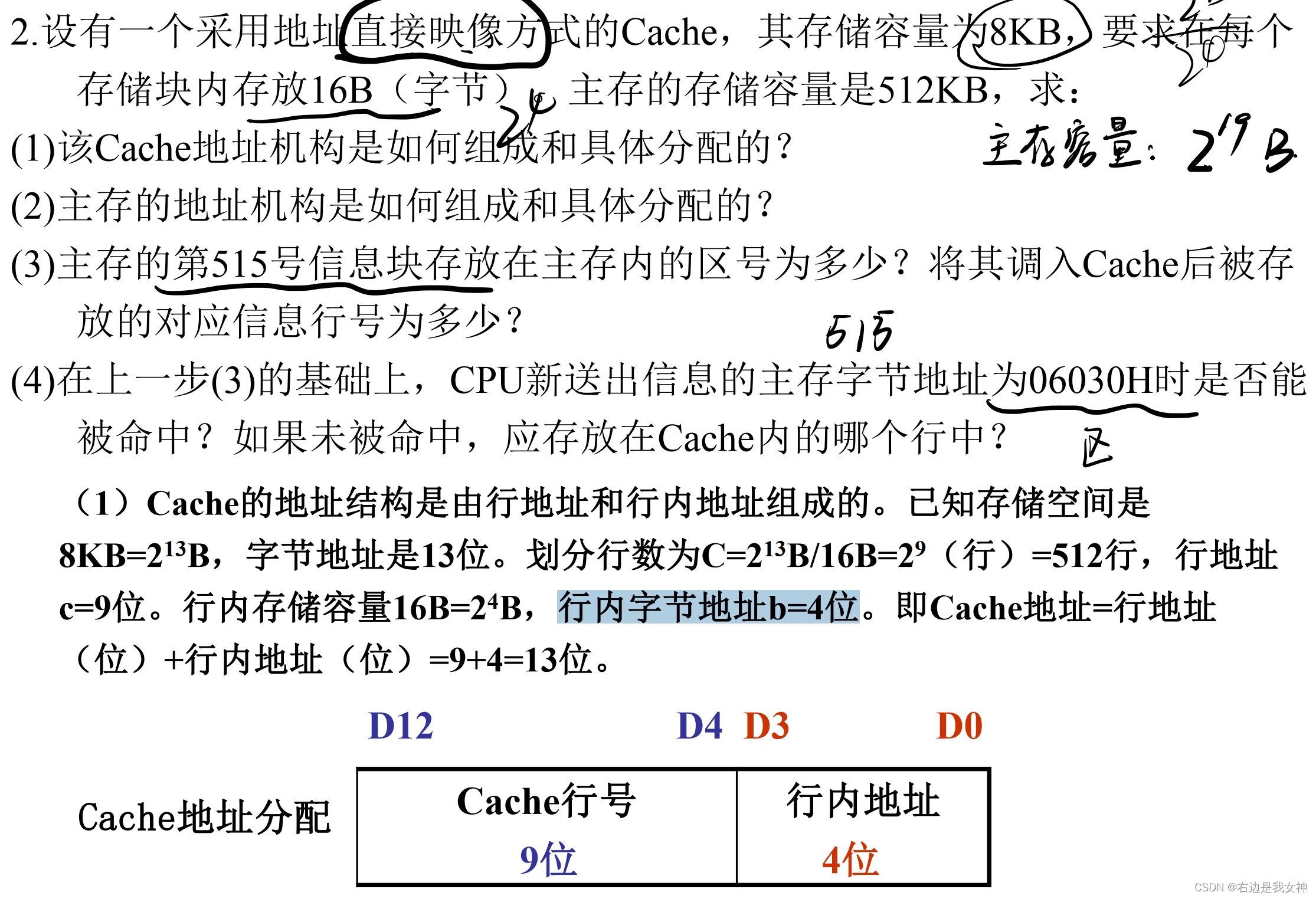

Cache的地址映像方式有:

- 直接映像:块号 mod Cache行数 分区 一对多

- 全相联映像:多对一

- 组相联映像:块号 mod Cache组数 多对多

直接映像的方式简单但不灵活且存储空间得不到利用,降低命中率。

全相联映像的方式灵活但开销大;

组相联映像的性能和复杂性介于两者之间。

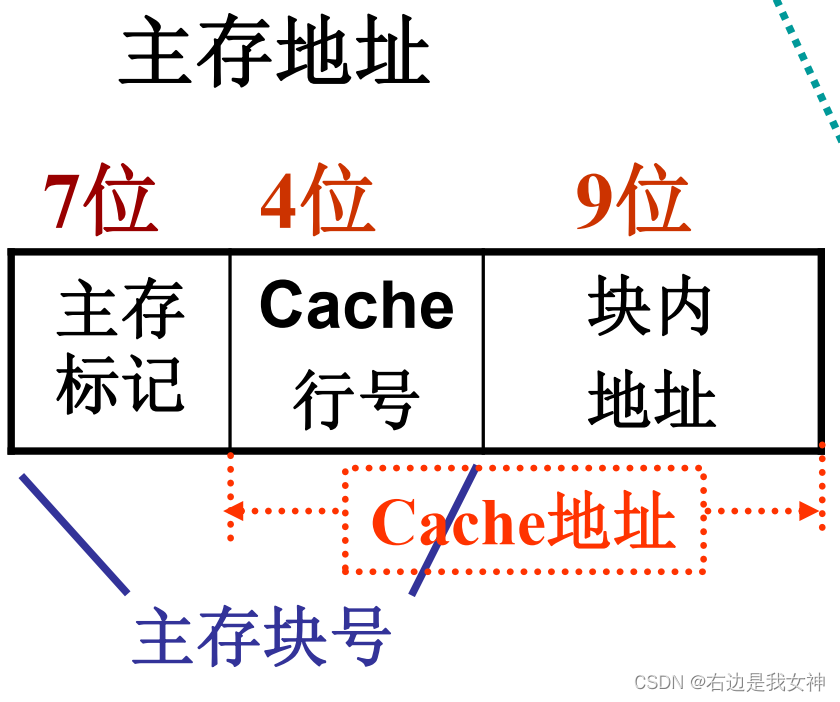

直接映射的主存地址:

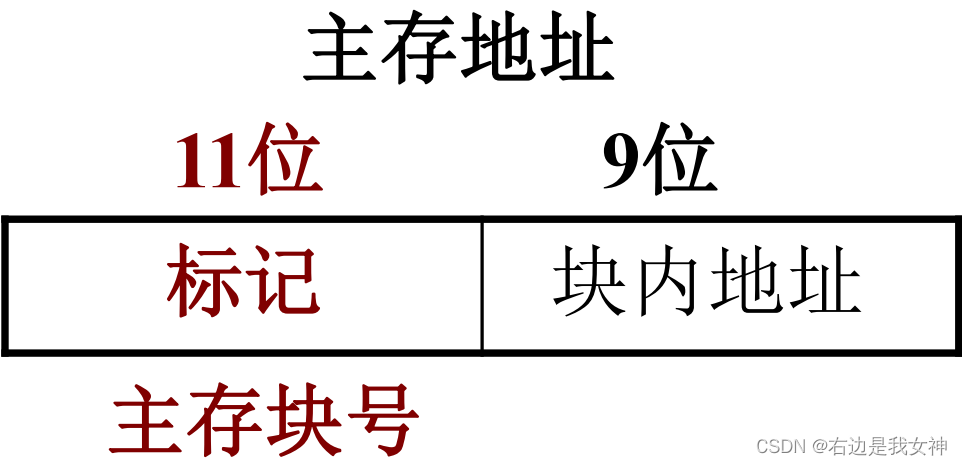

全相联映射的主存地址:

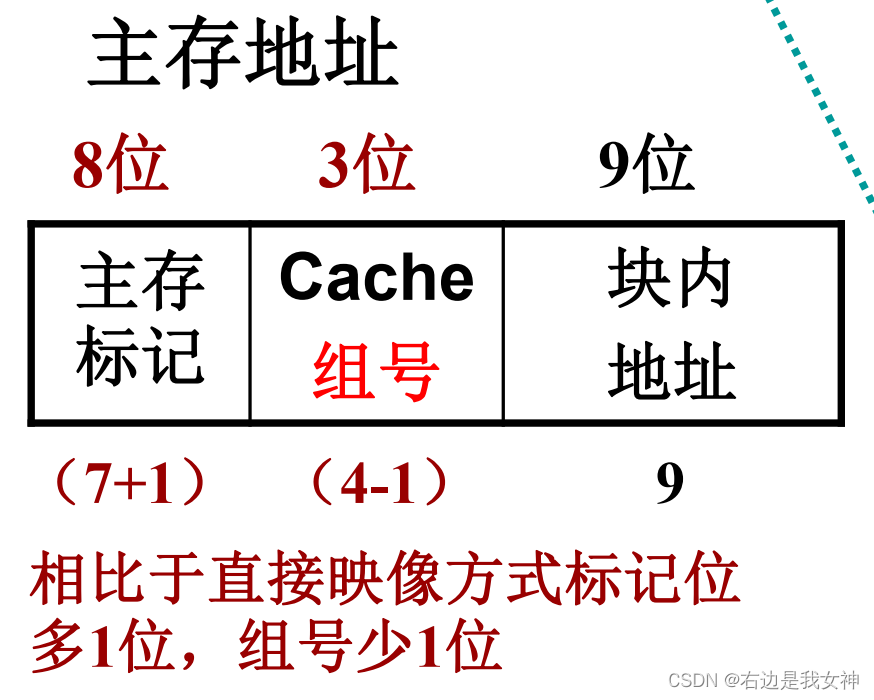

组相联映像的主存地址:

注意:行号和组号都是从0开始。

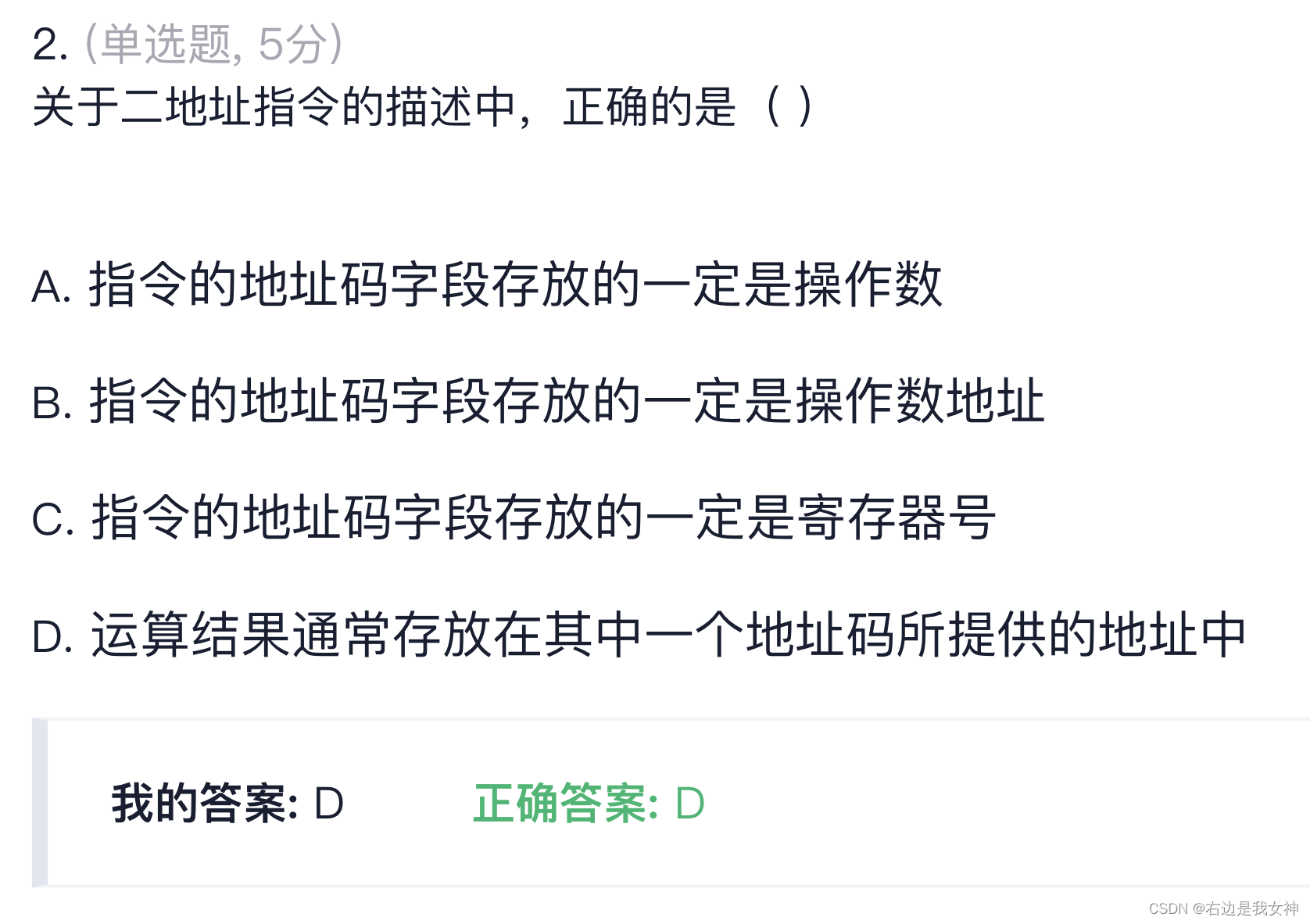

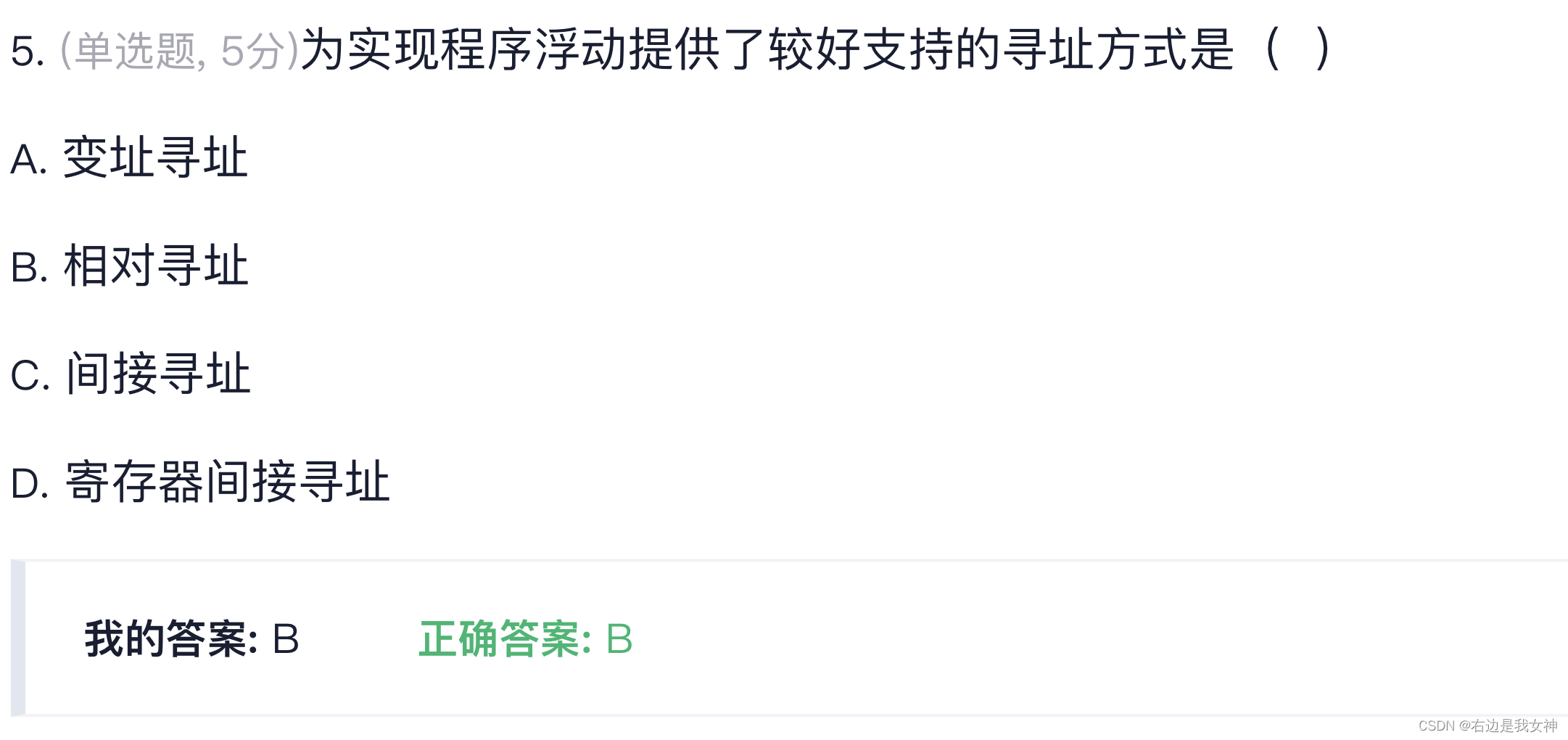

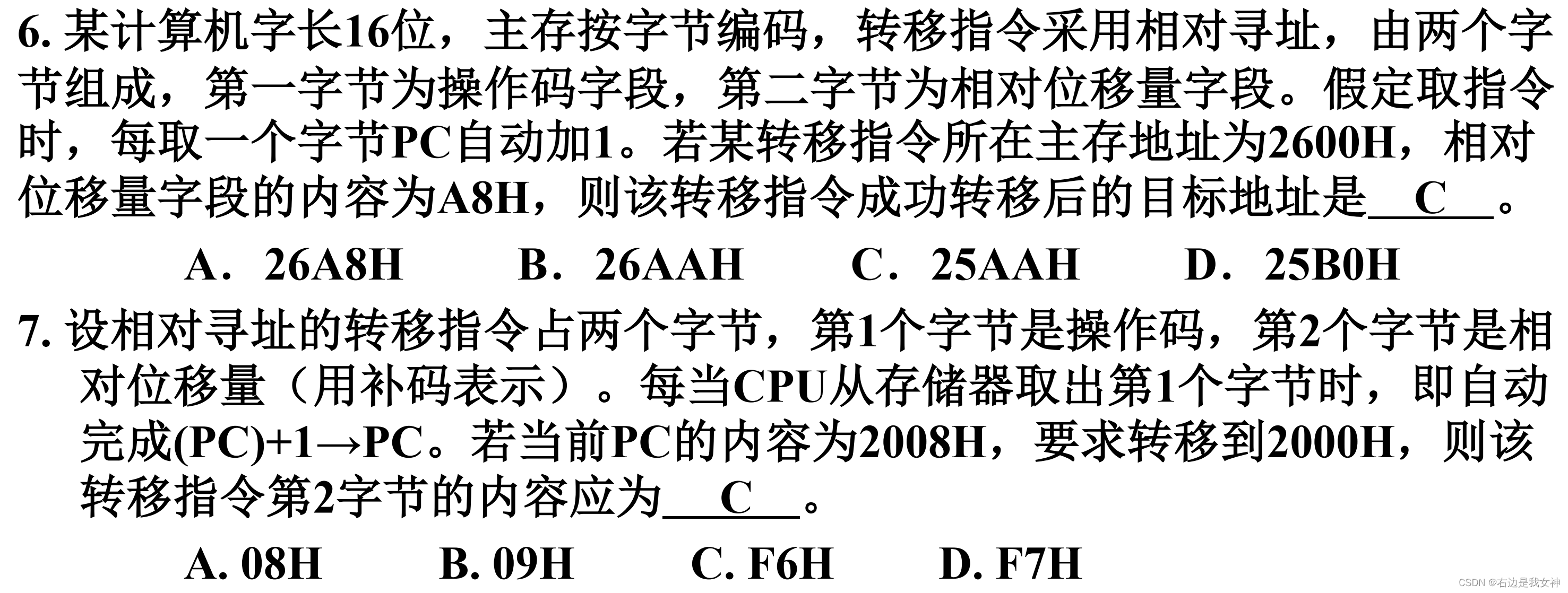

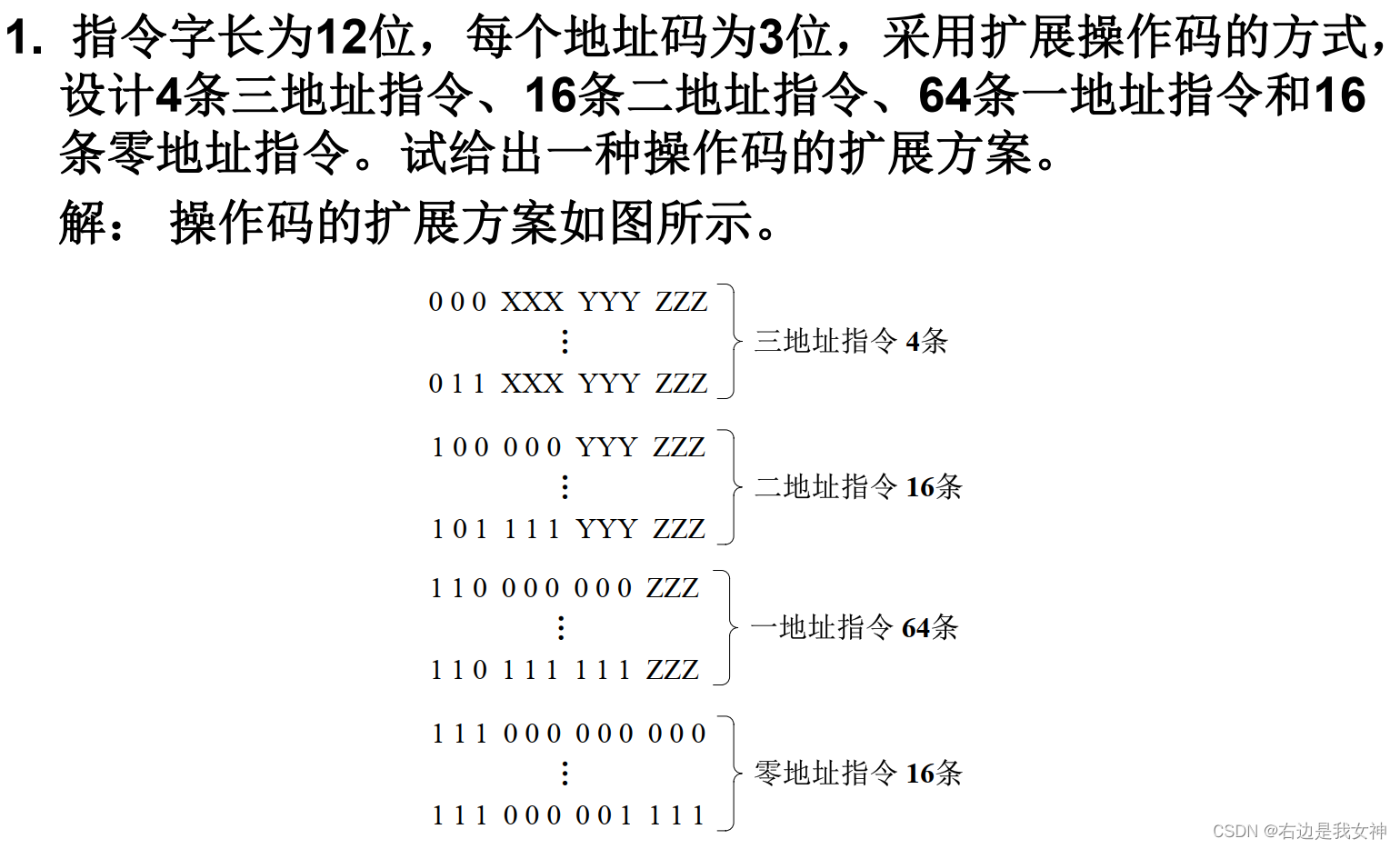

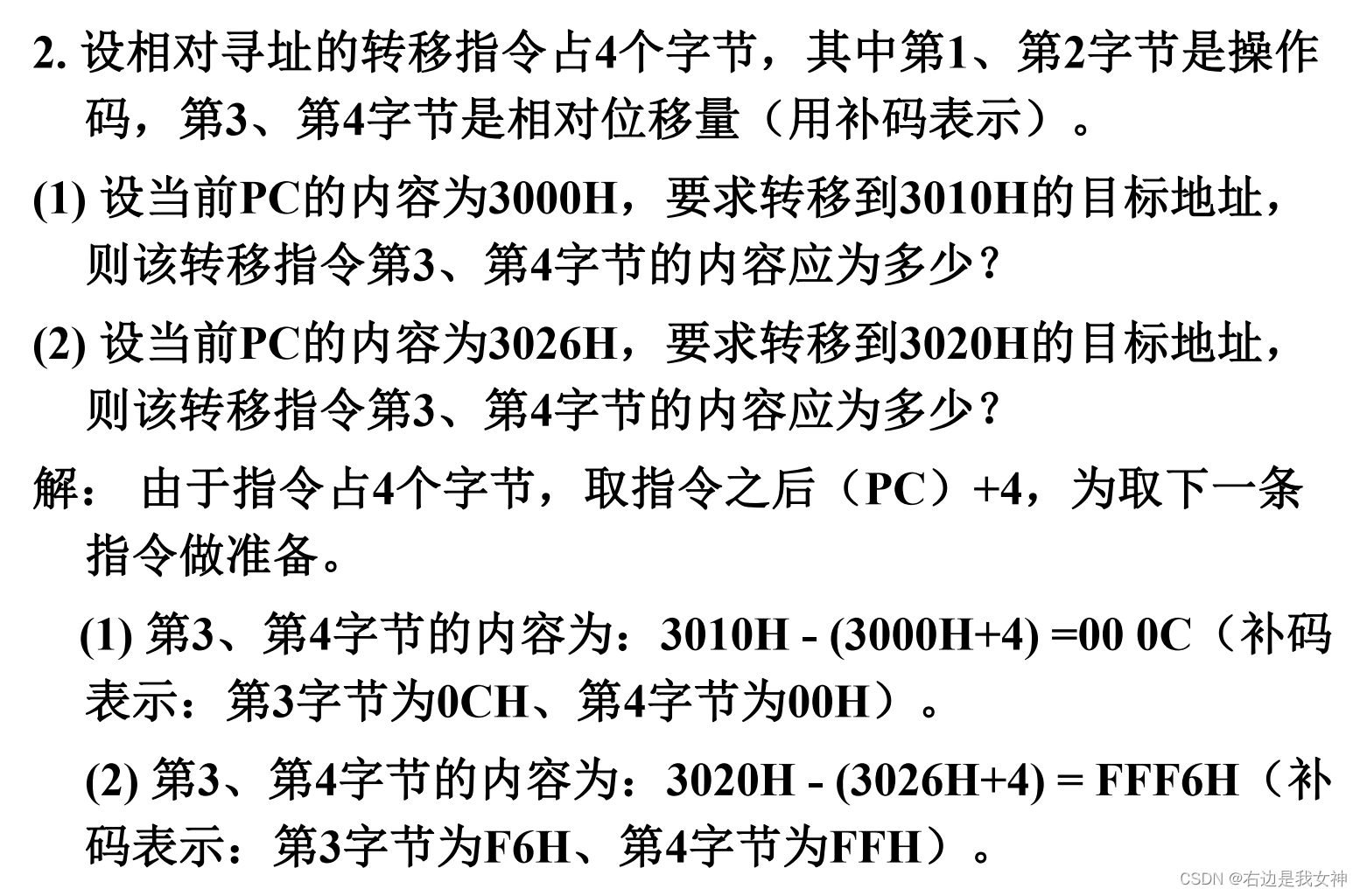

指令系统

相对寻址的计算、设计变长指令

操作数直接放在指令中,指令放在主存中。

FFF6+200A = 2000H

变长指令。

RICS:精简指令系统计算器:

- 优先选取使用频率高的一些简单指令;

- 指令长度固定,指令格式少,寻址方式少;

- 只有取数和存数指令访问内存;

- CPU中寄存器数量多;

- 大部分指令在一个或小于一个机器周期完成;

- 硬布线控制逻辑为主;

一方面是16进制,满16进位,另一方面是低位是小字节。

中央处理器

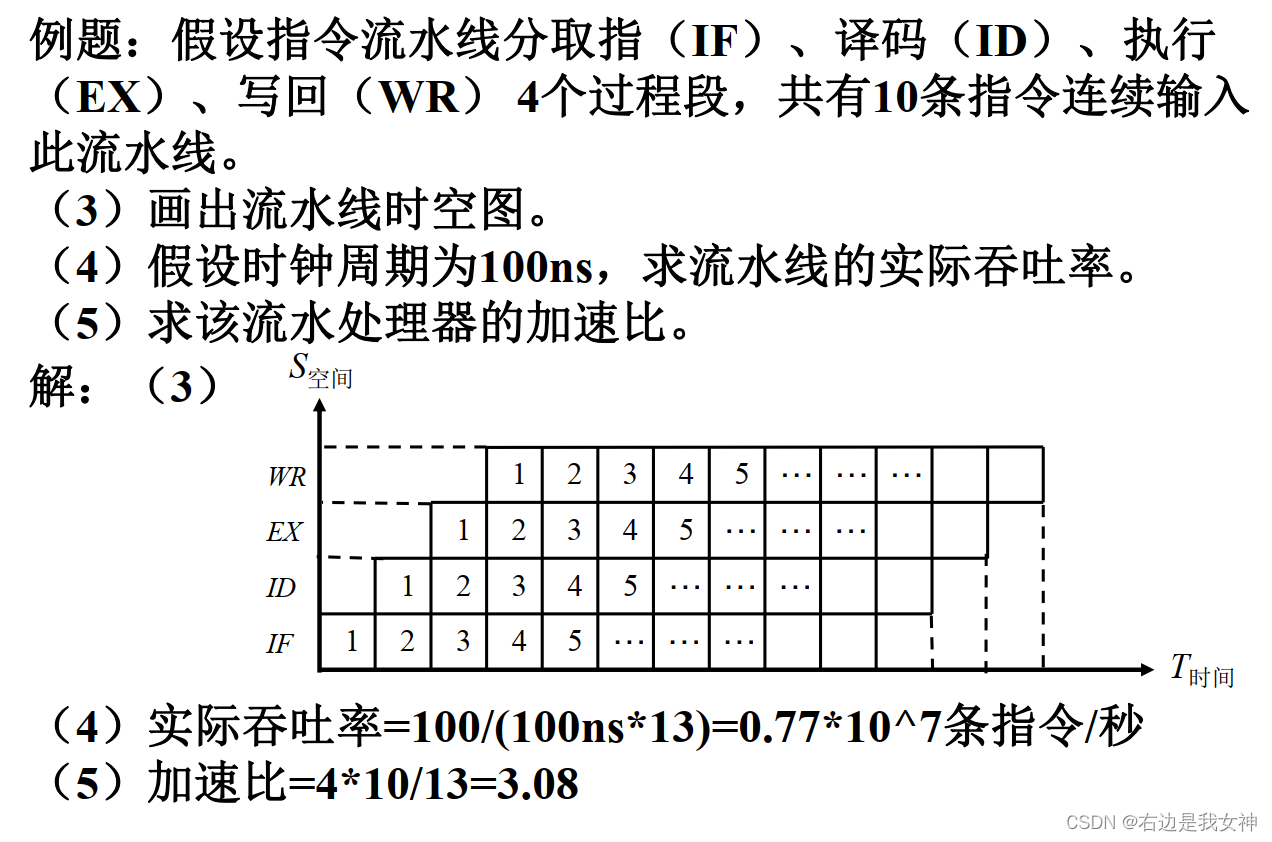

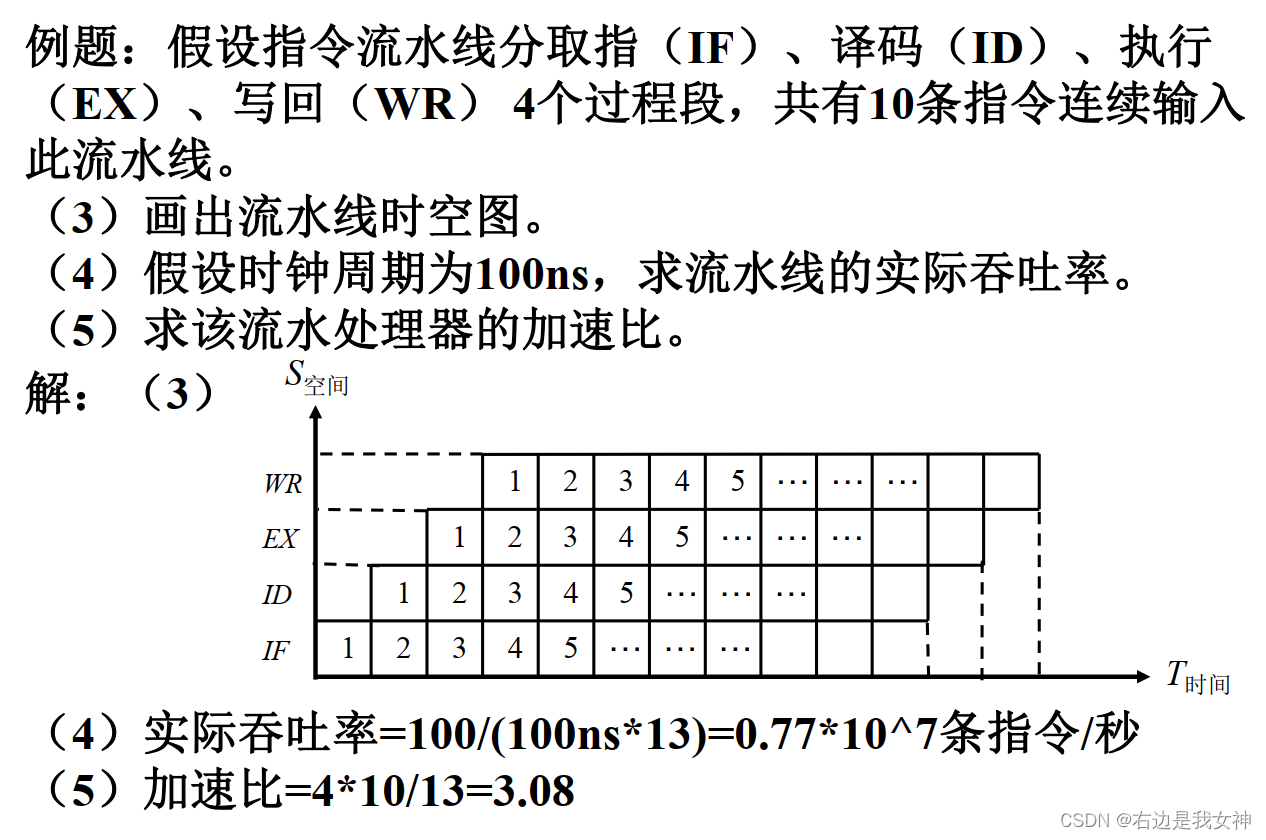

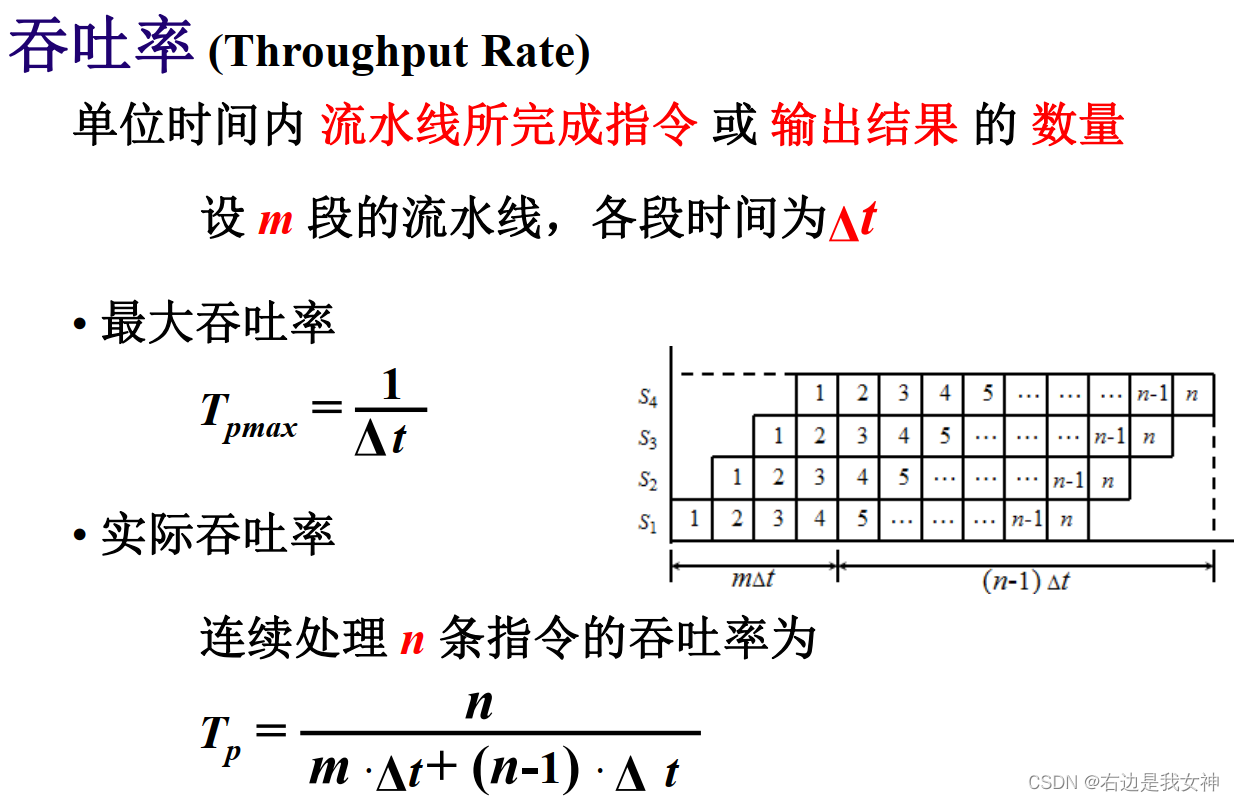

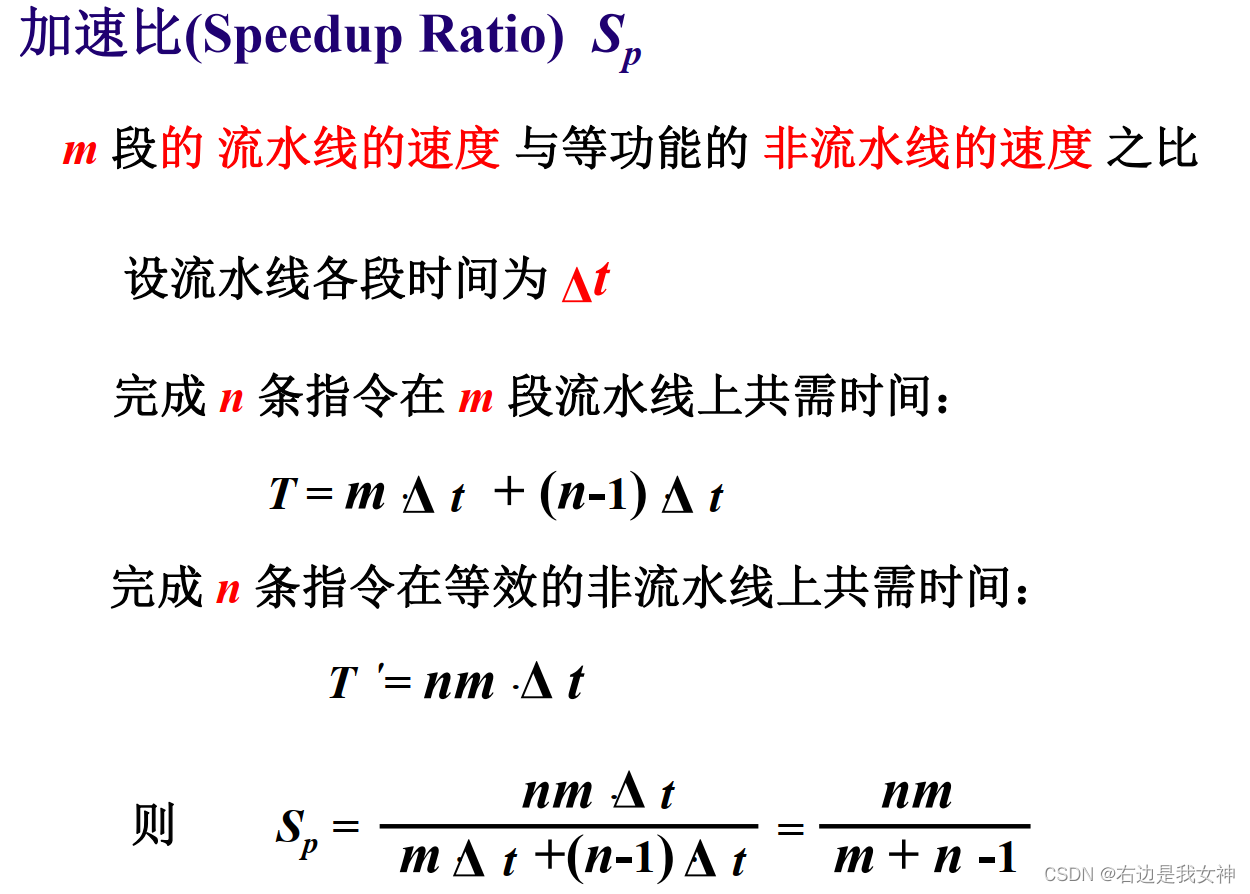

了解CPU内部构造、了解数据的流动、CPI及MIPS的相关计算、微指令的编码方式、指令流水线的相关计算

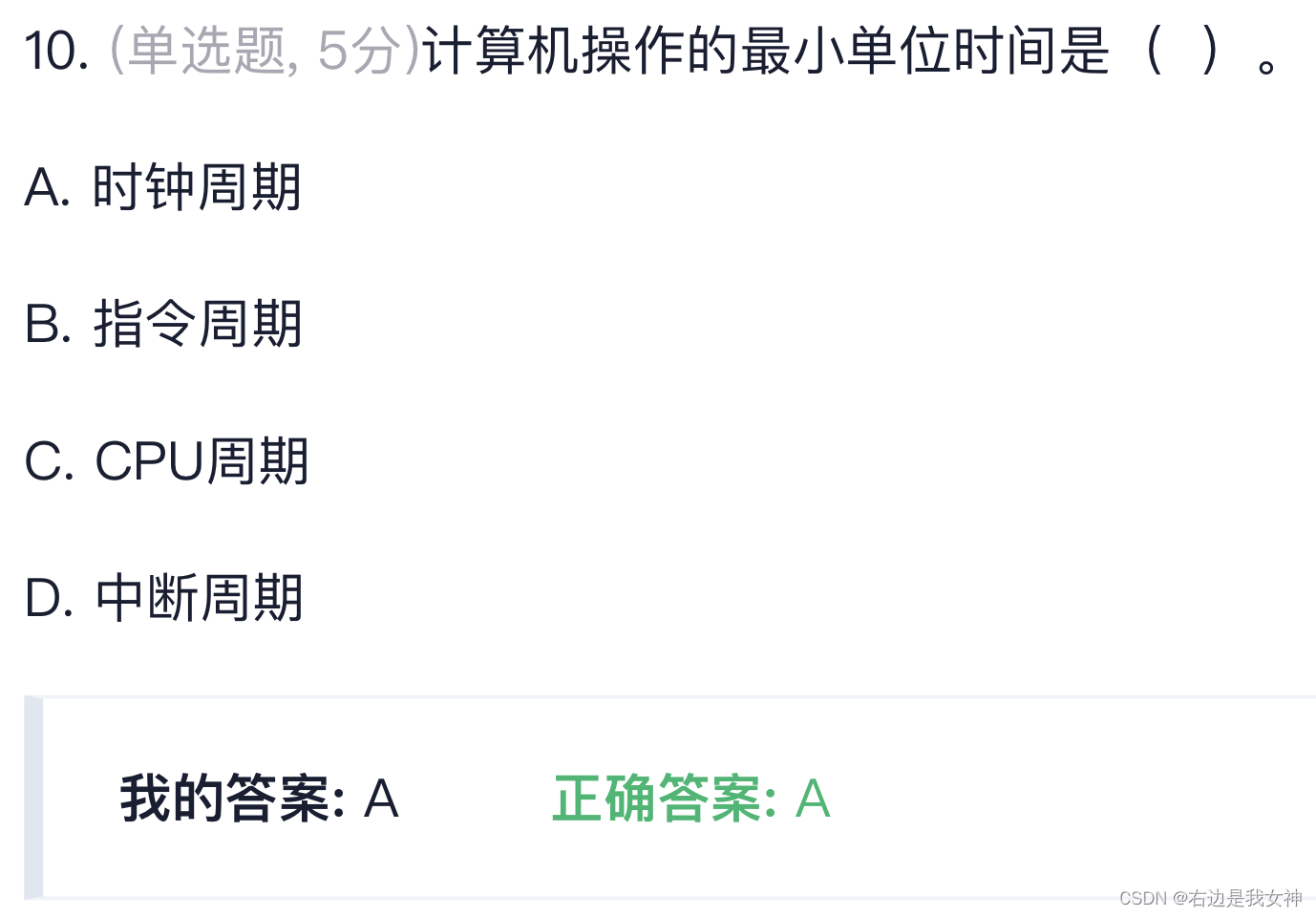

指令周期:取出一条指令并执行这条指令的时间。

CPU周期/机器周期:为了便于管理常把一条指令的执行过程划分成若干个阶段,每一阶段完成一个基本操作,完成一个基本操作所需要的时间称为机器周期。

微指令周期:读出微指令的时间加上执行这条微指令的时间。

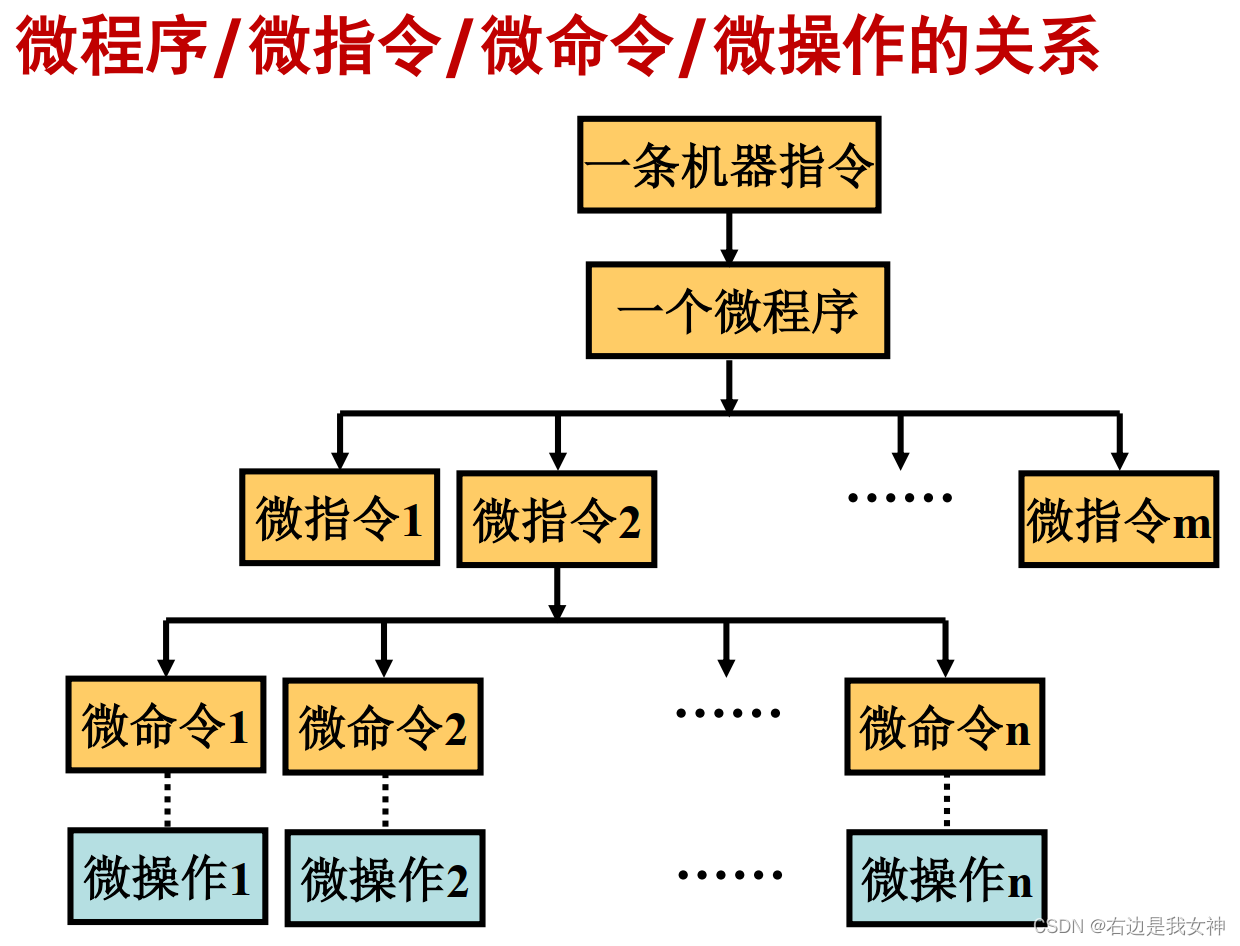

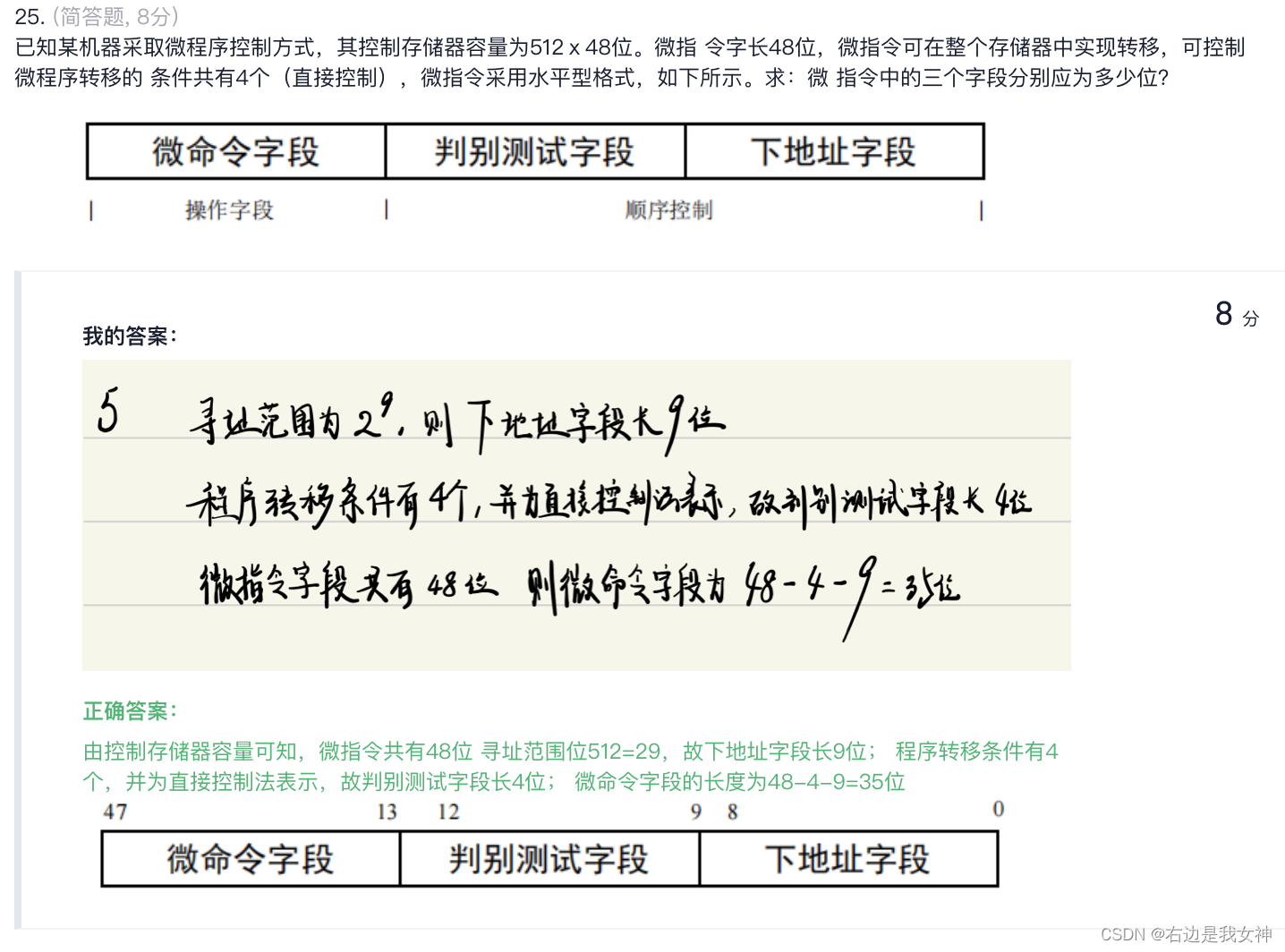

若干微命令编成一条微指令、若干微指令编成一段微程序。

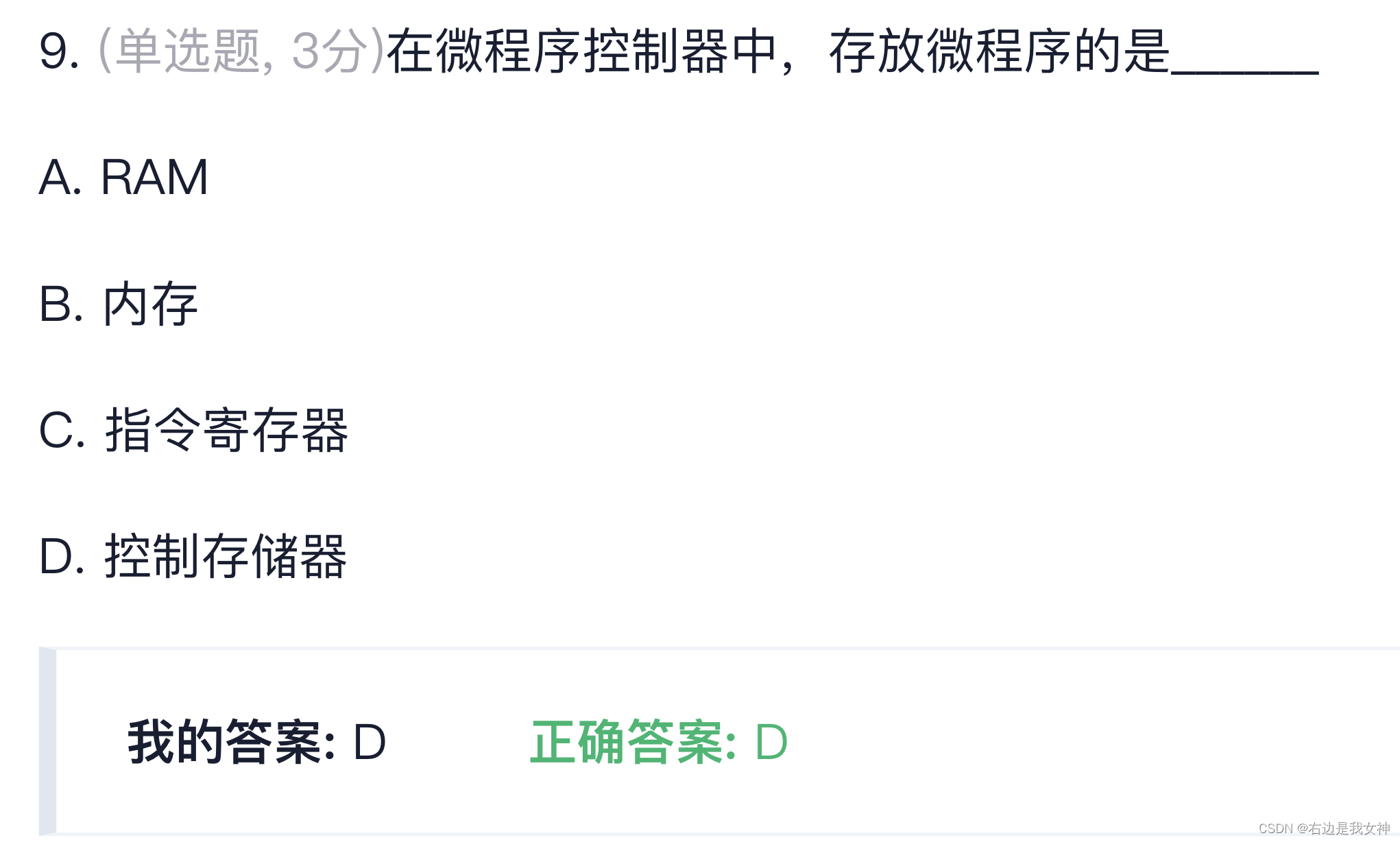

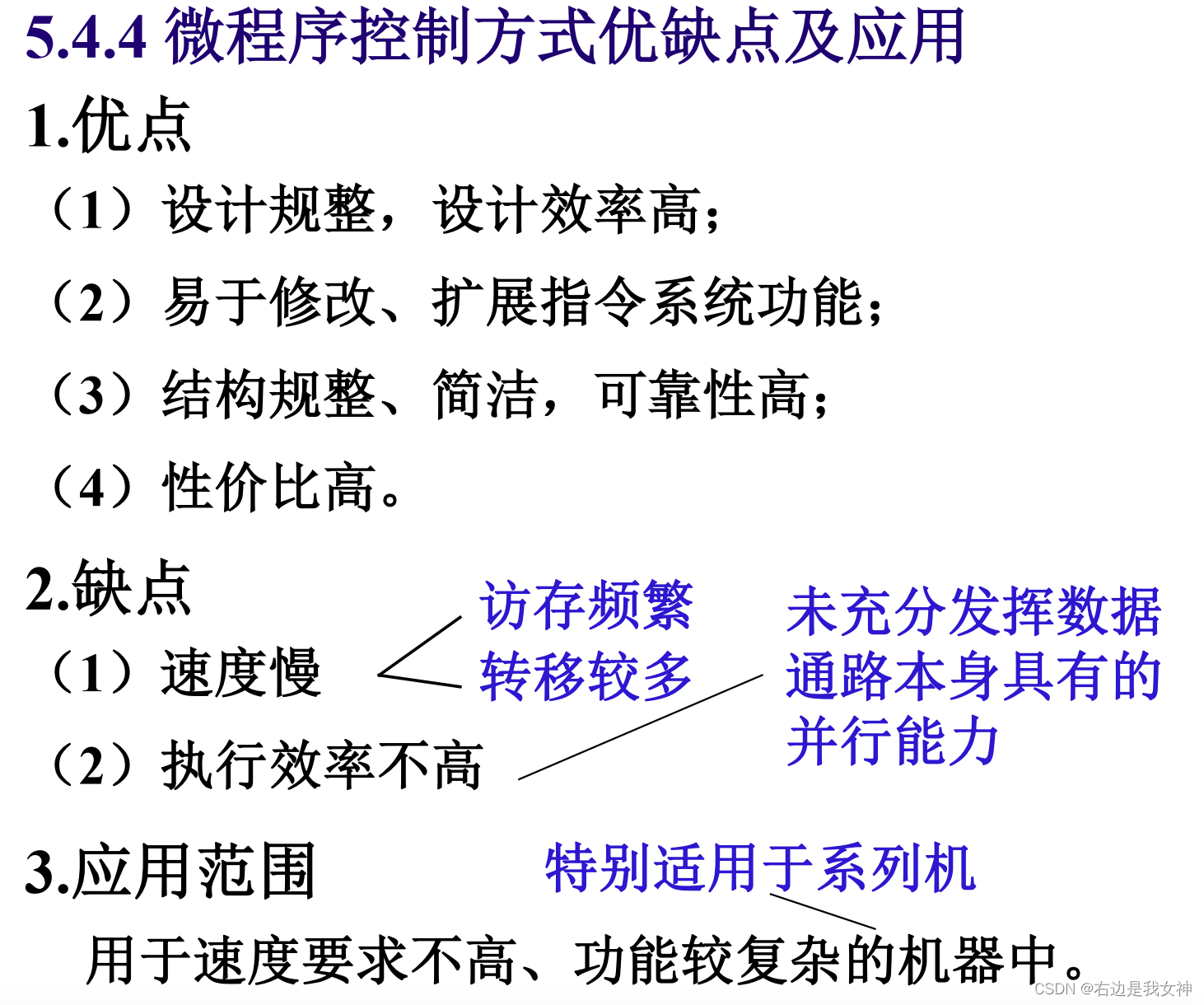

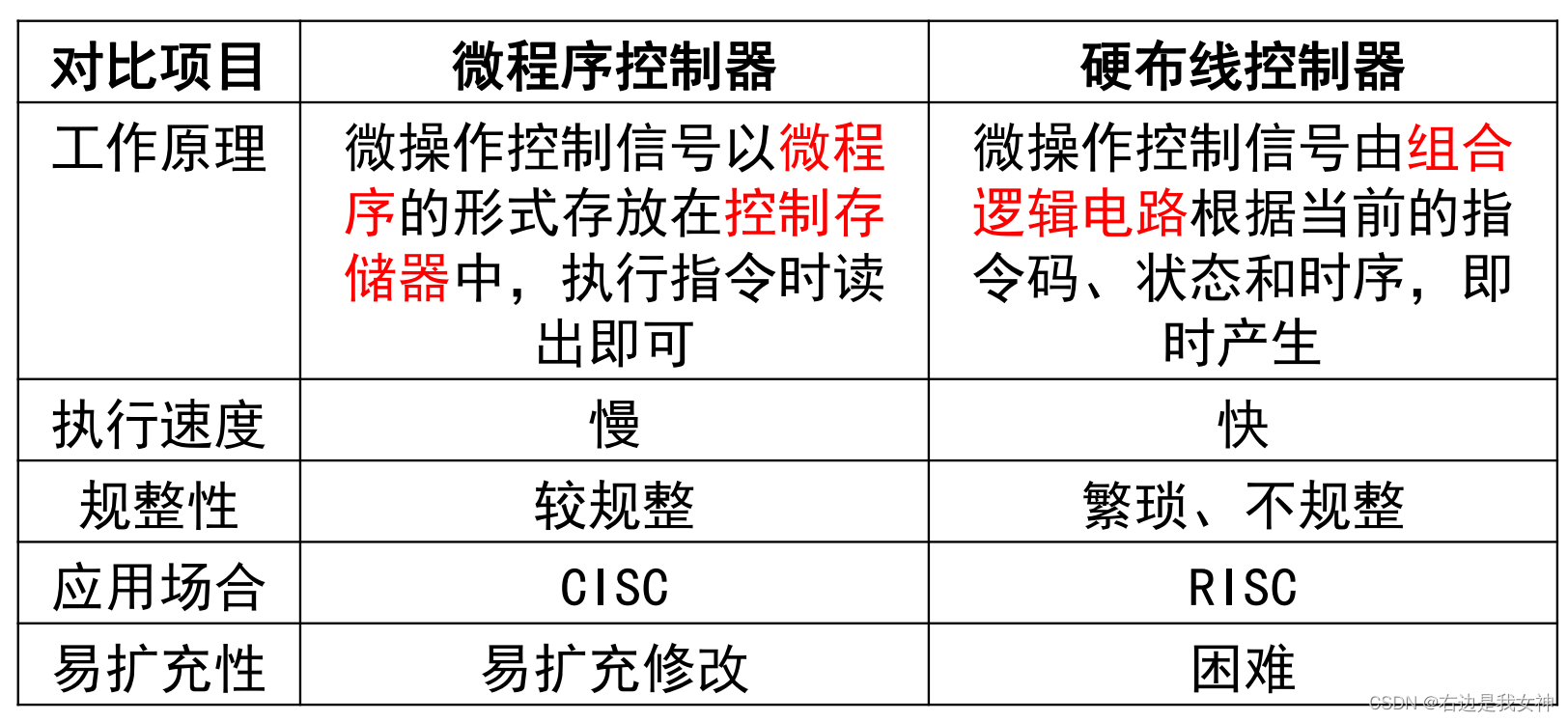

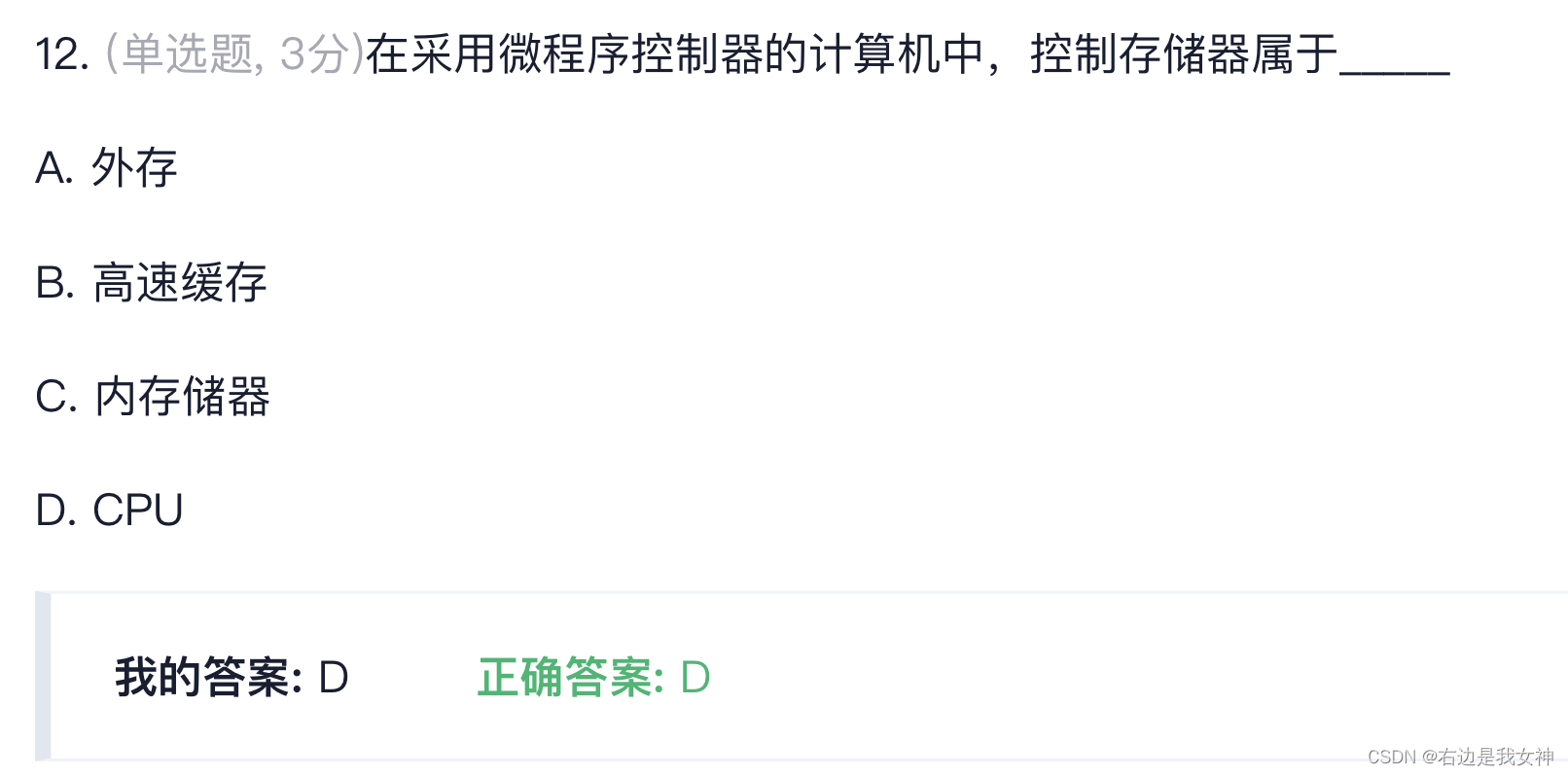

微程序实现存放在控制存储器中,执行机器指令时再取出。

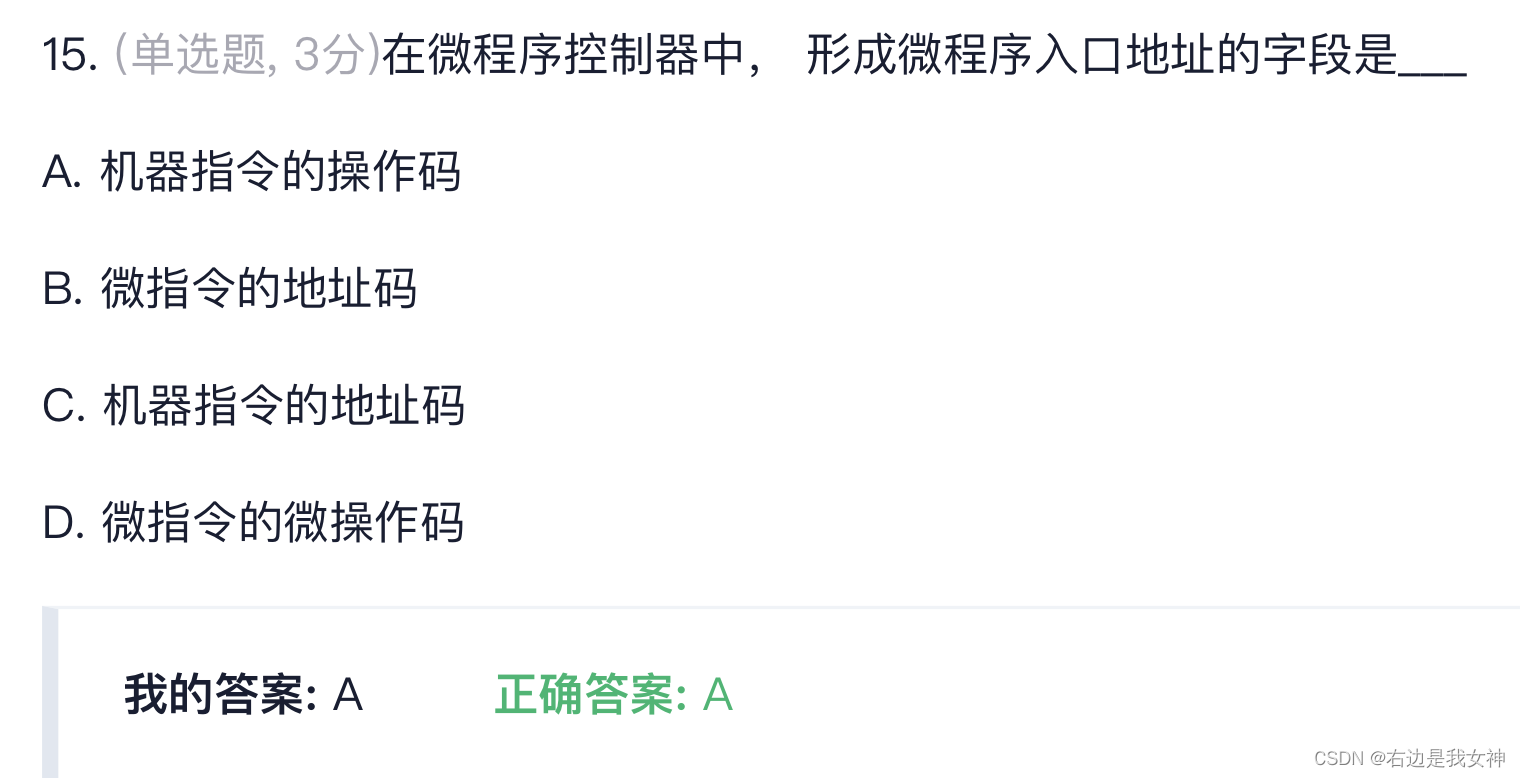

微程序控制器首先根据CM中的取指令程序得到机器指令。然后根据机器指令得到微程序入口地址(微地址形成电路生成的第一类地址),从CM中得到微指令后进行操作。之后更加微地址字段、现行微地址和运行状态由微地址形成电路给出后续微地址以此循环。

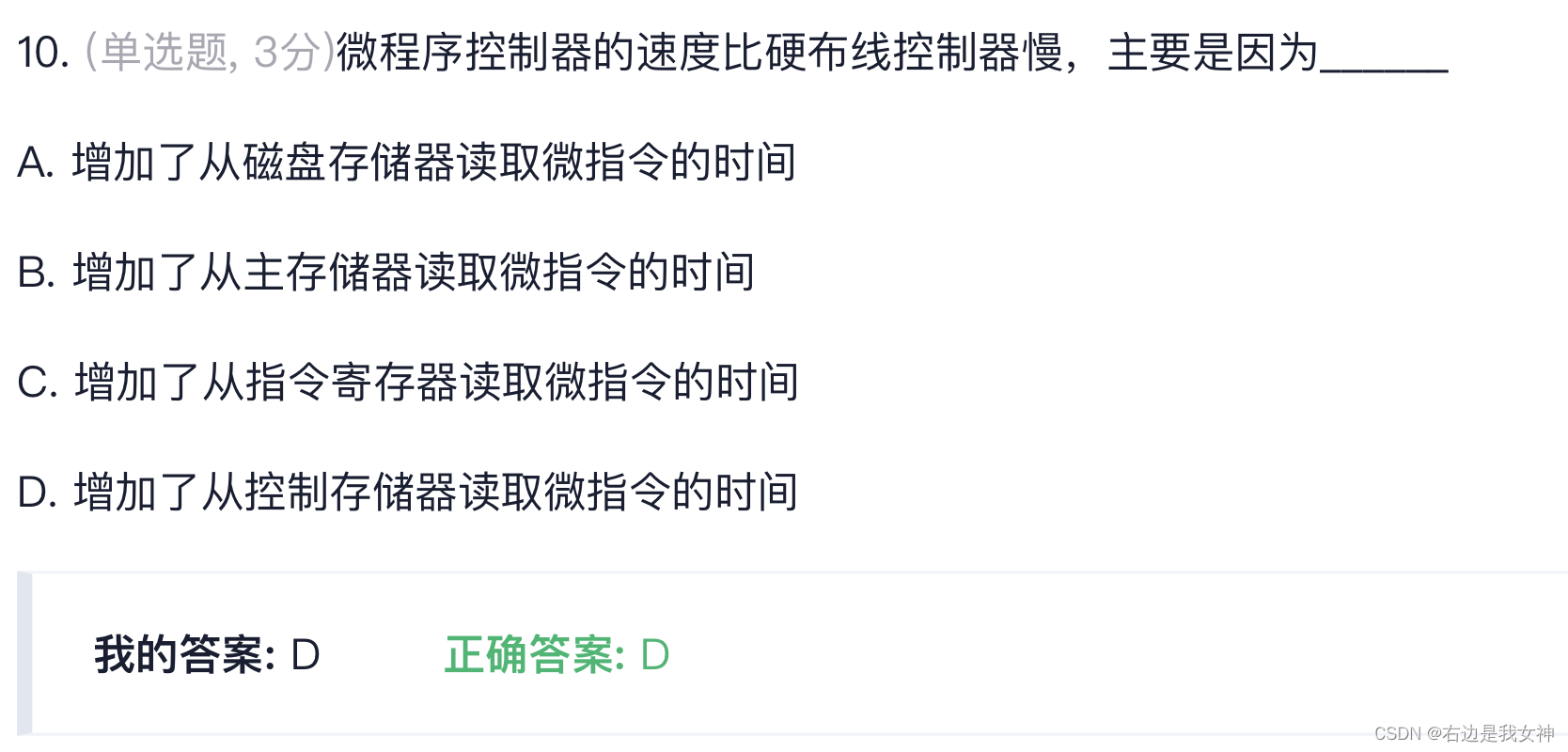

相比硬布线控制器,每次执行指令前都要从CM询问该执行那一条。

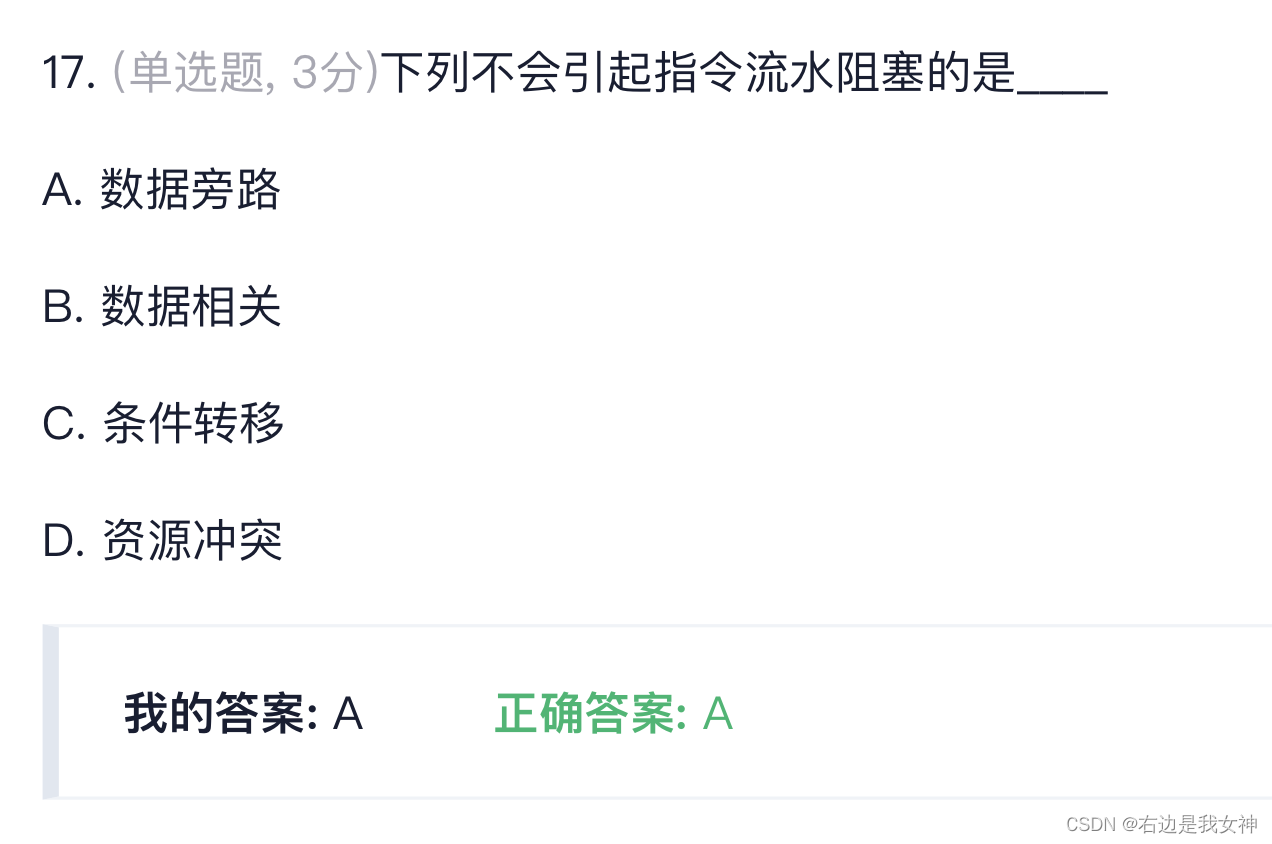

指令流水出现停顿与三种情况有关系:

- 结构相关:多条指令在同一时刻争用同一资源;

- 数据相关:后续指令要用到前面指令的操作结果;

- 控制相关:遇到条件转移指令时,存在顺序执行还是转移执行两种可能。

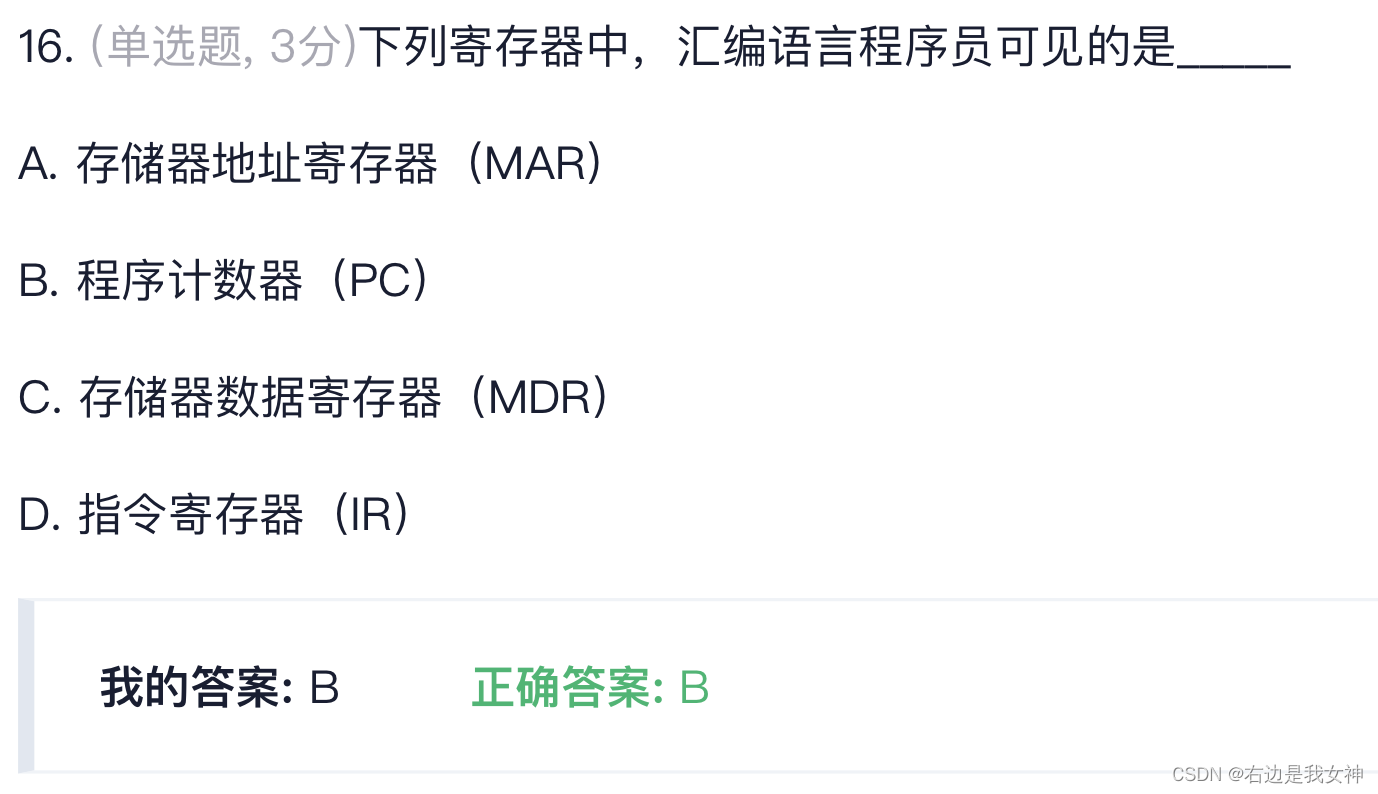

CPU中的主要部件有:

- CU 控制单元;

- PC 程序计数器:存放下一条指令地址;

- IR 指令寄存器:存放当前指令的内容,与CU相连;

- ID 指令译码器:对IR中的操作码进行分析解释;

- MAR:主存地址寄存器,与AB相连;

- MDR:主存数据寄存器,与DB相连。

取指周期的数据流:

PC->MAR->AB->M->DB->MDR->IR PC+1->PC

间址周期的数据流(从得到形式地址开始)

Ad(MDR)->MAR->AB->M->DB(EA)->MDR

存数指令:

Ad(IR) -> MAR 1->W ACC->MDR MDR->M(MAR) 地址给出 存指令给出 数据给MDR 数据放到主存相应地址位置。

取数指令:

Ad(IR) -> MAR 1->R M(MAR)->MDR MDR->ACC 地址给出 写指令给出 数据给MDR MDR在给寄存器。

每一步都是一个部件到另一个部件。A(B)表示在A的B位置取出数据。

水平格式包含三个部分:微命令字段、判别测试字段和下地址字段。

直接控制法:每一位表示有无这个命令,直接用01表示;

字段编码表示法:互斥的命令为一组,对应的编码表示序号。

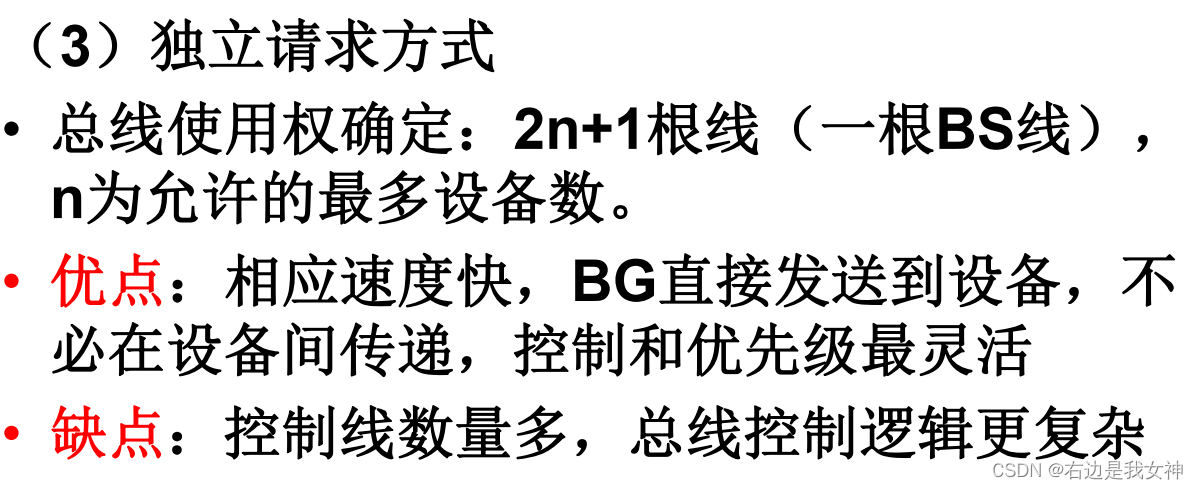

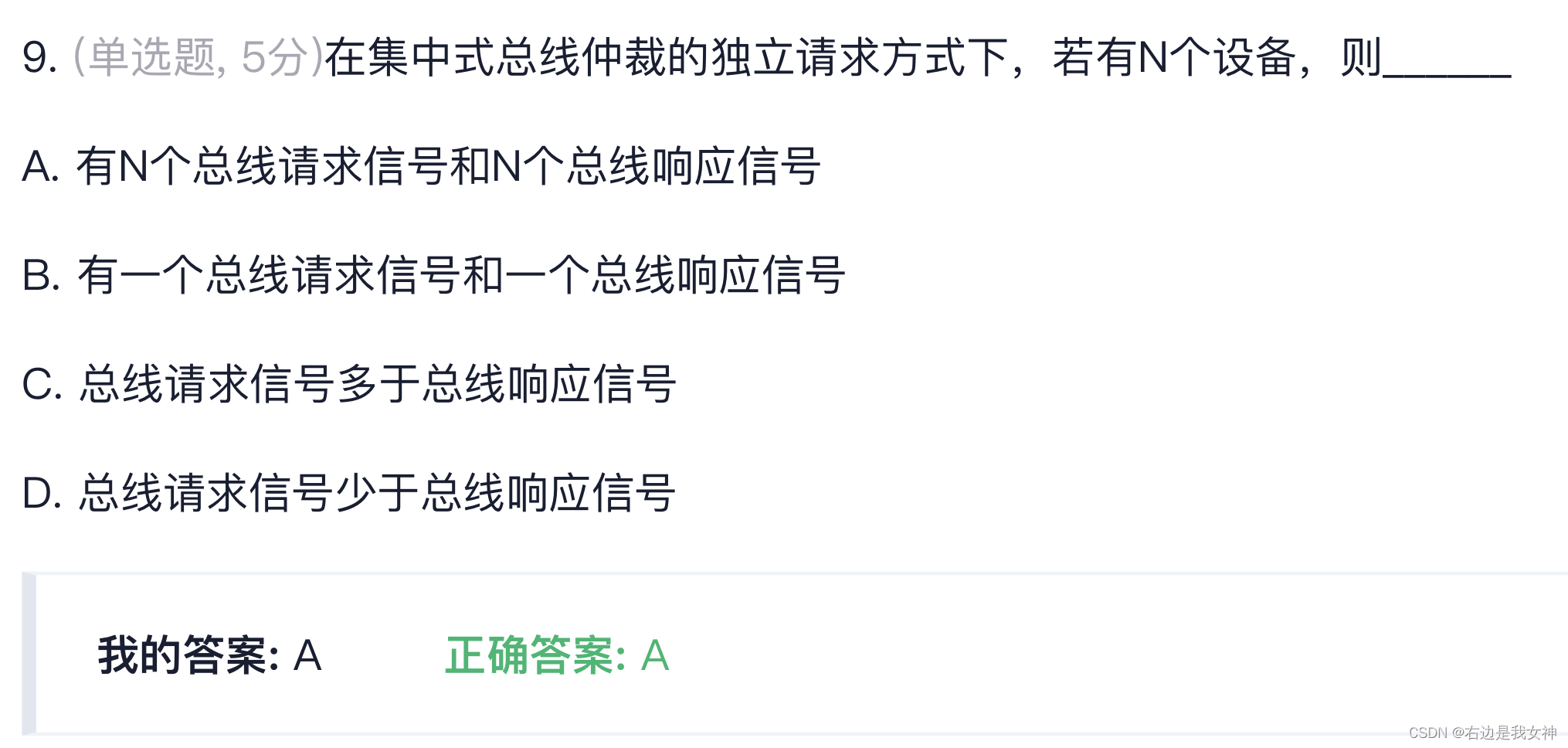

总线

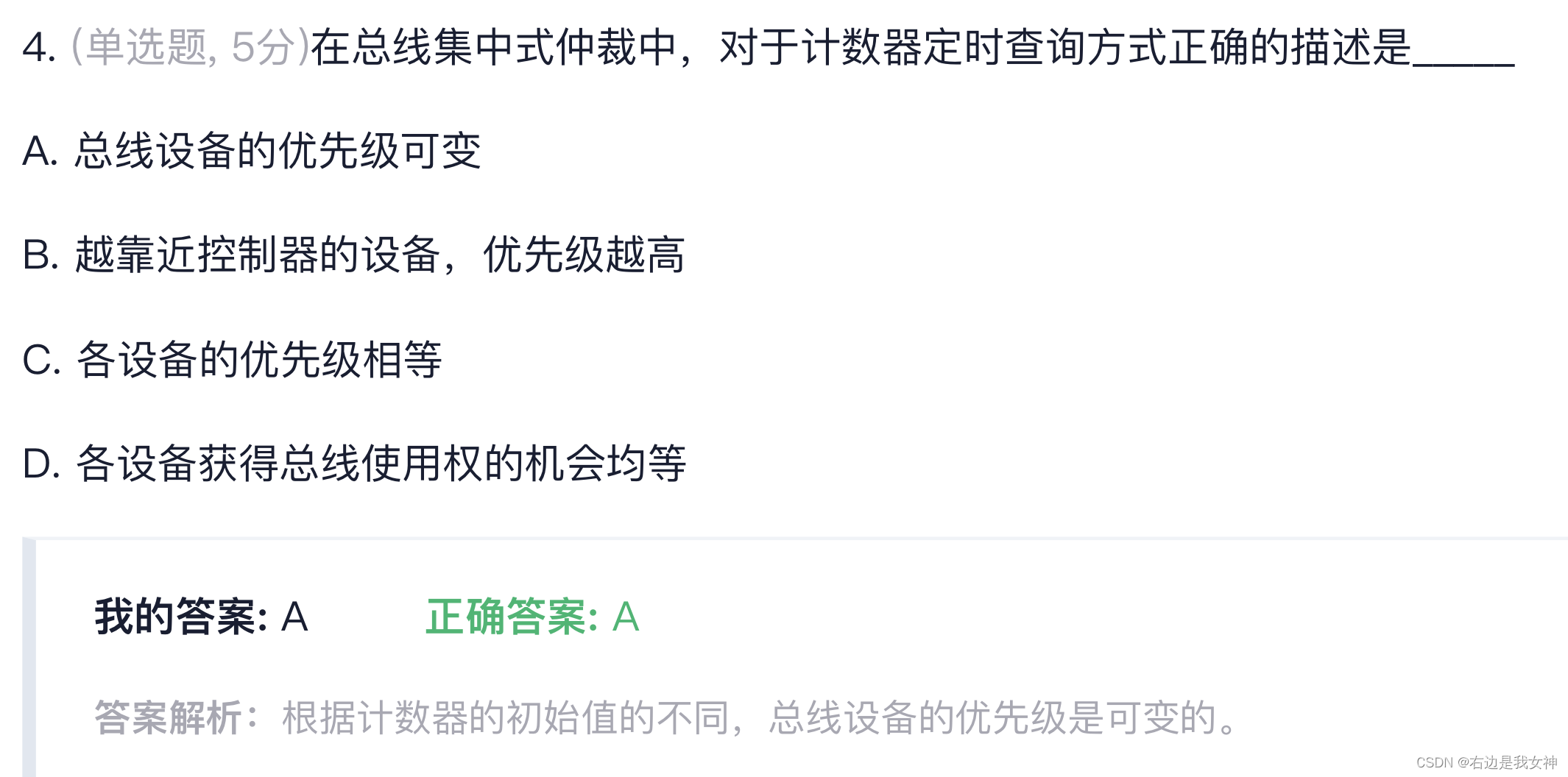

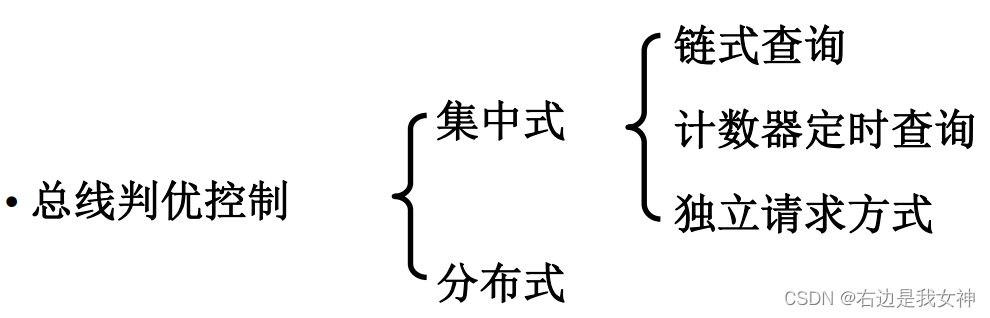

计算总线带宽、总线仲裁的三种方式

数据总线:双向传输总线,其位数称为数据总线宽度,即为机器位数;

地址总线:标识主存或I/O设备上存储单元的位置,单向总线,如果地址总线有n条,则可以寻址到

2

n

2^n

2n个存储单元;

总线带宽=总线的频率*传输字节(看单位) 一个周期传两字节 一个周期传一次

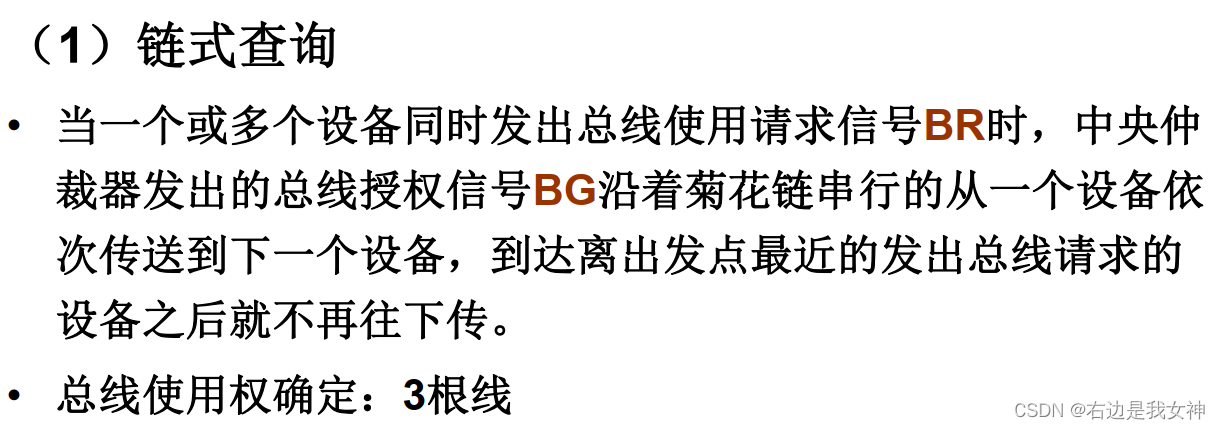

链式查询的缺点是:对硬件电路故障敏感,优先级无法改变;

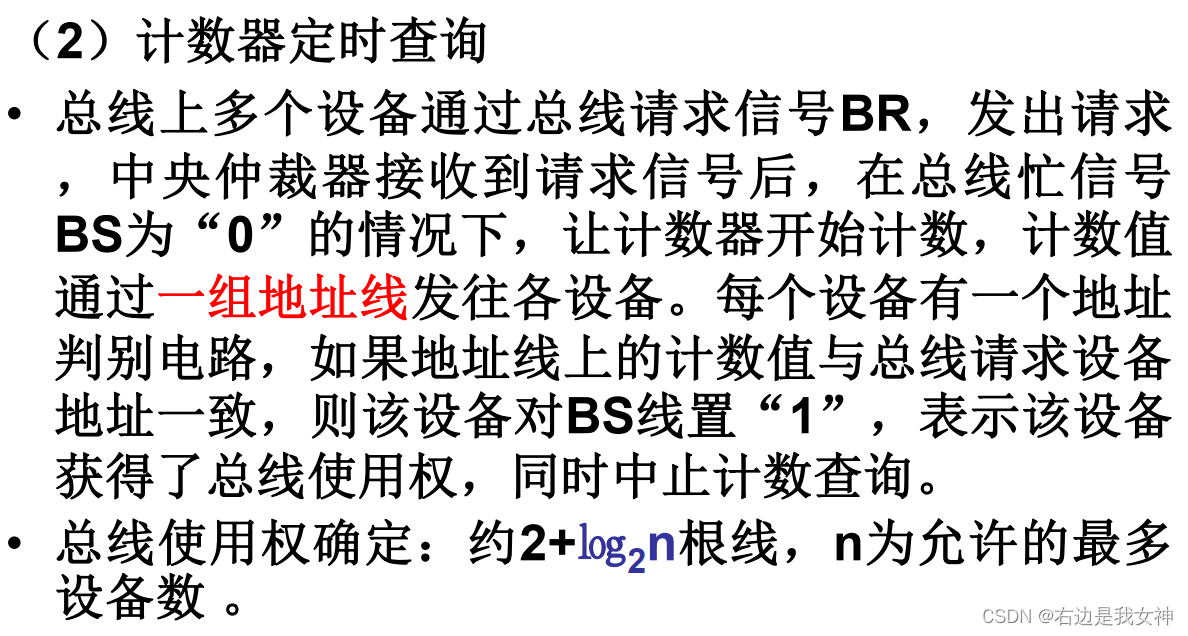

计时器定时查询的缺点是:增加了控制线的条数,控制相比链式查询复杂;

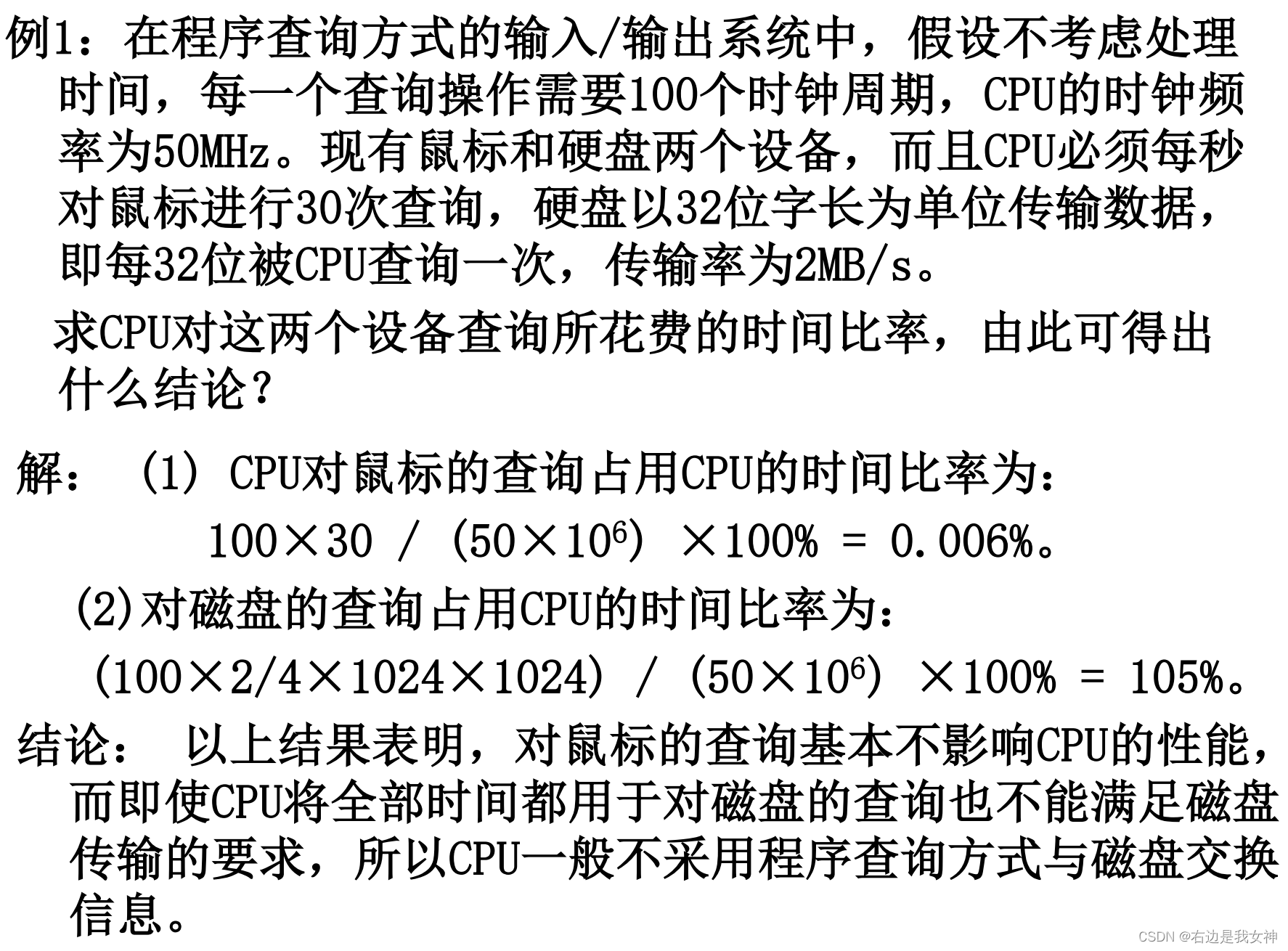

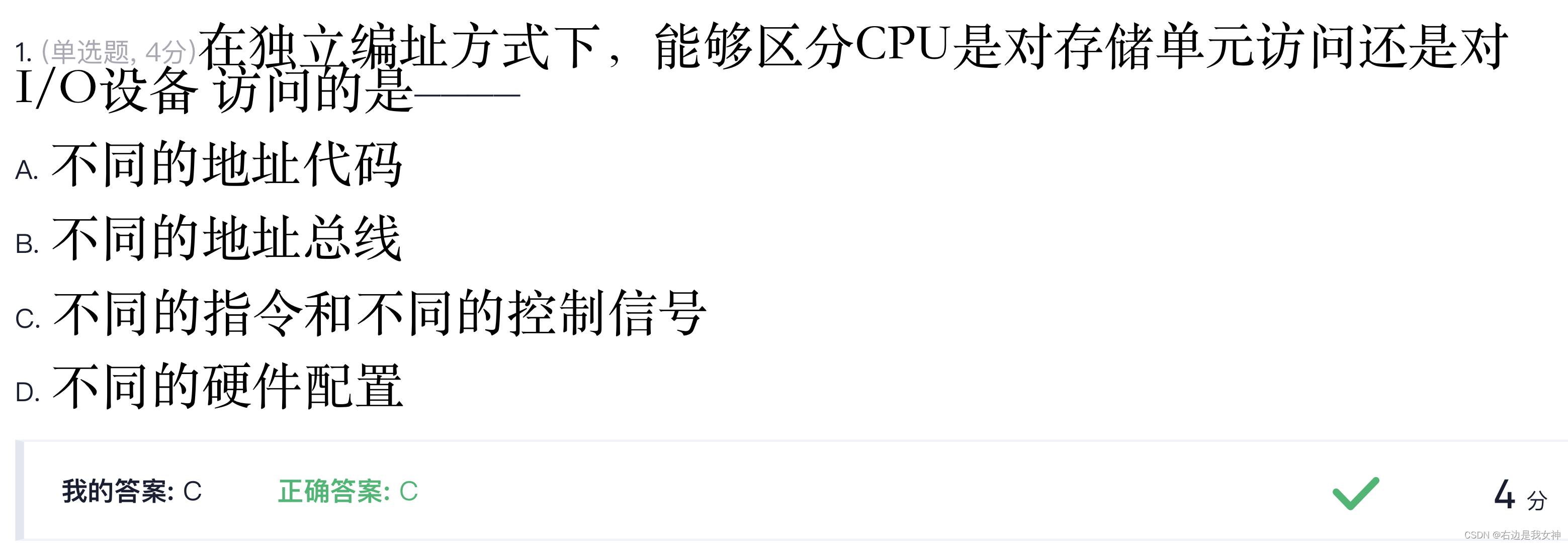

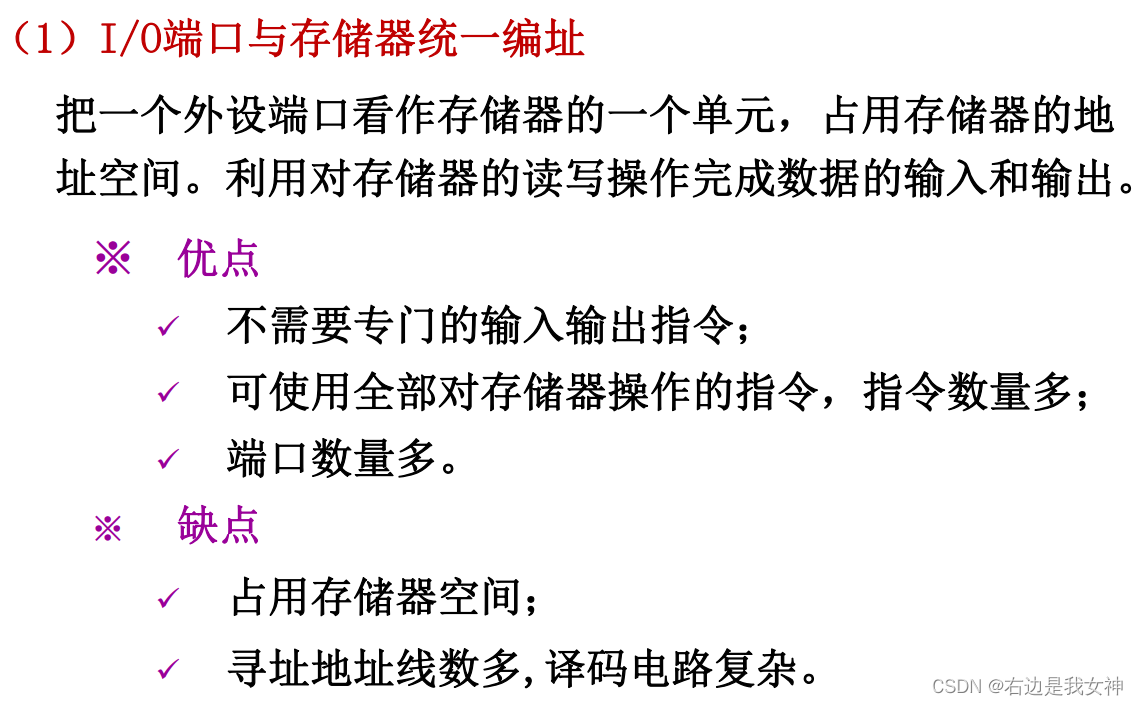

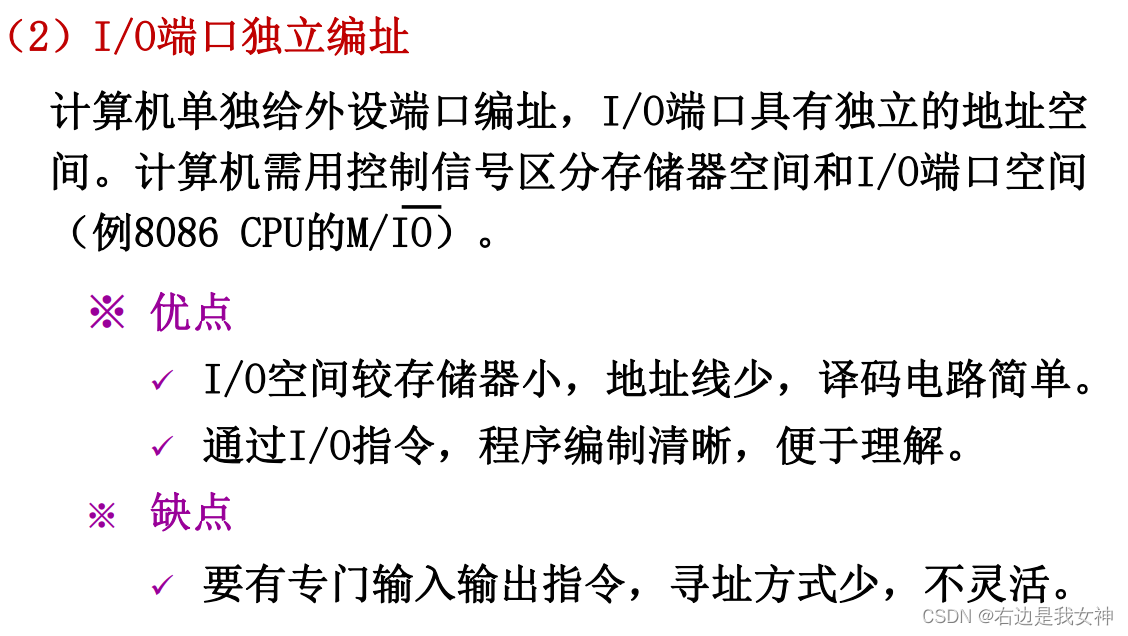

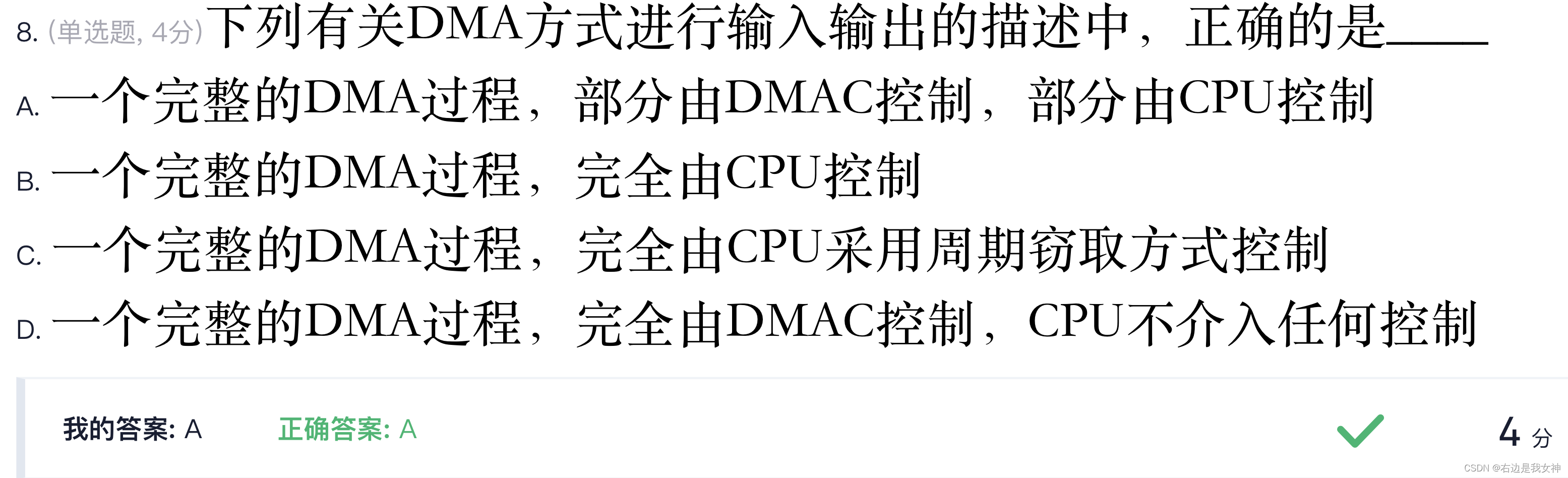

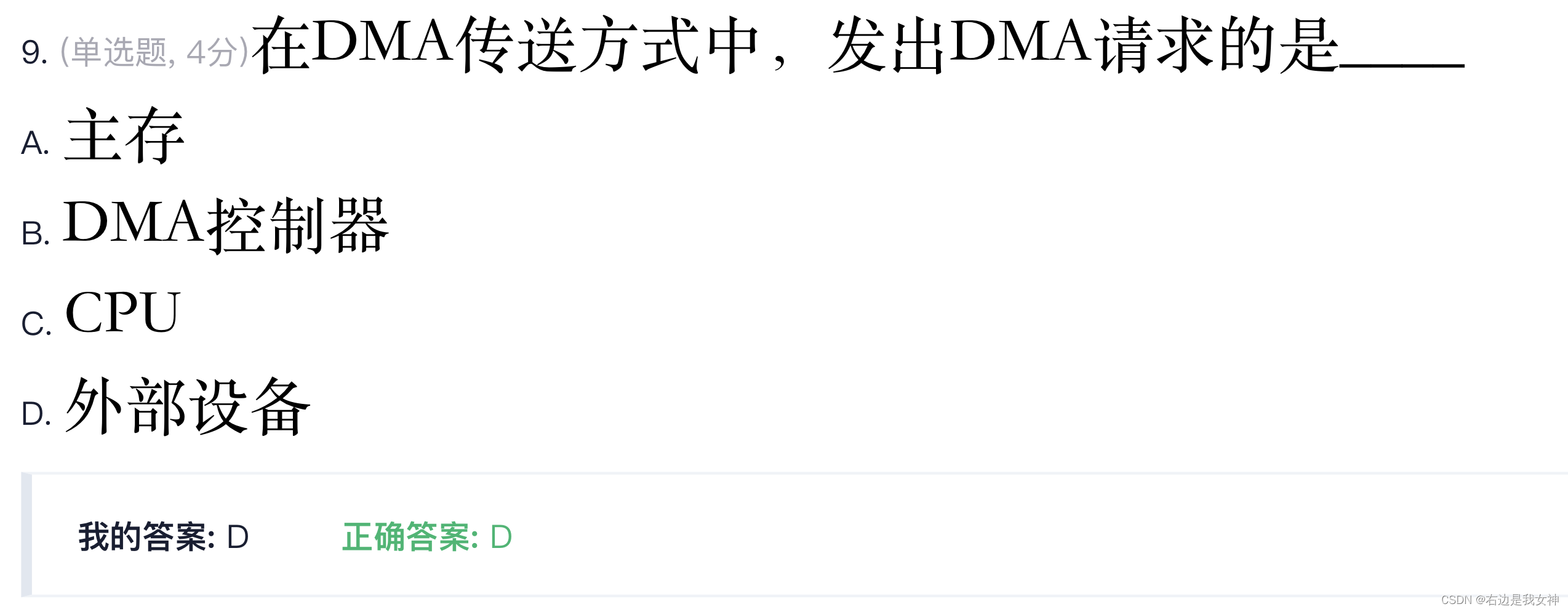

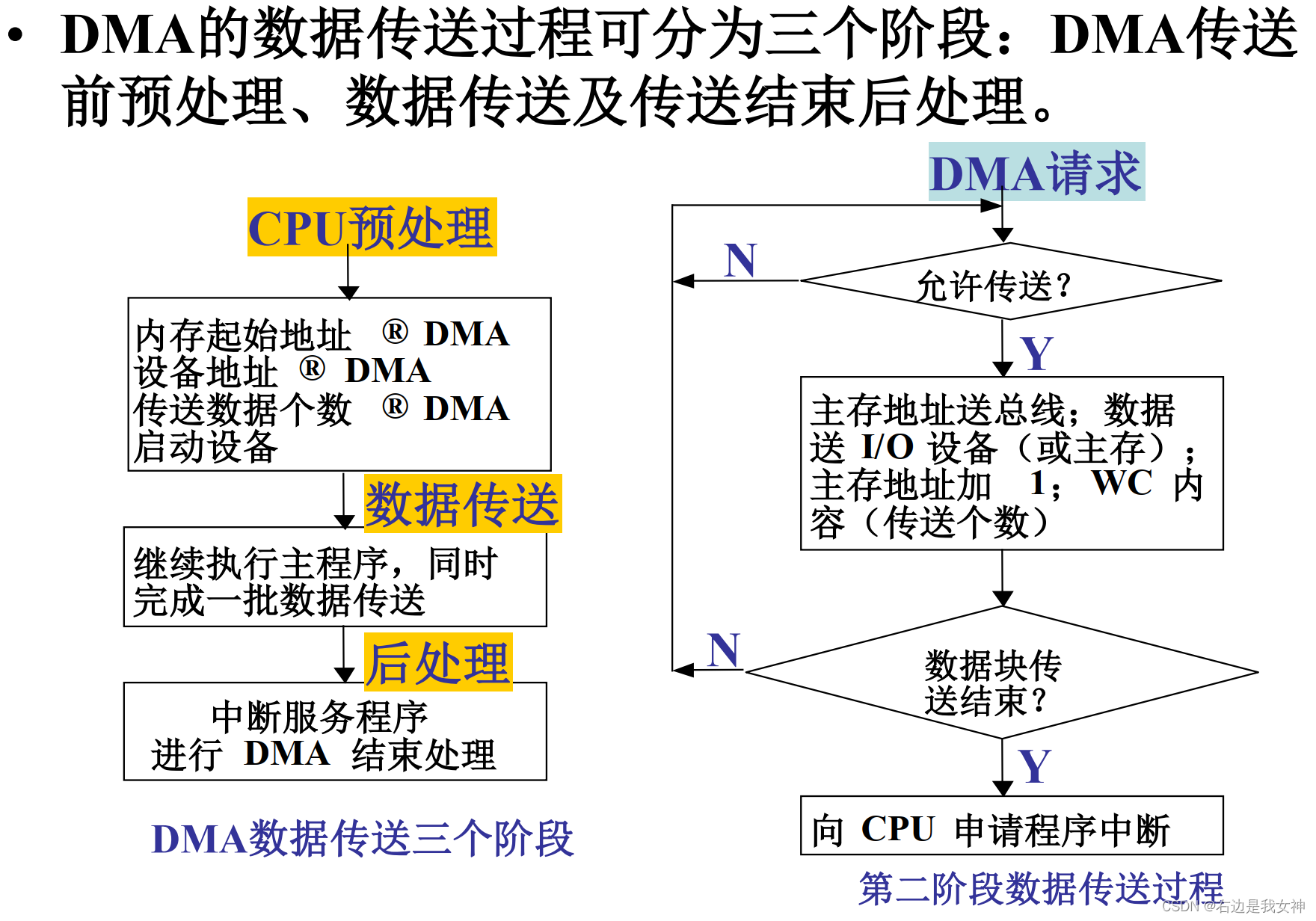

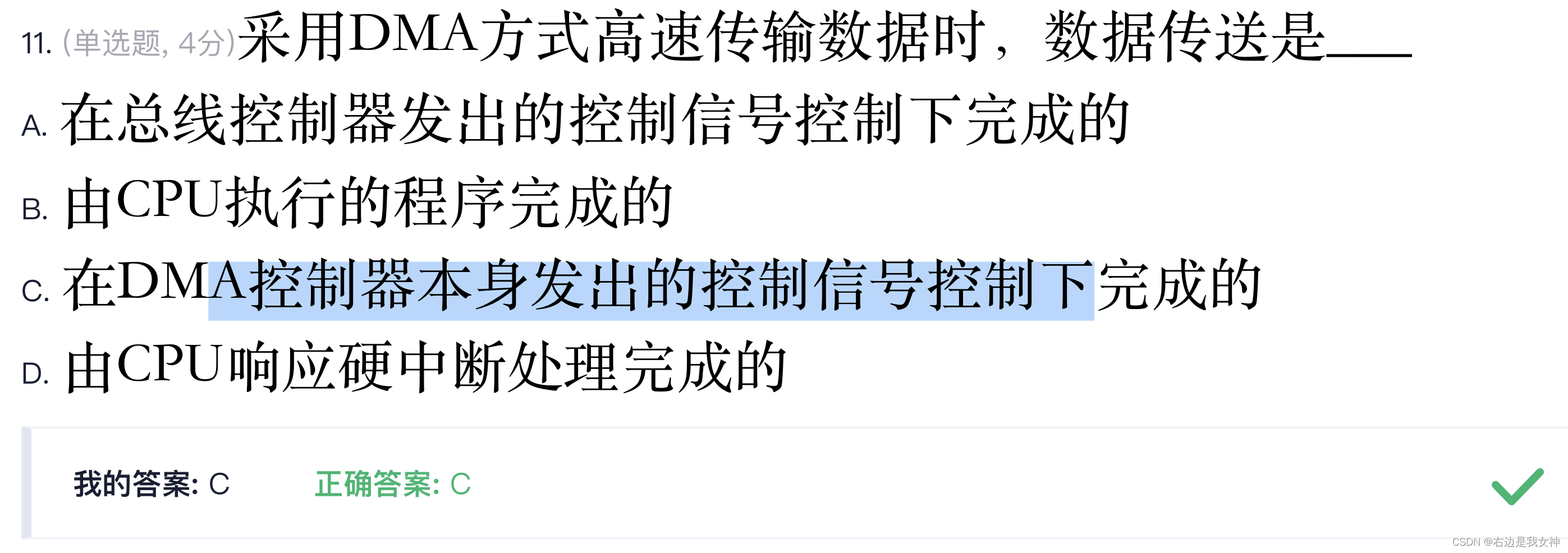

输入输出系统

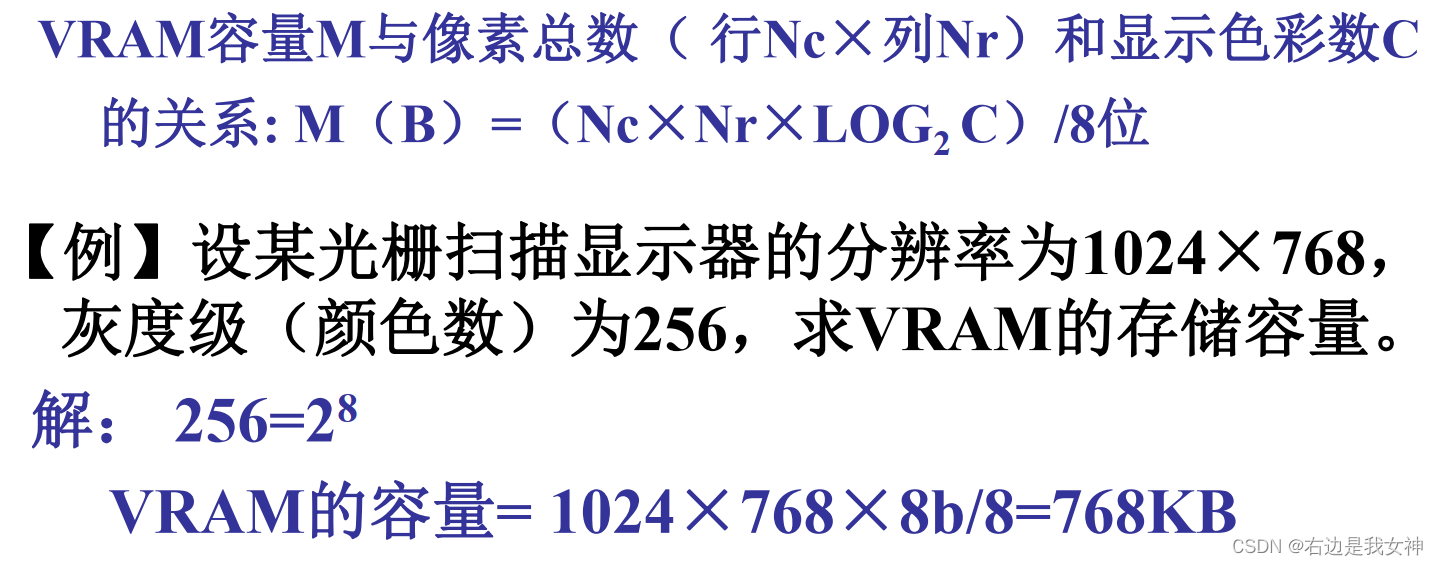

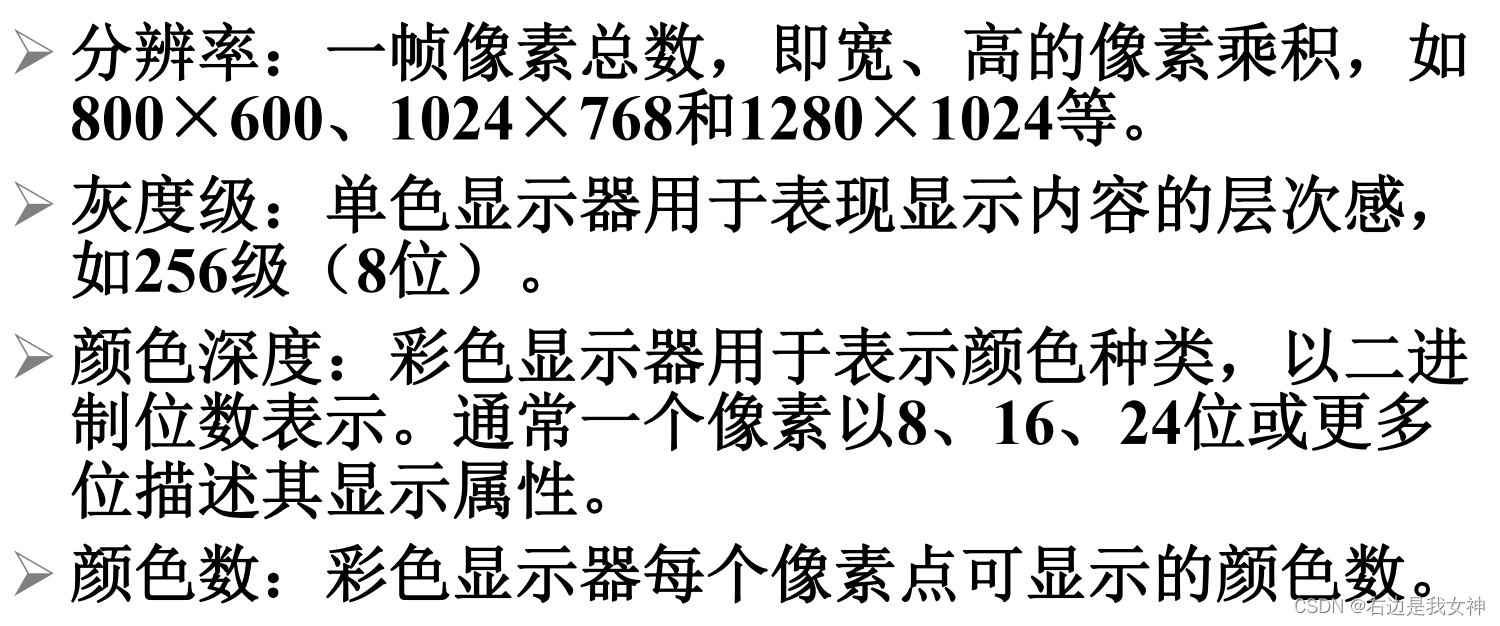

IO的两种编址方式、DMA的三种访存方式、查询花费的时间比率、绘制中断图、写屏蔽字、显示器性能指标相关

接口:外设和总线之间的中间环节。在完成各个外设和主机之间数据传输过程中,进行各种协调等工作的逻辑部件或电路。

端口:接口电路中可以被访问的单元,有独立的端口地址,可分为数据端口、状态端口、控制端口。

总线:

中断:CPU暂时中止当前程序运行,转去处理随机出现的情况或有意安排的任务,在处理结束后能自动恢复原程序的执行。

中断源:引起中断产生的事件或者发生中断请求的来源。

断点:程序被中断的地址。

中断响应:CPU响应中断,停止现行程序的运行,准备进入中断处理阶段。

中断服务程序:

中断向量:中断服务程序入口地址。

中断向量表:存放所有中断向量的一段内存区域。

中断向量地址:访问中断向量表的地址。

中断嵌套(多重中断处理):在处理某一个中断的过程中又发生了新的更高级中断源的中断申请,且CPU又处于中断状态下,CPU就要中断该服务程序的执行,在保存断点和现场后,转去响应优先级更高的中断请求,并执行新的中断服务程序。

中断优先级:

中断屏蔽:给每个中断源配置一位屏蔽触发器,置1表示阻止该中断源的请求,0表示可以正常申请,并将所有的触发器组成一个中断屏蔽寄存器,通过指令可对其设置和修改。

开中断:CPU允许接受中断请求

关中断:

DMA:IO设备与主存储器之间由硬件组成的直接数据通路,主要用于高速IO设备与主存之间的成批数据传送。

通道:

外围处理机:

- 保护现场;

- 中断事件处理;

- 恢复现场;

- 开中断;

- 中断返回。

1485

1485

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?