欢迎关注微信公众号:DRAM视界

其实LPDDR系列是没有PDA mode的。他是DIMM特有的。为什么呢?

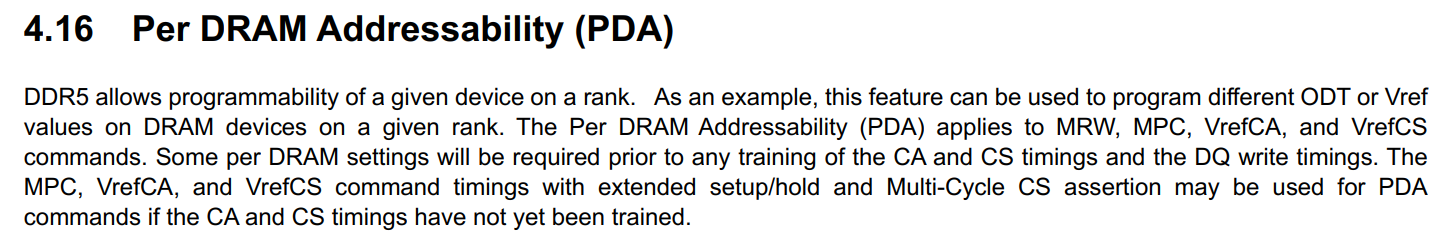

PDA = Per DRAM Addressability 意思是可以单独对每颗DRAM进行寻址。寻址是用来给DIMM上的每个DRAM颗粒设置不一样的配置。设置不一样的配置的目的主要是因为DIMM上不同location的颗粒需要的最佳配置可能是不一样的,所以根据training结果需要配置不一样的值的时候,就用到了PDA功能。如果不用PDA的话,能不能做到DIMM内不同颗粒之间设置不同的值呢?做不到的。因为DIMM上同一个channel的同一个rank内,CS是share的(dual rank的CS会分开)。CS share意味着我们默认情况下只能所有颗粒接受同一个command,包括MRW command.下图是DDR5 spec里面对PDA章节的描述。

DDR4 vs DDR5的PDA的细节上,DDR5针对性的做了改进。

**

DDR4的PDA实现方式如下:

**

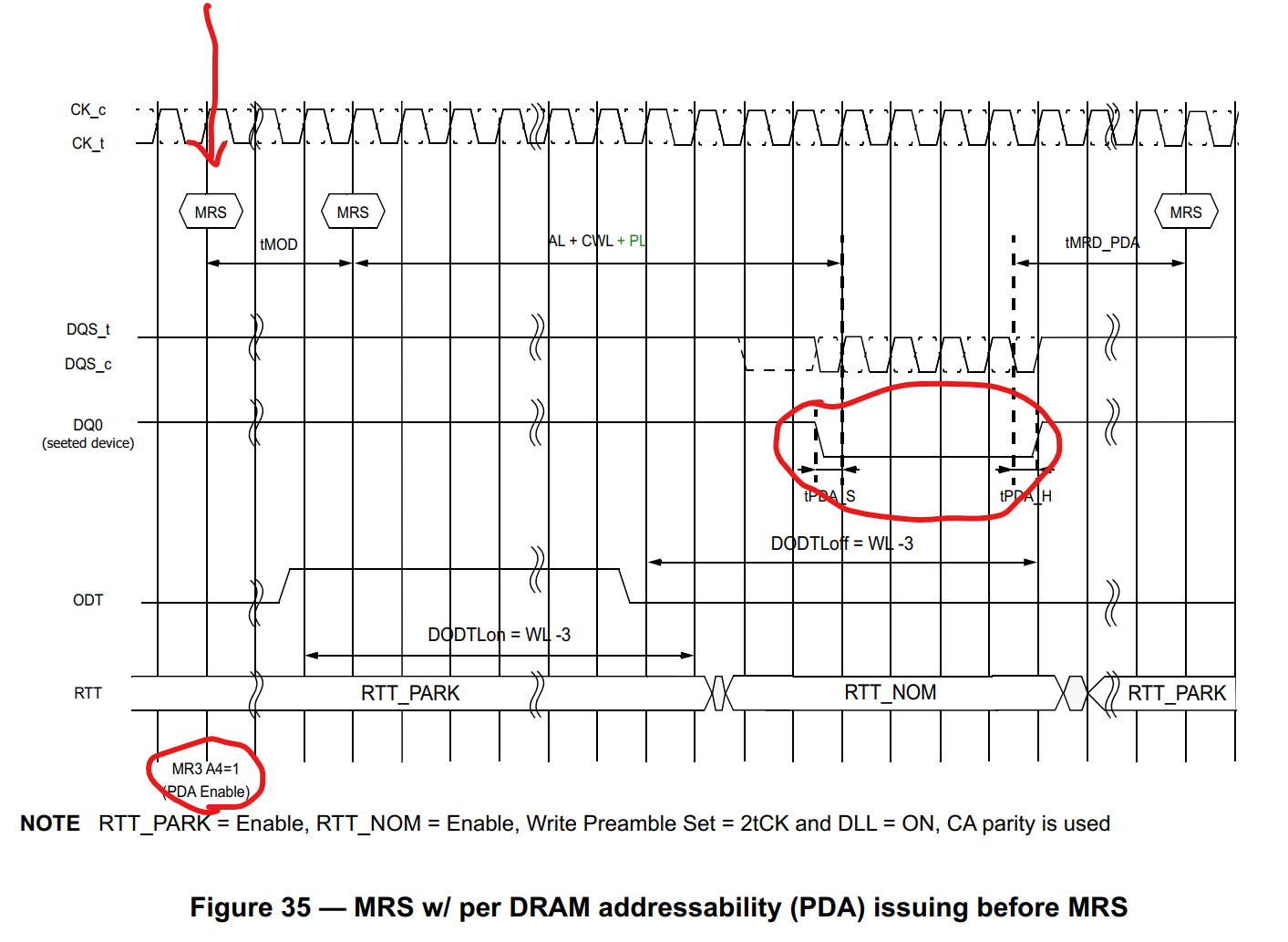

MR3 A4=1 enable PDA mode,意味着加下来的MR设定是在PDA mode下面进行的。跟normal mode的差别是PDA mode下,MRW是否有效,需要通过DQ0来判定。DQ0=Low的时候,才表明这个MRW是有效的。从而DIMM上通过不同DQ来select MRW有效的颗粒,从而实现不同的颗粒实现不一样的MR设定。

PDA mode会用在给不同的颗粒配置不同的VrefDQ value来给DQ提供最佳的reference值。但是/BUT这个地方的risk是PDA mode是需要通过DQ来select device的。所以如果VrefDQ最佳值与default VrefDQ差异太大,可能刚开始的PDA mode就是进不去的(因为VrefDQ default值不适用,最佳值又需要PDA来配置),导致了一个逻辑上的死循环。那么解这个死锁的关键是default的VrefDQ怎么着也得是DQ能拿来用的。不然就完犊子了。BTW: DQ0给了那么长时间的low,也是为了确保DQ能被有效的采集到。

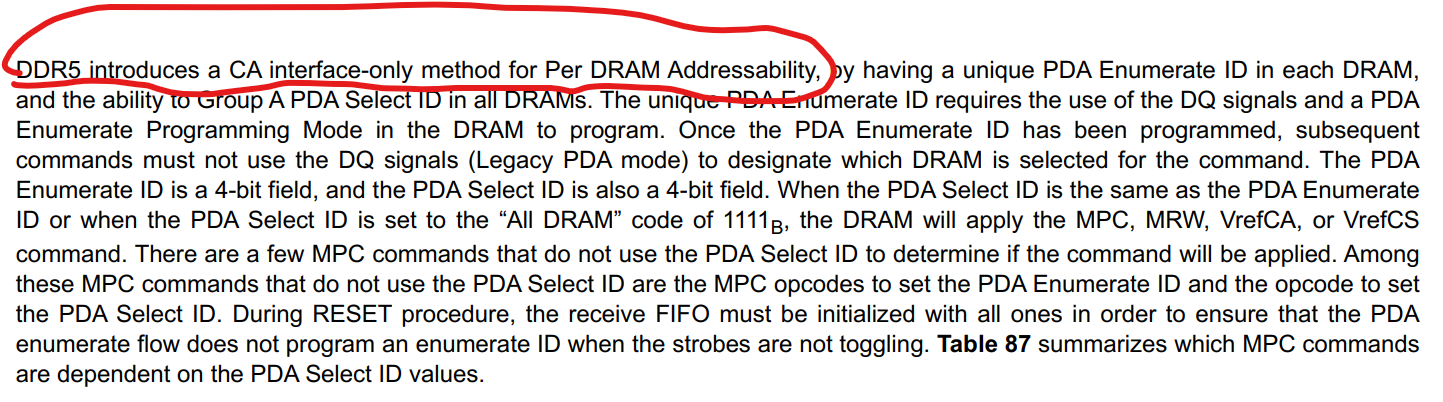

我们且看DDR5的更新的部分:

DDR5的PDA实现方式如下:

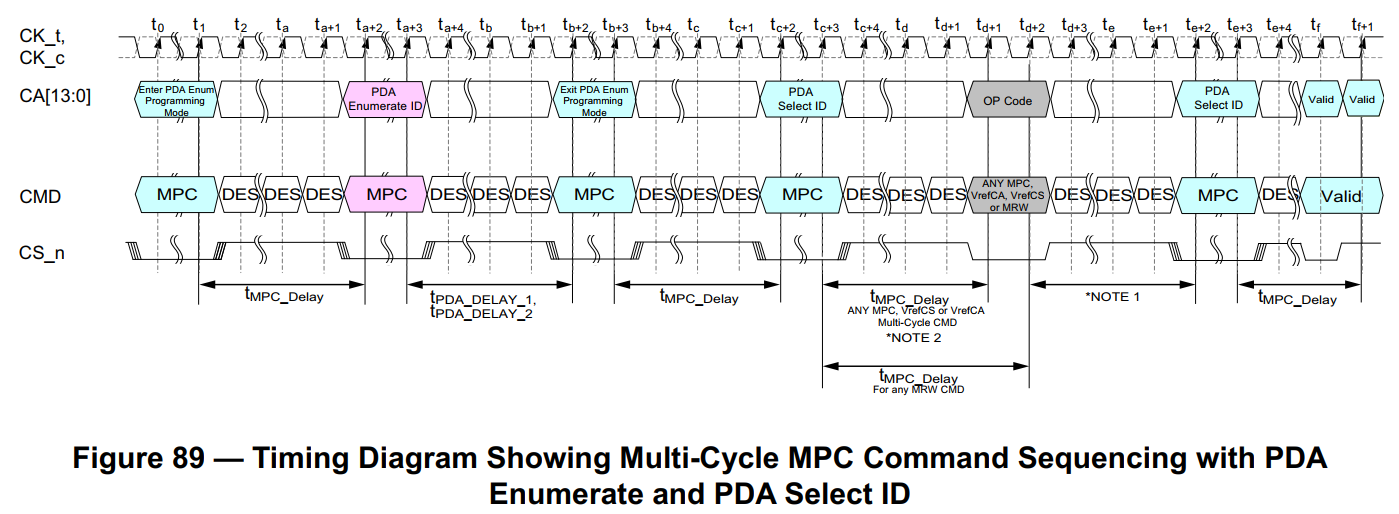

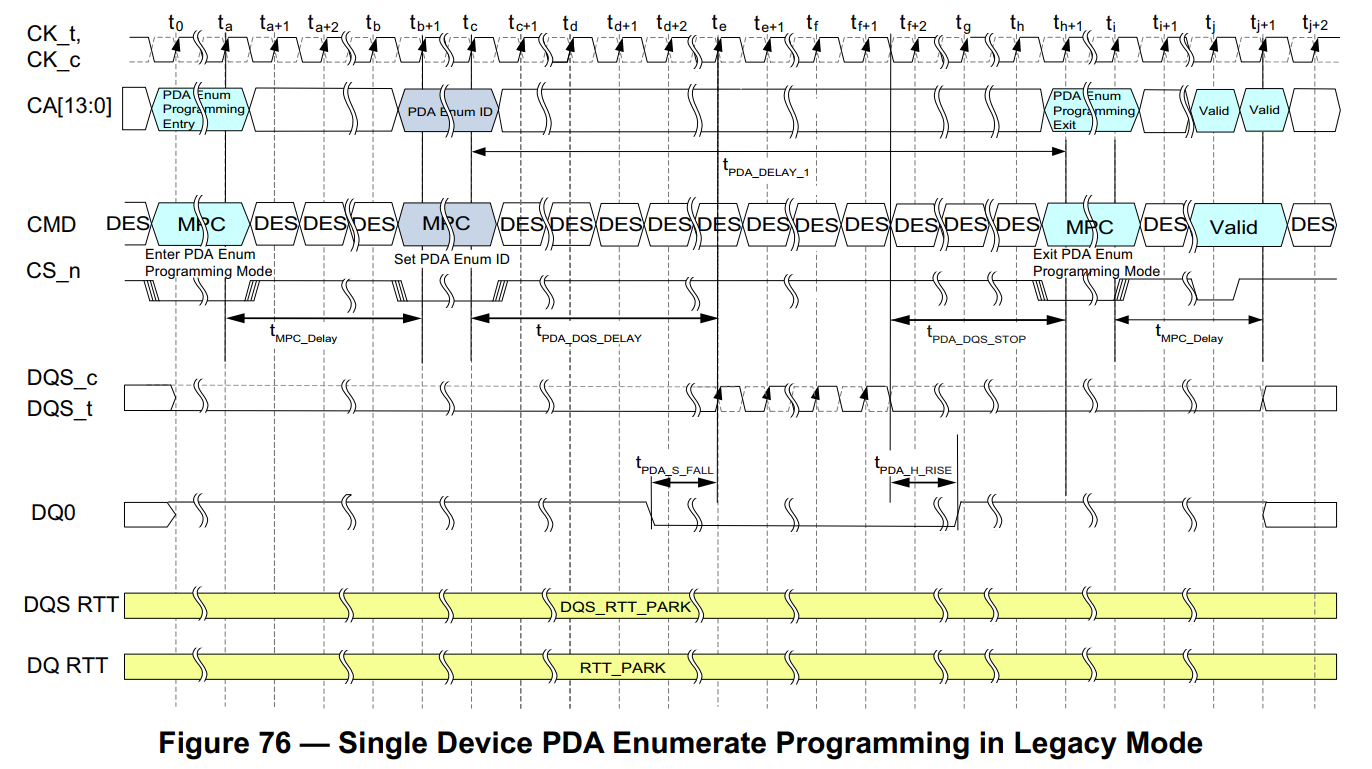

图中圈出来的部分的意思是,DDR5的PDA mode,只用到了CA. 大体flow是先通过DQ0来枚举ID,也就是给DIMM上的每个device配置一个ID, 然后需要更改MR的时候,通过ID来确定哪个颗粒来接受这笔MR command

枚举ID的时序图如下所示(依然需要DQ来决定哪个颗粒生效).

DDR5在枚举ID的过程中依然可能存在DDR4里面说的死锁,当然唯一避免的办法也是只能保证default的VrefDQ是肯定能用的。

那么DDR5的PDA的更改的地方,会让DDR5的PDA有更高的灵活性。系统只要前期把DIMM上不同位置的颗粒的ID配置好,后面配置MR设定的时候就特别轻松。而且随着training flow越来越精细,越来越复杂,DIMM上对PDA的应用越来越多,牵涉到的MR配置也越来越多,DDR5的PDA的新的改动会让PDA在系统的应用更方便。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?