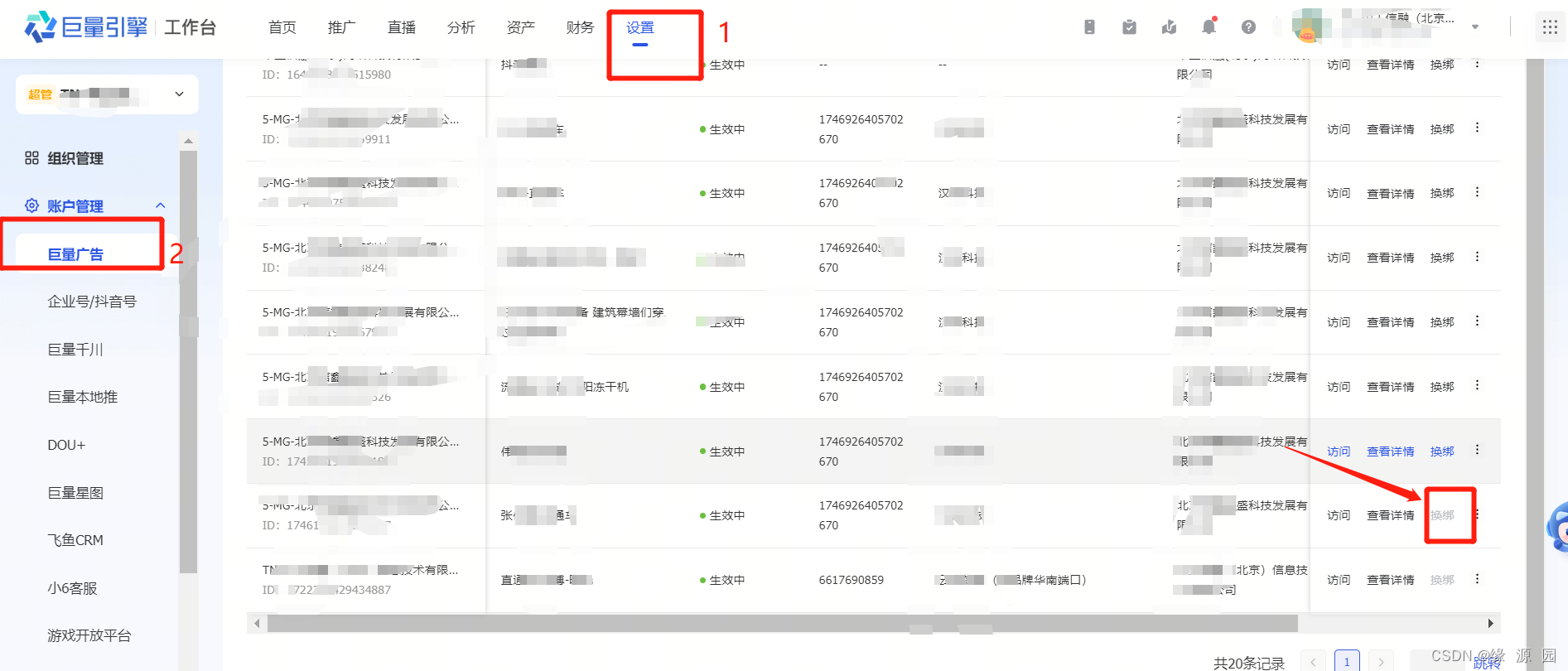

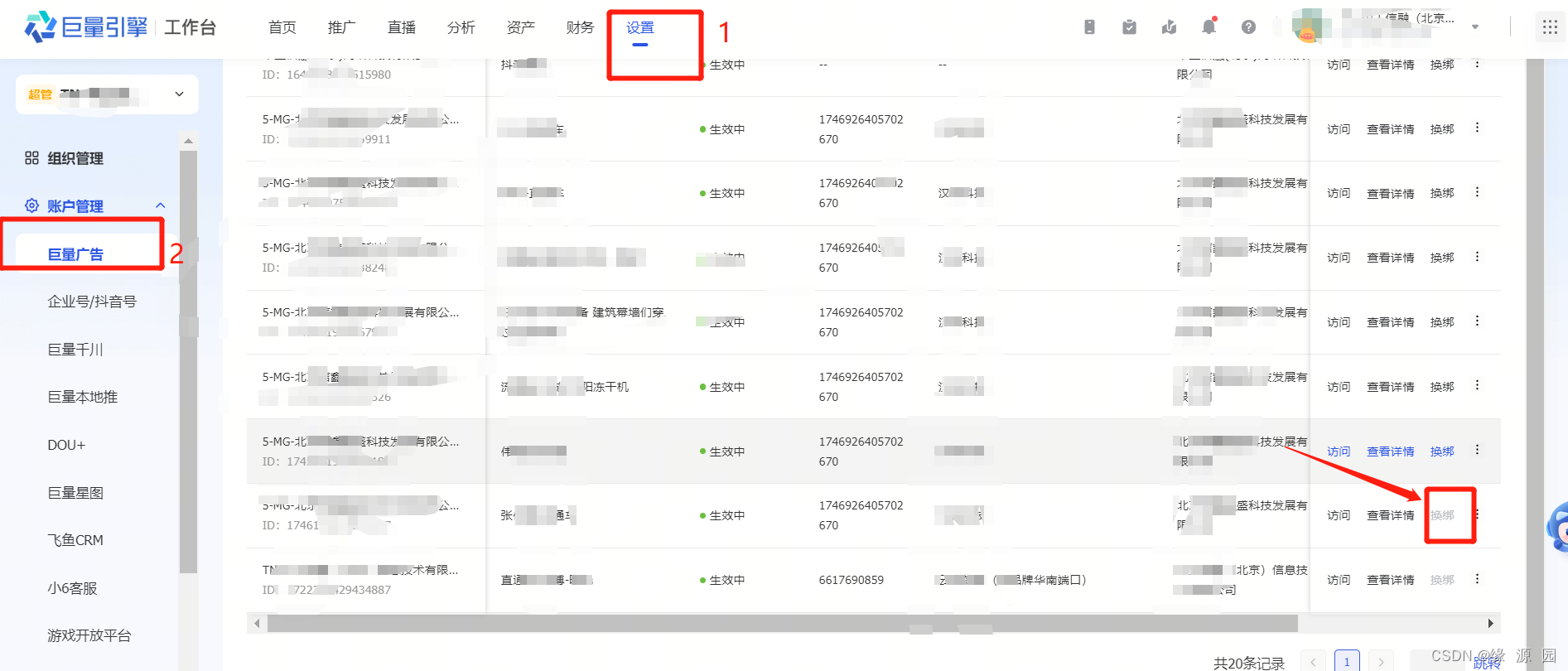

1、如果已有账户,对现有账户做转移操作。

2、换绑必须有邮箱地址。协作关系可选。

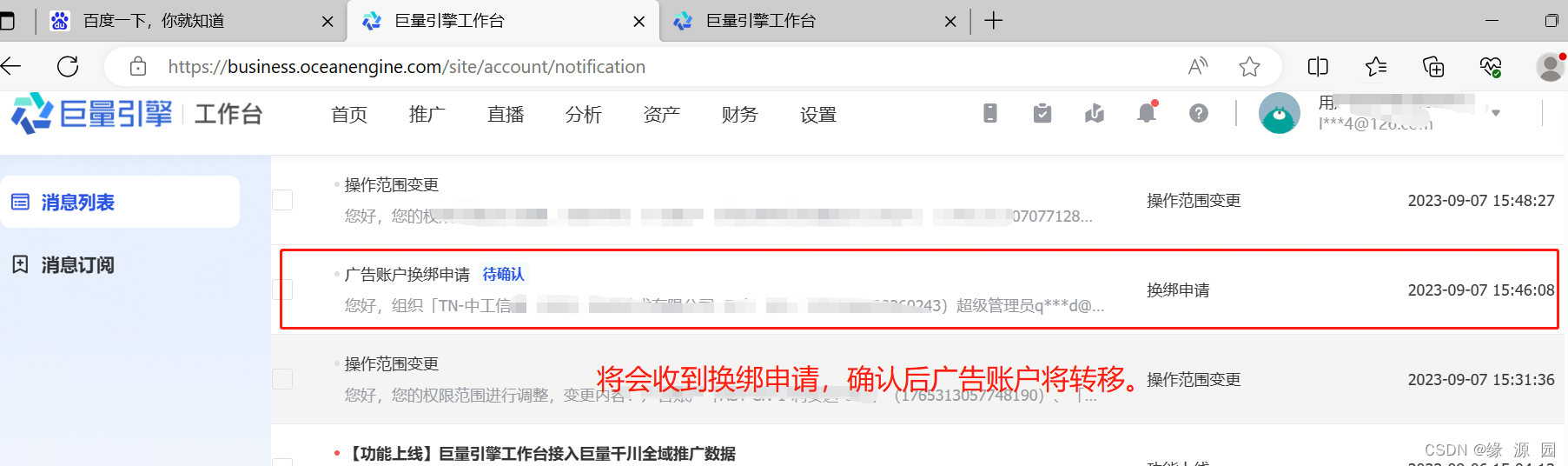

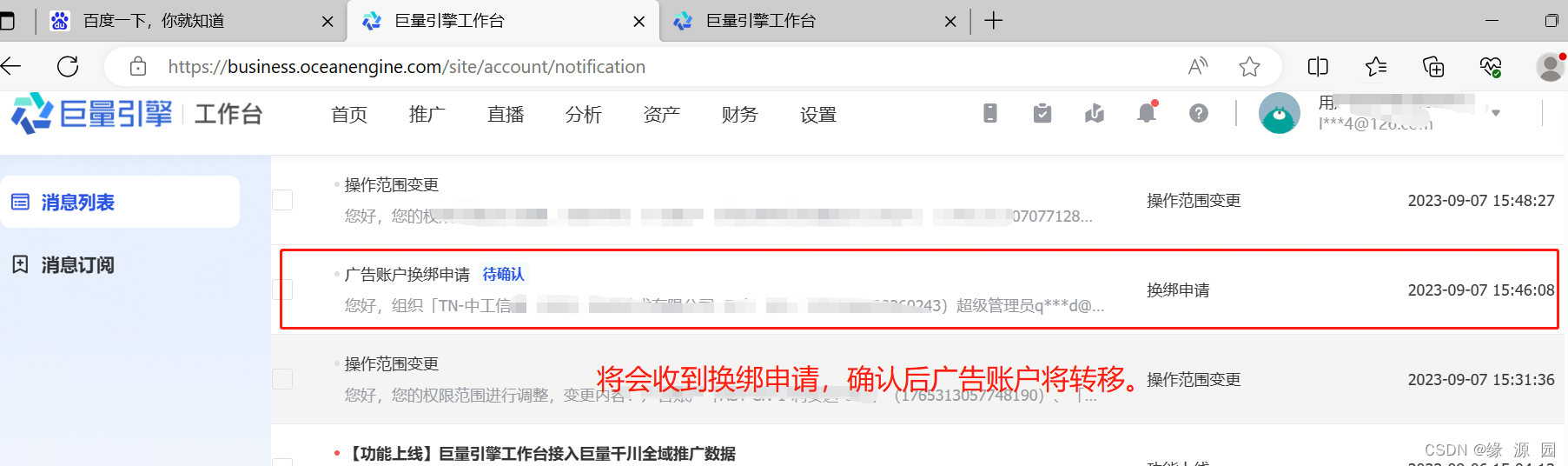

3、子账户将收到换绑的申请,理论上同意即可。

4、点击同意换绑申请,即将可以管理时,出现了未完成认证的提示。(我们需要完成实名认证)

5、检查账户是否认证。设置——组织管理可查。

6、则需要进行实名认证。个人账户则需要提供身份证正反面,即可确认成功。也可进行企业实名认证,注意一旦确认主体不可更改。

7、账户授权成功。此账户可管理被授权的广告账户。

2664

2664

2083

2083

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?