第六章 总线系统

6.1 总线的概念和结构

6.1.1 总线的基本参数

总线是一组能为多个部件分时共享的公共信息传送线路。其特点就是分时和共享

- 分时是指同一时刻只允许一个部件向CPU发送信息

- 共享是指总线上可以挂接多个部件。某一时刻只允许一个设备向总线发送信息,但同时可以有多个设备接收信息

总线特性

- 物理特性:是指总线的物理连接方式,包括总线根数,插头、插座形状

- 功能特性:是指总线的功能,例如:数据总线、地址总线和逻辑总线

- 电气特性:是指信号的传递方向和有效电平范围

- 时间特性:规定了总线上信号的时序关系

总线的性能指标(出现计算题)

- 总线宽度:数据线的根数

- 总线带宽:数据的传输速率,即单位时间(一个总线周期)内总线上传输数据的位数

- 总线复用:是指地址线与数据线是否复用

- 总线控制方式:链式、计数、独立

这里常考计算总线的带宽(最大数据传输率)

题目会给出时钟频率,总线周期与时钟周期的关系和总线一个周期内传输的位数或字节数(1字节等于8位)

例:总线宽度为32位(4字节),时钟频率为100MHz,若总线上每4个时钟周期传送一个32bit的字,问总线带宽是多少?

解:1个时钟周期为 1 100 M H Z = 0.01 μ s \frac {1}{100MHZ} = 0.01 \mu s 100MHZ1=0.01μs

总线周期为 0.01 μ s × 4 = 0.04 μ s 0.01\mu s×4 = 0.04\mu s 0.01μs×4=0.04μs

总线的数据传输速率为 32 b 0.04 μ s = 4 B 0.04 μ s = 100 M B p s \frac {32b}{0.04\mu s} = \frac {4B}{0.04\mu s}=100MBps 0.04μs32b=0.04μs4B=100MBps

6.1.2 总线的连接方式

单总线结构

计算机中的CPU、主存和I/O设备需要进行数据交互,所以就需要一组线来在他们之间传输数据。

在单总线中,同一时刻只能有一个设备获得总线的使用权。当不再使用总线时,要迅速放弃总线的使用权,否则会影响其他部件使用总线。

单总线结构不是指只有一根信号线,系统总线按照传送信息的不同分为地址总线、数据总线和控制总线

双总线结构

因为CPU与主存数据交互十分频繁,在单总线结构中会频繁地占有总线,所以我们在CPU和主存之间专门设置了一组存储总线。

三总线结构

在双总线结构的基础上增加了I/O总线。I/O设备通常速度较慢,所以我们设计了一个IOP(I/O处理器)来模拟CPU处理I/O请求。操作系统课程中我们学过,这种部件叫做通道。

多总线结构

目前计算机已采用了多总线结构,在CPU、主存、I/O之间互联采用多条总线。

挂在总线上的部件可以同时从总线接收数据,但只能分时向总线发送数据

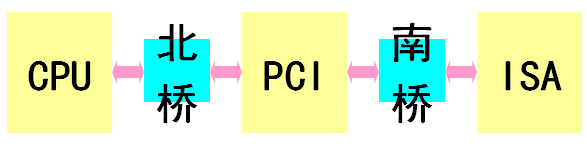

在多总线结构中,总线结构分为:CPU总线、PCI总线和ISA总线

- CPU总线:连接CPU和主存设备

- PCI总线:连接高速的I/O设备

- ISA总线:连接低速I/O设备

6.2 总线接口

6.2.1 数据的传送方式

并行传送

早期计算机普遍采用并行传送,但后来人们发现并行传送的方式并不理想,原因如下

- 每一数据位需要一条传输线

- 每一批传输数据后需要等待数据对齐后再发送

串行传送

只需要一条传输线,而且不需要等待对齐。

分时传送

同一部件总线复用或共享总线的部件分时使用。

6.2.2 总线接口的概念

I/O接口是CPU和主存、外设之间通过总线进行连接的逻辑部件。为什么不让总线直接连接CPU和外设呢?因为外设实在是太慢了,所以增加了一个I/O接口来缓冲速度上的差异;对于多个同一种外围设备,我们可以控制他们的接口来统一控制设备,也便于我们管理它们的状态;当CPU要传输数据时,该数据可能不会被外围设备识别,那就需要I/O接口充当一个适配器,按照我们的要求进行数据转换。这在《设计模式》中称为“适配器模式”。

6.3 总线的仲裁(重点)

之前我们说过,对于单总线来同一时刻可以有多个功能模块从总线接受数据,但同时只能有一个模块向总线发送数据。因此我们说,向总线发送数据的模块称为主方,响应主方请求的称为从方。

因为同一时刻只能有一个主方操作总线,所以为了解决多个主方争用总线的问题,我们在CPU中必须设置总线仲裁部件。

6.3.1 集中式仲裁

链式查询方式

先解释一下BG、BR和BS:

- BG(Bus Grant)是总线允许的信号线,在这条信号线上查询是谁发出了总线请求

- BR(Bus Request)是总线请求的信号线,功能模块在这条信号线上向总线控制部件发出请求信号

- BS(Bus State)是总线忙的信号线,是功能模块来通知控制模块此时总线已经被我占用

链式查询方式就是类似于将设备结构串联起来。每当控制部件收到BR的信号时,就从0号接口开始询问,直到n号结构为止。

- 优点:设计简单,容易添加设备

- 缺点:优先级固定。一旦前面的设备出现电路故障,后面发出请求的设备就无法反馈BG的信号

计数器定时查询方式

因为链式查询方式的优先级固定,越靠近控制部件的优先级越高。所以我们采用动态优先级,即在控制部件中设置一个计数器。每次查询时,我们指定一个计数值 i i i,BG就从第 i i i个总线设备开始询问:若计数值与设备号相等,则该设备获得控制权并终止查询和计数;若不相等则计数值+1。

-

优点:①计数器的初始值可以改变优先的次序②电路发生故障不会影响到之后的设备

-

缺点:需要有 ⌈ l o g 2 n ⌉ + 2 \lceil log_2n \rceil +2 ⌈log2n⌉+2条地址线。

假设一共有n个设备,有x条地址线,一条地址线信号为0或1,其最多能表示两个设备。那么x条地址线可表示 2 x 2^x 2x个设备。则设备地址线需要 x = l o g 2 n x = log_2n x=log2n,加上BS和BR线。这种方式不需要BG线,即不需要通过总线控制器的允许。

独立请求方式

独立请求方式就是对每一个设备都设置一个BG线和BR线。当第 i i i个设备发出 B R i BR_i BRi时,控制部件收到后通过 B G i BG_i BGi反馈。各个设备间的传输是互相独立的,不会受到彼此的干扰。

-

优点:①可以自定义优先级次序②反应速度快

-

缺点:①若有n个设备,则需要2n+1根线②控制逻辑更复杂(自定义优先级)

对于n个设备,每个设备都需要一个BG和BR,还额外需要一条BS线。

需要记住每种仲裁方式所需要的线数,响应速度,对电路故障的敏感程度和实现的原理

6.3.2 分布式仲裁

集中式仲裁只有一个仲裁器,也就是控制部件。而分布式仲裁有多个仲裁器,每个仲裁器都有一个仲裁号。当有总线请求时,把它们唯一的仲裁号发送到共享的仲裁总线上,每个仲裁器将仲裁总线上得到的号与自己的号进行比较。如果仲裁总线上的号大,则它的总线请求不予响应,并撤消它的仲裁号。最后,获胜者的仲裁号保留在仲裁总线上。

6.4 总线的定时和数据传送模式

6.4.1 总线同步定时

总线定时共有五个阶段:

-

请求总线:主设备向总线控制器提出申请

-

总线仲裁:仲裁机构决定将下一周期的总线授予某一申请者

-

寻址:找到获得使用权设备的地址

-

信息传送:设备通过总线传输数据

-

状态返回:撤销该设备在总线上的信息,让出总线使用权

同步定时方式就是指系统采用了一个统一的时钟信号来协调发送和接受双方的传送时间关系。在一个总线周期中,发送和接收方可以进行一次数据传输

- 优点:传送速度快,适合所接部件的存取时间较接近的系统;总线控制逻辑简单

- 缺点:不能及时进行数据的检验,可能存在坏值和噪声

6.4.2 总线异步定时

总线之间主要是通过异步方式进行通信,分别为非互锁、半互锁和全互锁

总线通信通常有一个发出请求,有一个接受请求。

- 发请求方:需要让对方知道我发出了请求;需要让对方知道收到了对方的答复

- 接受请求方:需要让对方知道做出了答复;需要让对方知道收到了对方的答复

非互锁

非互锁就是两条总线之间没有约束条件。假设A(主设备)向B发出一个请求,A此时不需要知道B是否收到,会在一段时间后撤销请求信号;B(从设备)假如接收到信号后,会发出一条答复,但不管对方是否收到答复,一段时候会自动撤回。

通俗点理解就是,你在菜市场丢了一本书,你回到家里发现以后就回到了菜市场等了一会发现没人挂失物招领,你就走了;有个人发现菜市场莫名其妙有本书,觉得可能是谁丢了,就在那等失主。等了一会发现失主没来,自己就把书拿走了······

半互锁

半互锁就是主设备需要等待从设备的答复后再取消请求信号。还是上面的例子,你这次丢了一个钱包,你回到菜市场后一直等,直到出现有人在找钱包的失主;而那个人发现菜市场有个钱包,等了一会失主发现没人来认领,又自己拿走了······

全互锁

全互锁就是主设备和从设备都需要等待对方的答复再取消信号。还是上面的例子,这次你还是要一直等,直到出现有人找钱包的失主;而那个人这次也一直等,直到失主出现,拾金不昧······

什么是猝发式传送?

猝发式传送是在一个总线周期中,总线可以传输多个存储地址连续的数据。即一次传输一批地址连续的数据

- 优点:总线周期可变,适合两个存取速度差距较大的设备进行数据传输

- 缺点:速度慢;逻辑复杂

6.5 总线接口的标准

ISA(Industry Standard Architecture,工业标准体系结构)是最早出现的微型计算机系统总线,传输速率最为8/16 bit,属于并行总线。

PCI(Peripheral Component Interconnect,外部设备互联)是专门为I/O设备、外围部件所设计的。通常与南桥和外围设备相连,支持即插即用,属于并行总线。

PCI-E是PCI的增强版,传输速率更快,属于并行总线。

USB(Universal Serial Bus,通用串行总线)连接外部设备的I/O总线,支持即插即用,属于串行总线。

SATA(Serial Advanced Technology Attachment,串行高级技术附件)是一种串行硬件驱动接口。我记得当时安装硬盘的时候,需要分清自己电脑里是M2接口还是SATA接口(M2接口的硬盘比较小;SATA接口的硬盘大)

本章小结

- 总线有物理特性、功能特性、电气特性、机械特性,因此必须标准化

- 微型计算机系统的标准总线从ISA总线(16位,带宽8MB/s)发展到EISA总线(32位,带宽33.3MB/s)和VESA总线(32位,带宽132MB/s),又进一步发展到PCI总线(64位,带宽264MB/s)

- 衡量总线性能的重要指标是总线带宽,它定义为总线本身所能达到的最高传输速率(选择题会考)

- 集中式仲裁和分布式仲裁

- 总线的同步定时和异步定时

1045

1045

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?