一、定义

UART(Universal Asynchronous Receiver/Transmitter)是一种广泛使用的串行通信协议,用于在设备间通过异步方式传输数据。它无需共享时钟信号,而是依赖双方预先约定的参数(如波特率)完成通信。

功能和特点

基本的 UART 系统只需三个信号即可提供稳健的中速全双工通信:Tx(传输的串行数据)、Rx(接收的串行数据)和接地。

与SPI和I2C等其他协议相比,不需要专门的clock信号来同步数据传输,这是由其独特的通信机制决定的。

异步通信方式:发送方在发送数据时,会根据预设的波特率(即每秒传输的位数)来发送数据,而接收方也根据相同的波特率来接收并解析数据。这种机制使得UART能够在没有外部时钟信号的情况下进行有效的数据传输

内部时钟控制:虽然UART不需要外部的clock信号,但它仍然依赖于内部的时钟信号来控制数据的发送和接收。这些内部时钟信号由UART硬件模块自身提供,用于生成发送和接收数据的节拍。然而,这些内部时钟信号并不需要像SPI或I2C那样通过外部线路传输到其他设备,而是只在本地设备内部起作用。

二、工作原理

将要传输数据的 UART 从数据总线接收数据。数据总线用于通过 CPU、内存或微控制器等其他设备将数据发送到 UART。数据以并行形式从数据总线传输到传输 UART。发送 UART 从数据总线获取并行数据后,添加一个起始位、一个奇偶校验位和一个停止位,从而创建数据包。

接下来,数据包在 Tx 引脚上逐位串行输出。接收 UART 在其 Rx 引脚上逐位读取数据包。然后,接收 UART 将数据转换回并行形式,并删除起始位、奇偶校验位和停止位。最后,接收 UART 将数据包并行传输到接收端的数据总线:

发送 UART 不是 clock 信号,而是将 start 和 stop 位添加到正在传输的数据包中。这些位定义了数据包的开头和结尾,因此接收 UART 知道何时开始读取这些位。

当接收 UART 检测到起始位时,它开始以称为波特率的特定频率读取输入位。波特率是衡量数据传输速度的指标,以每秒位数 (bps) 表示。 两个 UART 必须以大致相同的波特率运行。在位的时序相差太大之前,发送和接收 UART 之间的波特率只能相差约 10%,超过此值,位的时序就会脱节。

两个 UART 还必须配置为发送和接收相同的数据包结构。

关于UART必须了解的几点

波特率

特率表示每秒传输的符号数(单位:bps,bits per second),决定了数据传输的速率。

常见值:9600、19200、38400、57600、115200 bps等

重要性:发送端和接收端的波特率必须一致(波特率误差需控制在允许范围内)。

常见问题:波特率不匹配导致数据乱码;高频时钟误差积累引发通信失败。

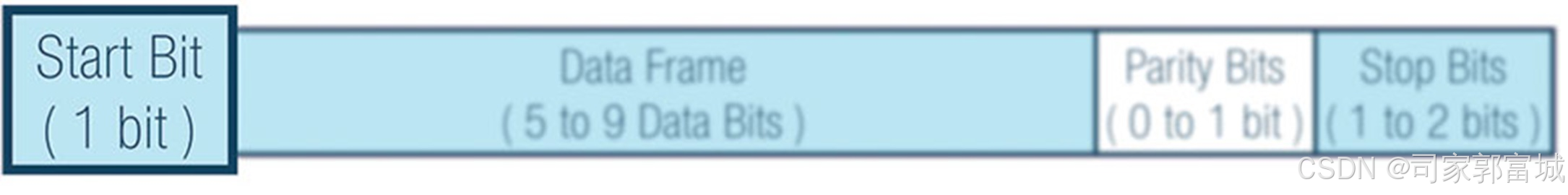

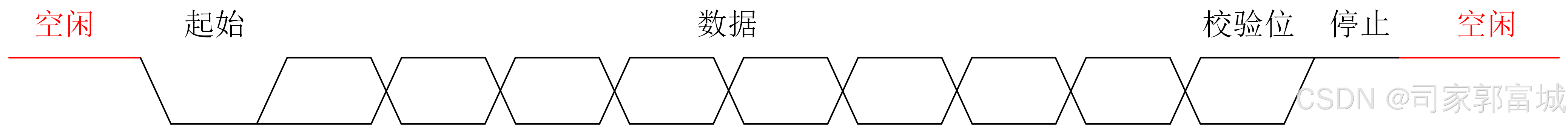

三、协议帧

在UART中,传输模式为数据包形式。连接发送器和接收器的机制包括串行数据包的创建和物理硬件线路的控制。数据包由起始位、数据帧、奇偶校验位和停止位组成。

3.1 起始位

起始位是单字节 UART 传输的 first bit。它指示数据行正在离开其空闲状态。

当不传输数据时,UART数据传输线通常保持高电压电平。若要开始数据传输,发送UART会将传输线从高电平拉到低电平并保持1个时钟周期。当接收UART检测到高到低电压跃迁时,便开始以波特率对应的频率读取数据帧中的位。

起始位是overhead位:它促进了接收器和发射器之间的通信,但不会传输有意义的数据。

3.2 数据帧

数据位包含传输的实际数据,如果使用了奇偶校验,那么数据位长为5~8 bits,如果没有使用奇偶校验,则位长为5~9 bits。在一般情况下,数据位为 8 bits,数据首先从最低有效位开始发送,高位在后。

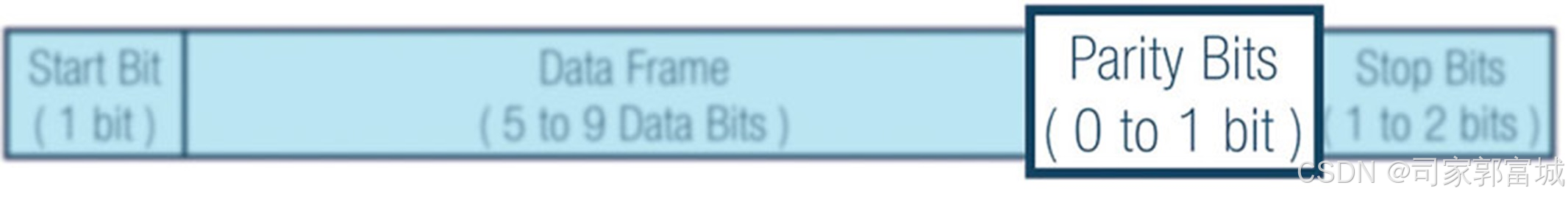

3.3 奇偶校验位

奇偶校验描述数字的偶数或奇数。奇偶校验位是接收 UART 判断传输过程中是否有任何数据发生变化的一种方式。比特可以通过电磁辐射、不匹配的波特率或长距离数据传输来更改。

接收 UART 读取数据帧后,它会计算值为 1 的位数,并检查总数是偶数还是奇数。如果奇偶校验位为 0 (偶数奇偶校验),则数据帧中的 1 或逻辑高位应总计为偶数。如果奇偶校验位是 1 (奇偶校验),则数据帧中的 1 位或逻辑高电平应总计为奇数。

当奇偶校验位与数据匹配时,UART 知道传输没有错误。但是,如果奇偶校验位为 0,总计为奇数,或者奇偶校验位为 1,总计为偶数,则 UART 知道数据帧中的位已更改。

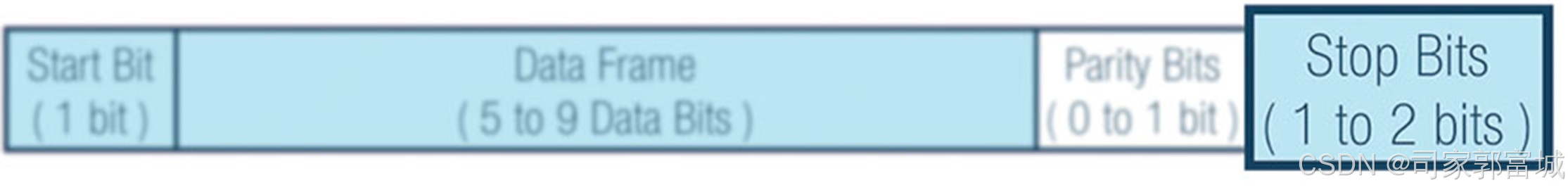

3.4 停止位

为了表示数据包结束,发送UART将数据传输线从低电压驱动到高电压并保持1到2位时间。

空闲位

设备之间不传输数据时以持续的高电平表示空闲。空闲位持续时间越长,两个数据帧间隔也越长,单位时间传输的数据就越少。

四、同步和采样

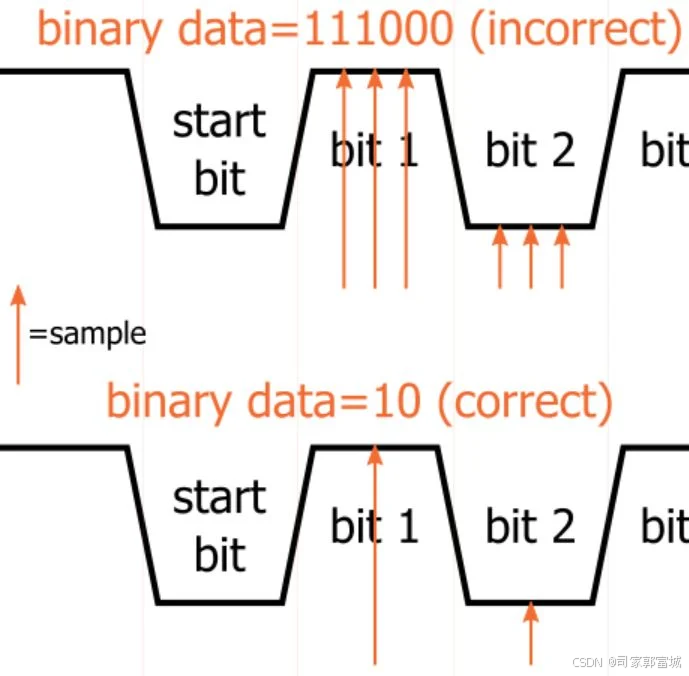

如果没有某种时钟机制,标准数字数据就毫无意义。下图显示了原因:

典型的数据信号是在逻辑低电平和逻辑高电平之间转换的电压。只有当接收器知道何时对信号进行采样时,它才能正确地将这些逻辑状态转换为数字数据。这可以通过使用单独的时钟信号实现。例如,发射器在时钟的每个上升沿更新数据信号,然后接收器在每个下降沿对数据进行采样。

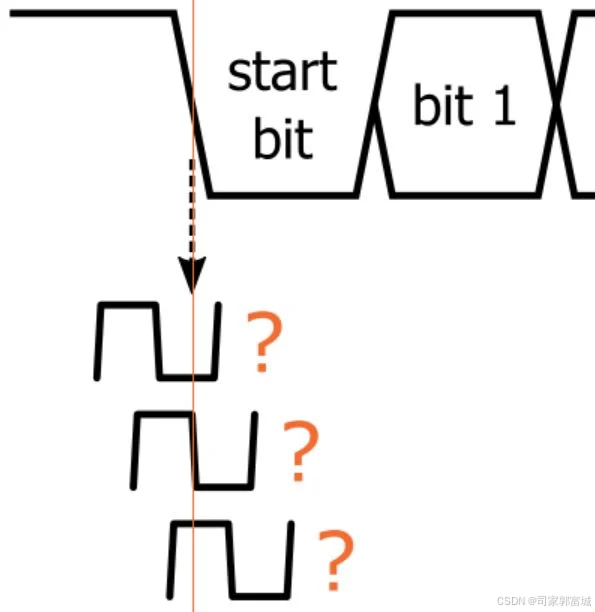

然而UART接口并不使用时钟信号来同步Tx和Rx设备。那么接收器怎么知道何时采样发射器的数据信号呢?

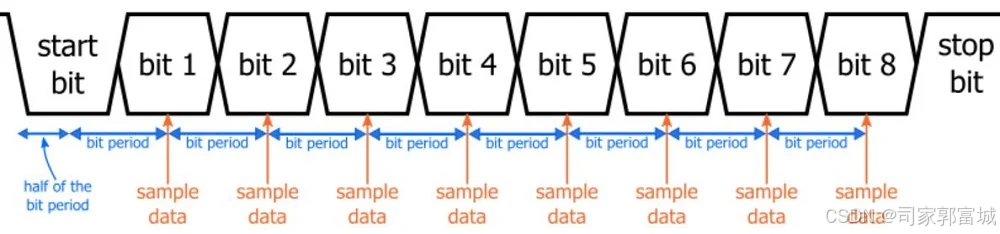

发射器根据其时钟信号产生bit流,然后接收器的目标是使用其内部时钟信号在每个bit的中间时刻对传入的数据进行采样。在bit中间时刻进行采样并非必需,但却是最优的,因为如果在bit开始或结束附近进行采样,会使系统对于接收器和发射器之间时钟频率差异的鲁棒性降低。

接收过程从起始位的下降沿开始。这是关键的同步过程发生的时刻。接收器的内部时钟与发射器的内部时钟完全独立——换句话说,这个第一个下降沿可能对应于接收器时钟周期中的任何一点:

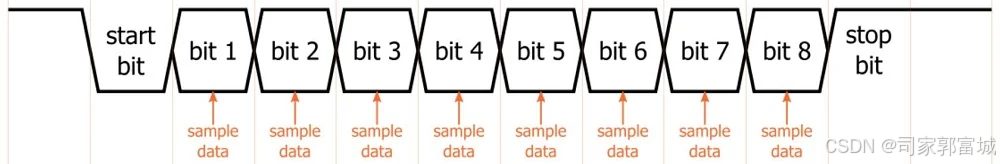

为了确保接收器时钟的有效边沿能接近bit周期的中间时刻发生,发送到接收器模块的波特率时钟频率要比实际的波特率高得多(高8倍、16倍乃至32倍)。

假设一个bit周期对应16个接收器时钟周期。在这种情况下同步和采样可以按如下方式进行:

1)接收过程由起始位的下降沿启动;

2)接收器等待8个时钟周期,以建立一个接近bit周期中间时刻的采样点;

3)然后接收器再等待16个时钟周期,这会使其到达第一个数据位周期的中间时刻;

4)第一个数据位被采样并存储在接收寄存器中,然后该模块再等待16个时钟周期才对第二个数据位进行采样;

5) 这个过程一直重复,直到所有的数据位都被采样和存储完毕;之后,停止位的上升沿会使UART接口返回到空闲状态。

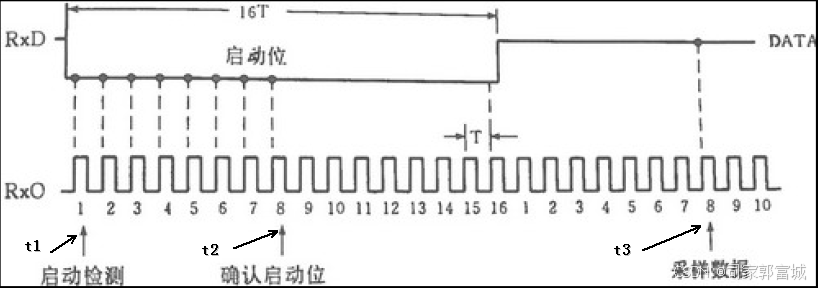

UART串口通信16倍过采样数据

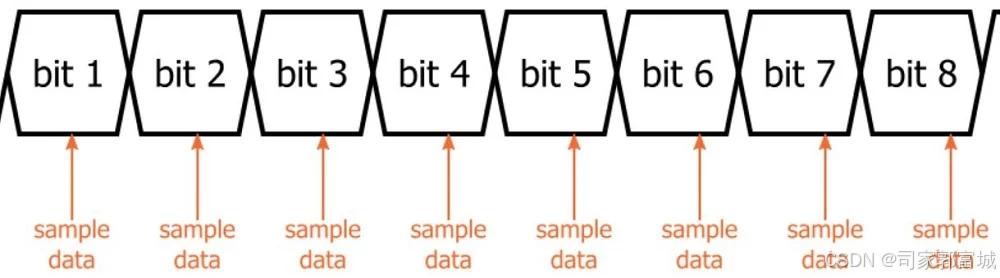

标准UART的RXD前端有一个1“到0跳变检测器”,当其连续接受到8个RXD上的地电平时,该检测器就认为RXD线出现了起始位,进入接受数据状态。

在接受状态,接受控制器对数据位7,8,9三个脉冲采样,并遵从三中取二的原则确定最终值。采用这一方法的根本目的还是为了增强抗干扰,提高数据传送的可靠性,采样信号总是在每个接受位的中间位置,可以避开数据位两端的边沿失真,也可以防止接受时钟频率和发送时钟频率不完全同步引起的误差。

结合图示,讲解如何让采样时刻处于被采样数据的时间中间点:

1)在t1时刻若检测到低电平,就开始对这个低电平进行连续的检测;

2)当检测了8个时钟周期后,到达t2,此刻,若前面的8个周期都是低电平,则认为检测到了起始脉冲。否则就认为是干扰,重新检测;

3)在检测到起始位后,再计数16个采样时钟周期就到达了第一个数据位的时间中间点t3,在此刻采样数据并进行保存;

4)然后再经过16个周期,就是第二个数据位的时间中间点,在此时刻进行采样;然后,再经过16个周期,就是第三个数据位的时间中间点,在此时刻进行采样…..一直这样采样,直到把所有的数据位采样完毕。

五、波特率误差

由于UART接口缺少外部时钟,因此只有当内部波特率相等时,发送端和接收端设备才能进行可靠地数据通信。然而“相等”并不是一个真正的工程词 - 我们总是要考虑噪声,误差和变化。

唯一相关的误差是发射器的波特率和接收器的波特率之间的差异。

如果接收器波特率与发射器波特率完全匹配,并且第一个位在位周期的正中间采样,则最后一个数据位也将在位周期的正中间采样。

如果波特率(以及位周期)不同,则每个采样点将逐渐靠近位转换。换句话说,最后一个数据位是受波特率差异影响最严重的数据位(为方便起见,我们始终假设 Rx 位周期比 Tx 位周期长;如果我们假设 Rx 位周期较短,结果将是相同的)。

5.1 简单评估波特率最大允许误差

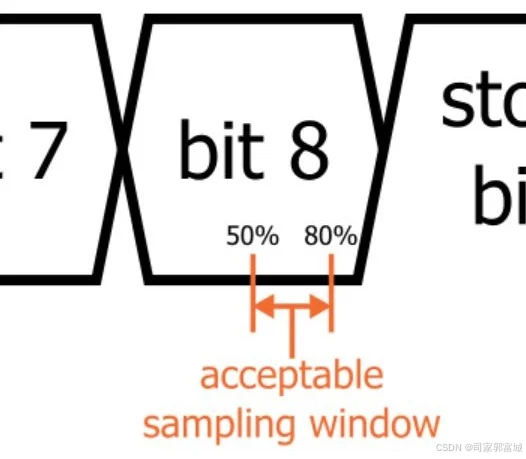

如果最后一个bit在从最后一个数据位bit到停止位bit的转换之前被采样,那么波特率就是足够准确的(在这里,我们假设系统可以容忍对停止位bit的错误采样)。

但是我们不希望在预期转换之前(1ns或更短时间)进行采样,我们需要一些余量。一般认为一个合理的余量是20%。即最后一个bit必须在从最后一个数据位bit到停止位bit的转换之前的至少20%的位周期被采样。

发送端设备的bit周期定义如下:

如果我们用E来表示接收端设备波特率与发送端设备波特率之间百分比差异的绝对值,那么接收端设备附加bit周期时间为:

对于第一次分析,我们将通过假设定时过程在起始位的正中间开始来简化。因此,对于一个8数据位接口,最后一个数据位将会偏离8ΔTRX:

前面提到的最后一个数据位的可接受采样窗口是从50%(理想值)到80%(接近我们愿意的),80% - 50%= 30%= 0.3 。

我们可以按照以下方式求解最大允许的E:

所以,基于这一简化的分析,只要发送端设备的波特率与接收端设备的波特率之间的差异小于3.75%,八数据位UART通信就应该是可靠的。

5.2 全面分析波特率最大允许误差

上一章节给出了一个经验法则,适用于任何能够容忍帧错误(即,指示停止位采样不正确的错误)的八数据位UART系统。在这一节中,我们将开发一个综合方程,可以提供更精确和定制的估计。

为此,我们将纳入以下几点:

1)起始位采样的位置变量

2)数据位数的变量

3)采样最终位的余量变量

4)奇偶校验位的存在或缺失

5)帧错误容忍度

根据上一章节分析:

现在我们的最终位采样余量是一个变量;我们将使用M(之前我们使用的是20%)。从下面的方程可以看出,M必须以小数形式输入,而不是百分比。

数据位的数量是一个变量,用N表示。我们还将包括一个用于奇偶校验位(P)和停止位(S)的变量。如果你有奇偶校验位,P使用1;如果没有,使用0。如果你想确保停止位被正确采样,S使用1;如果不确保,使用0。则公式更新为:

我们最后需要的是一个考虑起始位实际采样位置的变量。当前形式的方程假设为50%(即,比特周期的正中间)。这是理想位置。与理想位置的任何偏差都可能导致后续位的采样位置更接近过渡点(因此更接近错误)。我们添加以下项来将此纳入方程:

这项是指与理想的起始位采样位置的偏差,以小数形式表示并乘以接收设备的bit周期。例如,如果起始位在比特周期的60%处被采样,这项将是|(50% - 60%)|TRX = 0.1TRX。你不能直接确定这项的确切值,但如果你了解UART的低级功能细节,你可以提出一个合理最坏情况估计。

现在我们的方程是:

再考虑接收端设备的bit周期等于发送端设备的bit周期加上对应于误差百分比的额外时间,我们的最终方程如下:

计算示例

考虑以下几点:

1)最终位采样余量为30%

2)最坏情况下起始位采样偏差为5%

3)8个数据位

4)不允许有帧错误

5)使用奇偶校验位

带入到最终方程中:

1572

1572

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?