刷题推荐

链接: Verilog刷题

1,实验简介

通过LED流水灯实验,熟悉vivado软件开发FPGA的基本流程。包括器件选择、设置、代码的编写、编译、分配管脚、下载、程序FLASH固化烧录等。

2,实验环境

vivado 2019.1

黑金AX7035开发板

3,实验原理

3.1,LED硬件电路

从原理图可以看出,FPGA的IO输出低电平点亮LED,输出高电平LED熄灭。

4,程序设计

FPGA的设计中通常使用计数器来计时,对于50MHZ的系统时钟,一个时钟周期是20ns,那么表示1秒需要50_000_000个时钟周期。

4.1,vivado工程创建

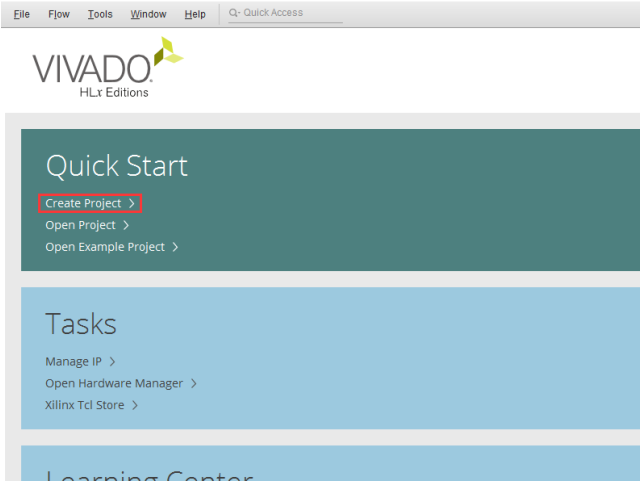

1,打开vivado,在IDE里双击Create Project,如下图:

2,弹出一个vivado的工程向导,点击Next;

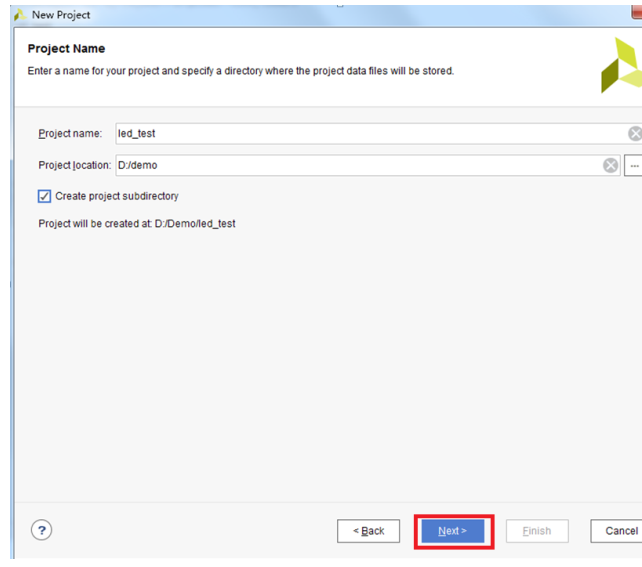

3,在弹出的对话框中输入工程名和工程存放的目录,工程可以选择自定义一个文件夹存放,这里取一个led_test的工程名,点击Next;

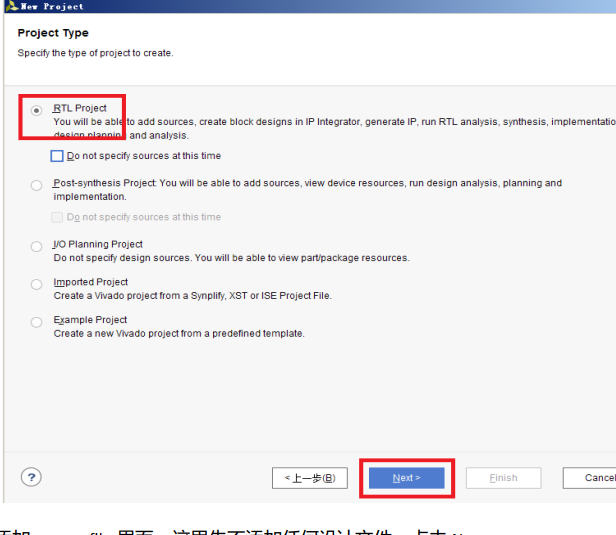

4,在下面的对话框中默认选择RTL Project,因为这里使用Verilog行为描述语言来编程。下面的Do not specify source at this time 的勾也可以打上。如果不打上,下一步会进入添加source file界面;

5,进入添加source file 界面,这里先不添加任何设计文件,点击Next;

6,提示是否添加已有的约束文件,这里约束文件也没有设计,所以不添加;

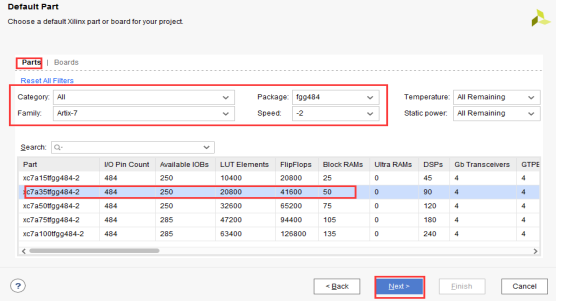

7,选择所用的FPGA器件,以及进行配置。首先在Family栏里选择Artix - 7,Speed grade栏选择-2,在Package栏选择fgg484,然后在下面列表中选择xc7a35tfgg484-2,单击Next;

8,再次确认板子型号是否正确,没有问题点击Finish完成工程创建。

4.2,编写流水灯的Verilog代码

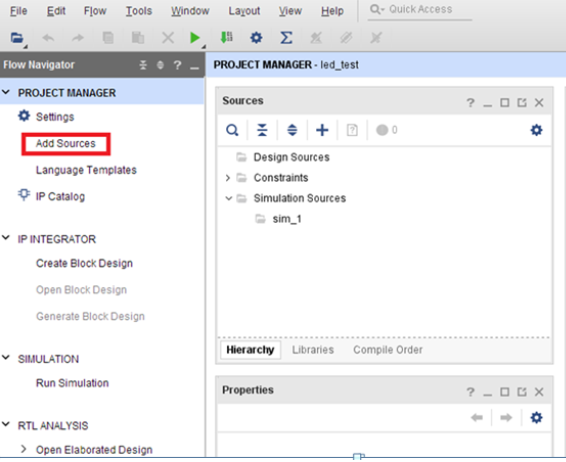

1,点击Project Manager下的Add Sources图标;

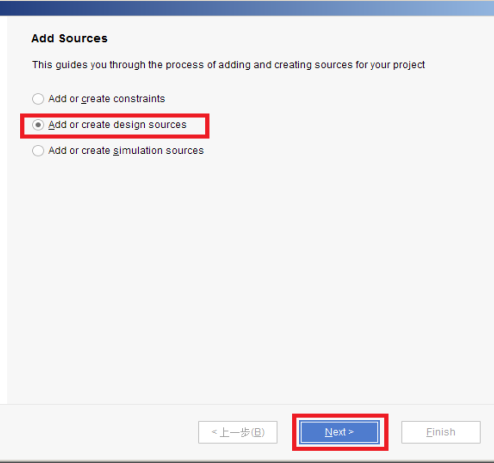

2,选择Add or create design sources,点击Next;

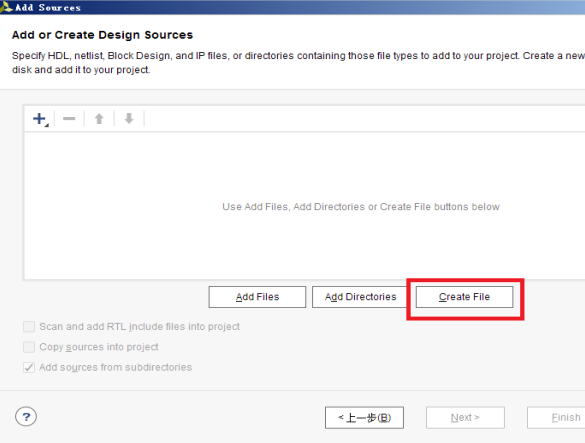

3,点击Add Files可以添加源文件,点击AddDirectories可以按目录添加源文件,因为还没设计程序,所以点击Create File按钮;

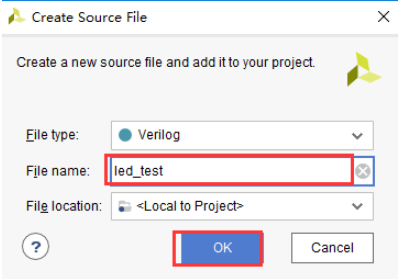

在弹出的对话框里选择File type是Verilog,File name是led_test,点击OK,点击Finish;

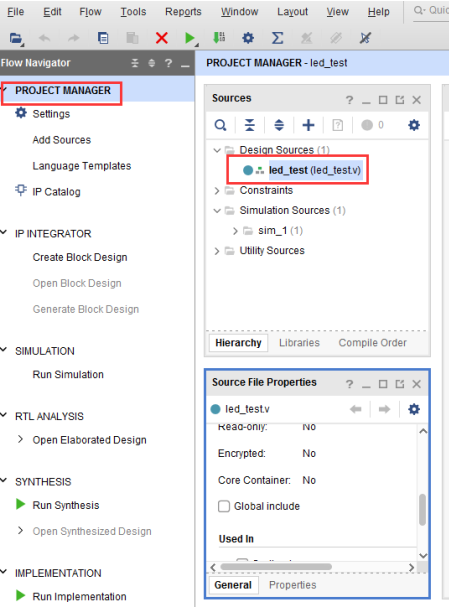

4,向导会提示定义I/O端口,可以在后面编写,单击OK,单击Yes。这时在Project Mannager界面下的Design Sources已经有了一个led_test.v文件,并自动成为项目的top模块;

5,编写代码,control+s保存好代码;

`timescale 1ns / 1ps

module LED_test

(

input sys_clk, //system clock 50MHZ on board

input rst_n, //reset low active

output [3:0] led //LED use of control the LED signal on board

);

reg [31:0] timer;

reg [3:0] led;

//==============================

/cle counter : from 0 to 4 sec

//==============================

always @(posedge sys_clk or posedge rst_n)

begin

if(~rst_n)

timer <= 32'd0; //when the reset signal valid,time counter clearing

else if(timer == 32'd199_999_999) //4 seconds count(50M * 4 - 1 = 199_999_999)

timer <= 32'd0; //count done,clearing the time counter

else

timer <= timer + 1'b1; //timer counter = timer counter + 1

end

//==============================

//LED control

//==============================

always @(posedge sys_clk or posedge rst_n)

begin

if(~rst_n)

led <= 4'b1111;

else if(timer == 32'd49_999_999)

led <= 4'b0111;

else if(timer == 32'd99_999_999)

led <= 4'b1011;

else if(timer == 32'd149_999_999)

led <= 4'b1101;

else if(timer == 32'd199_999_999)

led <= 4'b1110;

end

ila ila_inst

(

.clk(sys_clk),

.probe0(timer),

.probe1(led)

);

endmodule

4.3,添加XDC管脚约束文件

4.3.1,添加LED管脚约束

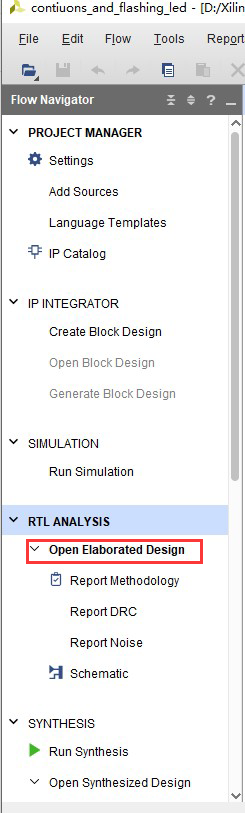

1,点击RTL Analysis下的Open Elaboratred Design图标;

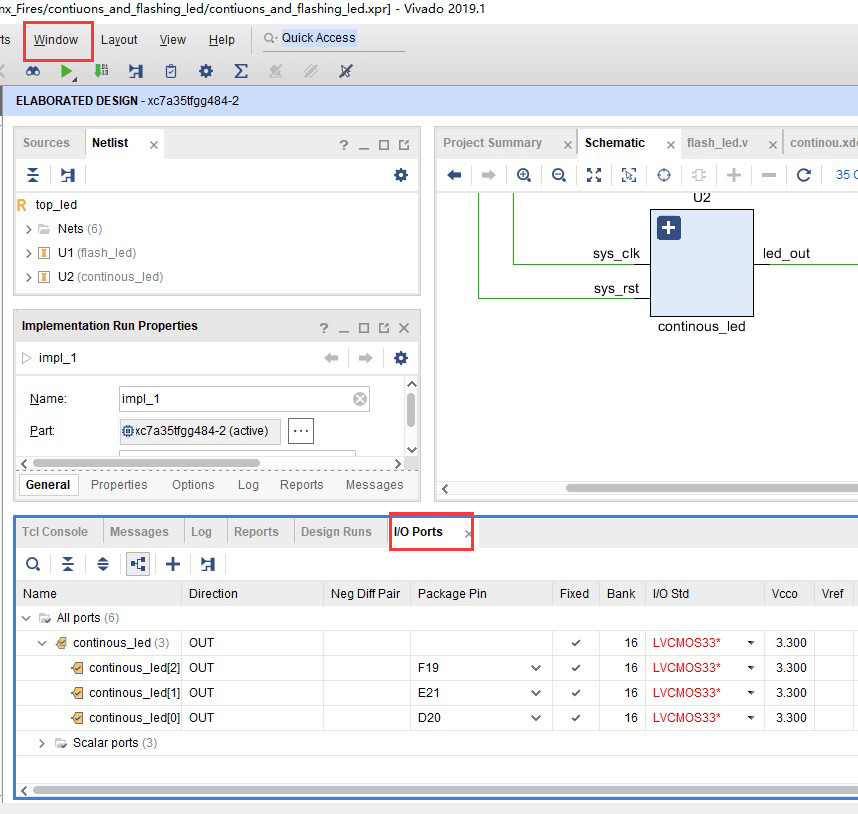

2,在I/O Ports添加I/O口和时钟、复位口的引脚,如果在栏目找不到,到菜单栏单击Window,选择I/O Ports。将原理图的I/O写入,复位引脚在这里默认低电平复位,将I/O口用一个按键替代即可;

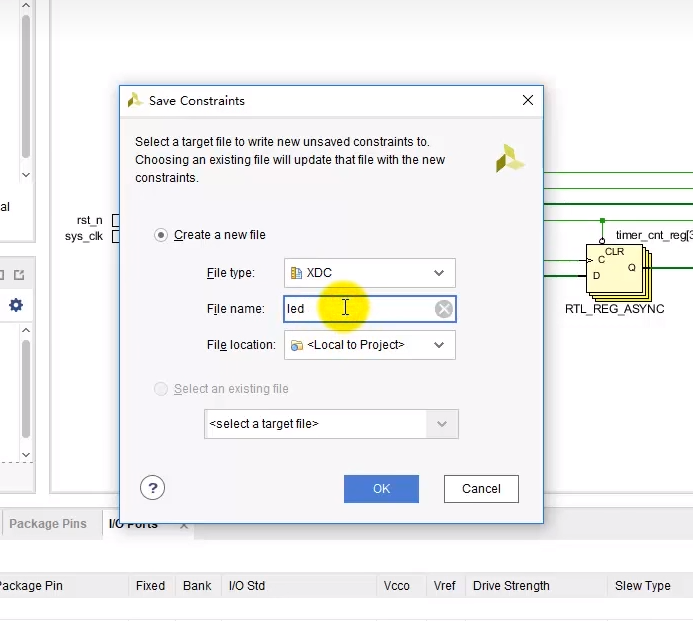

3,control+s保存,在弹出的向导里File type 默认是XDC,Project name自定义,在这里是led,单击OK;

4.3.2,添加时钟约束

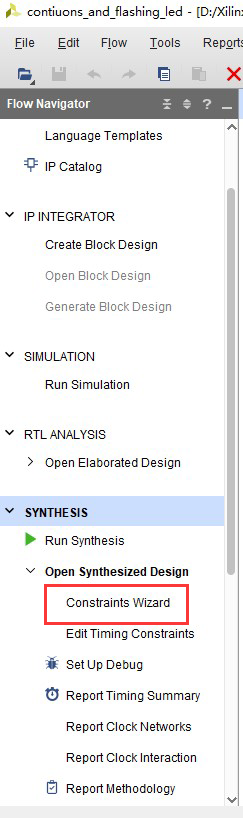

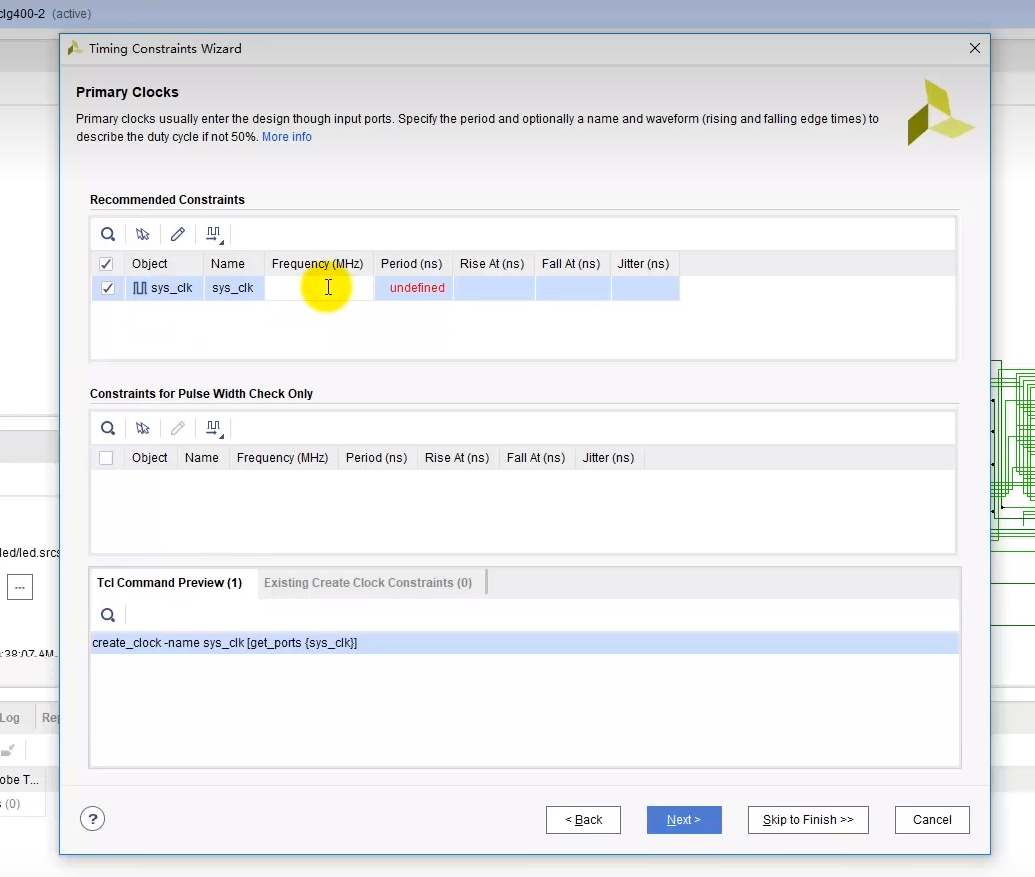

1,点击Synthesis下的Open Synthesized Design图标,选择Constranits Wizard,点击Next;

2,在Frequency栏下输入50,点击Skip to Finish,点击Finish;

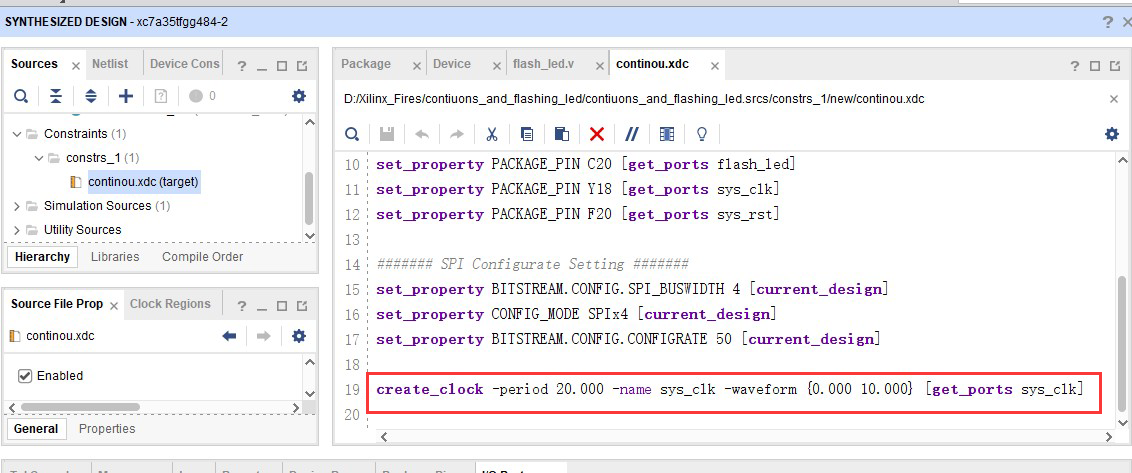

3,打开xdc文件,会出现约束语句。

4.4,vivado仿真验证

可以用vivado自带的仿真工具来验证流水灯程序的结果

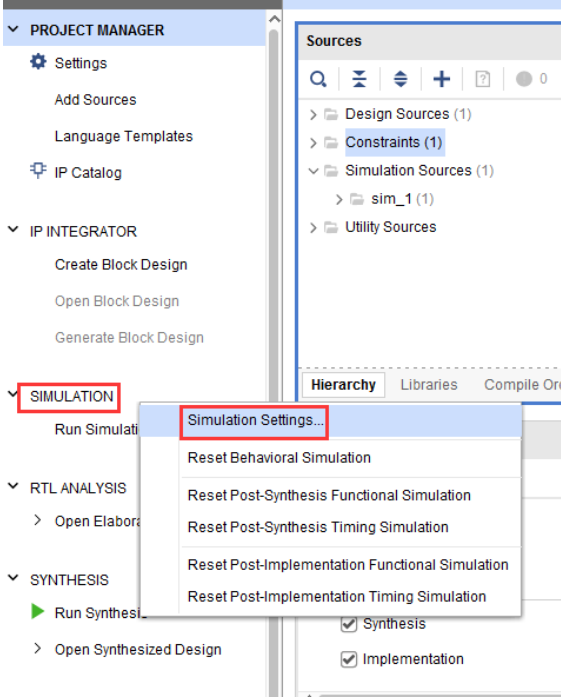

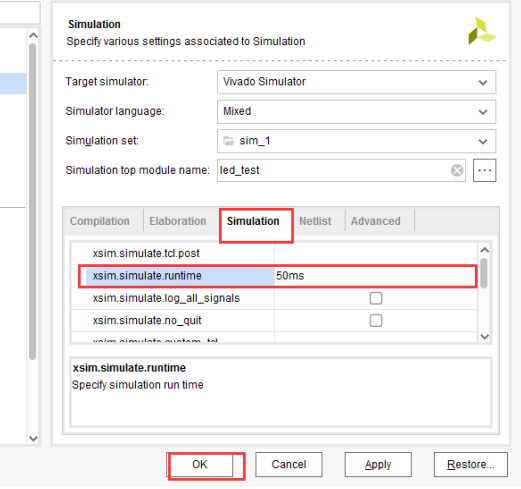

1,设置vivado的仿真配置,右击SIMULATION 中的Simulation Settings;

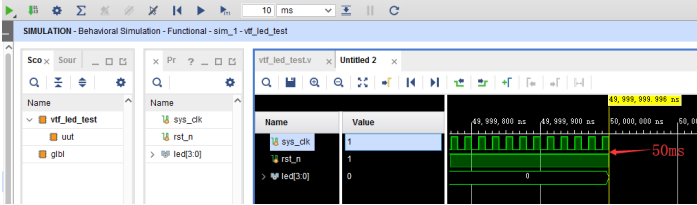

2,设置成需要的仿真时间,这里设置成50ms,单击OK;

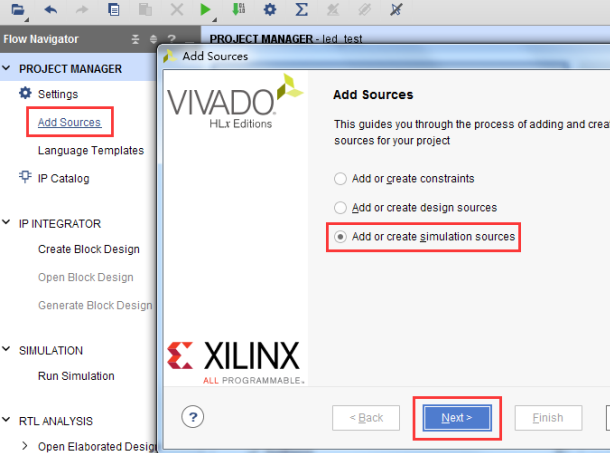

3,添加激励测试文件,点击Project Manager下的Add Sources图标;

4,选择Add or create simulation sources,点击Next;

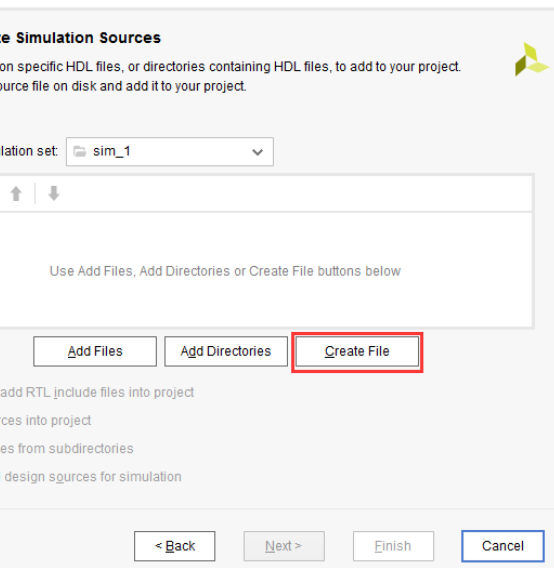

5,点击Create File生成仿真激励文件;

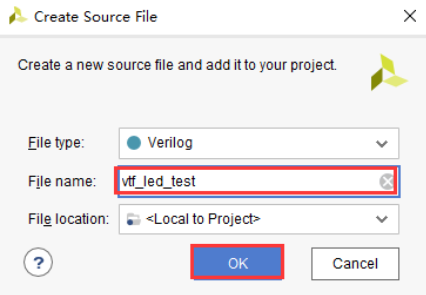

在弹出的对话框中输入激励文件的名字,这里为vtf_led_test,点击Finish,点击OK,点击Yes;

6,编写仿真程序,control+s保存好代码;

`timescale 1ns / 1ps

module vtf_LED_test;

reg sys_clk;

reg rst_n;

wire [3:0] led;

LED_test uut

(

.sys_clk(sys_clk),

.rst_n(rst_n),

.led(led)

);

initial begin

sys_clk = 0;

rst_n = 0;

#1000;

rst_n = 1;

#20000;

end

always #10 sys_clk = ~sys_clk;

endmodule

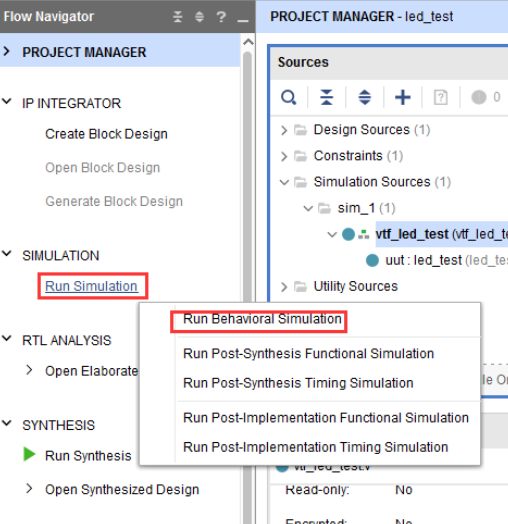

7,点击Run Simulation,再选择Run Behavioral Simulation,这里做一下行为级的仿真;

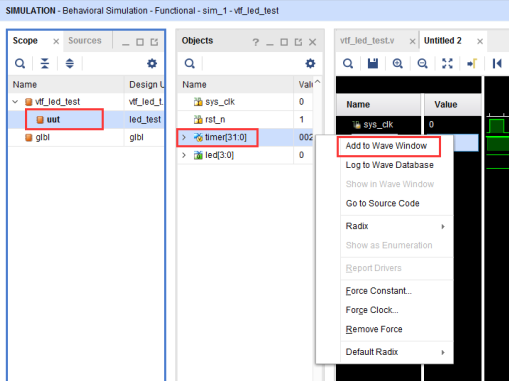

8,在弹出的仿真界面中可以选择双击uut,将timer拖动到Wave中观测timer的波形;

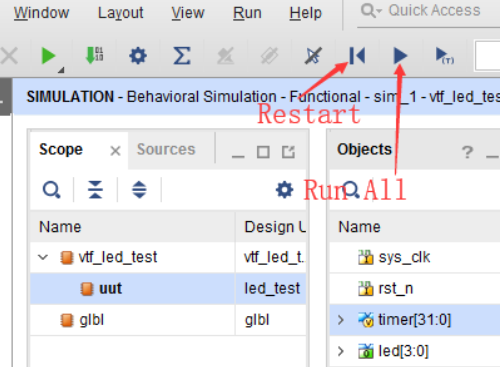

9,点击图标Restart复位一下,再点击Run All,可以看到仿真波形与设计相符;

4.5,下载和Flash固化

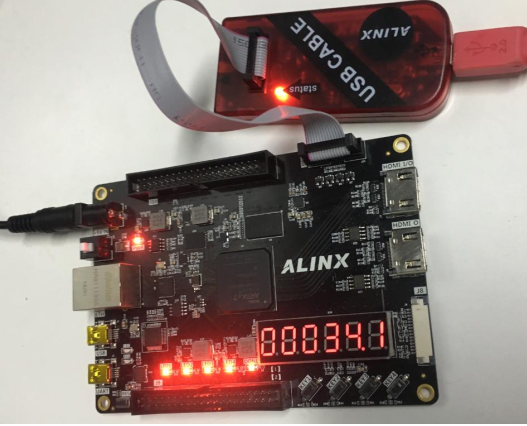

经过前面的编译和仿真,我们可以把bit文件下载到FPGA芯片中,看一下实际运行效果,下载程序之前先连接硬件,JTAG和开发板连接,开发板连接电源上电。

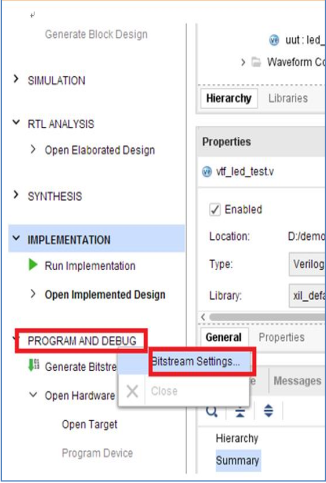

1,右击PROGRAM AND DEBUG ,单击Bitstream Setting;

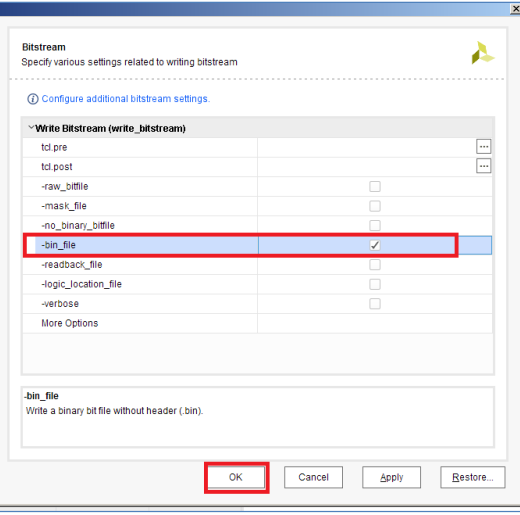

2,选择生成bin文件,点击OK,生成的bin文件在后面固化程序到Flash中会用到;

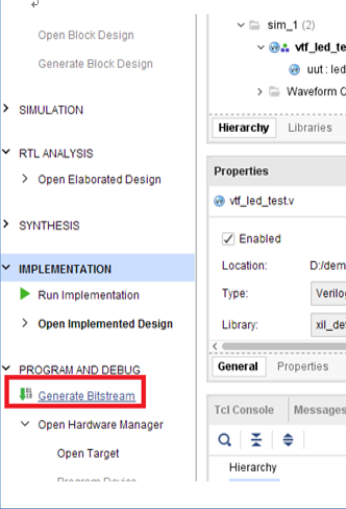

3,单击Generate Bitstream生成bit和bin文件;

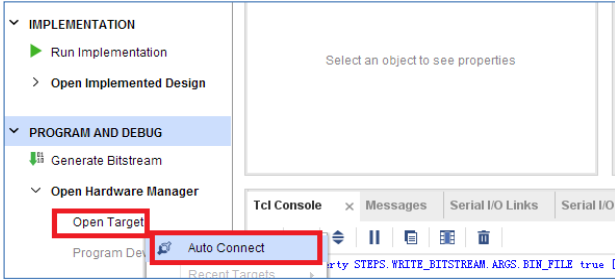

4,点击Open Hardware Manager,点击Open Target->Auto Councet,在hardware界面下会显示xc7a35t_0图标,说明JTAG连接成功;

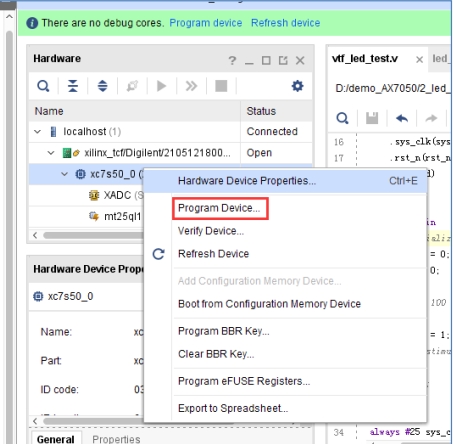

5,右键xc7a35t_0,选择Program Device,选择led_test生成的bit文件,点击Program烧写FPGA【掉电程序丢失】

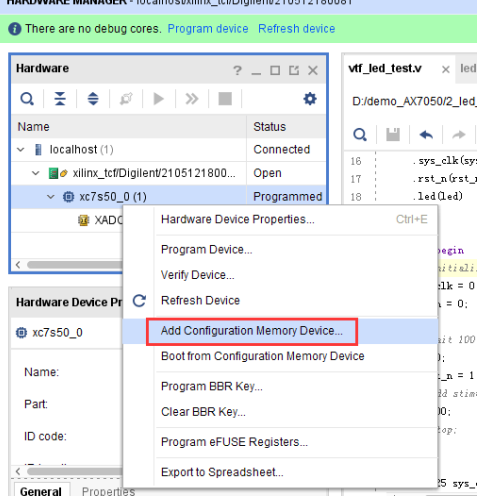

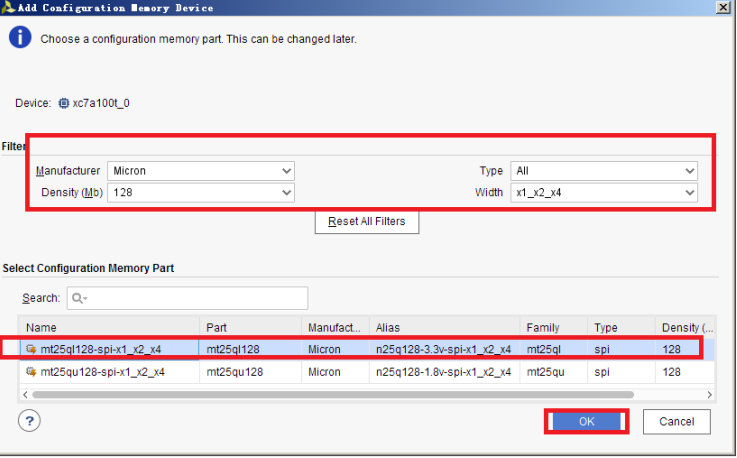

6,右键xc7a35t_0,选择Add Configruation Memory Device,在弹出的对话框选择正确的FLASH型号,点击OK【掉电程序不丢失】;

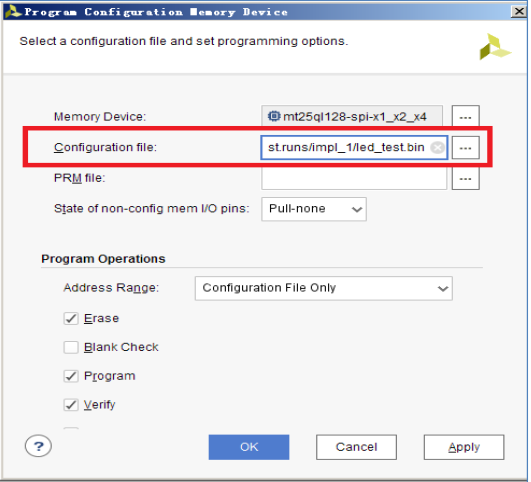

7,提示是否对SPI FLASH进行编程,点击OK,在弹出的窗口中,Configration file选择vivado生成的bin文件【文件默认在imp1_1目录下】,点击OK;

8,想加快上电后程序启动,可以在xdc文件添加以下几行代码,目的是为了提高SPI FLASH的读写时钟,其中前面两条设置QSPI FLASH的数据宽度和配置模式,后面一条是配置速度,这个值越大,速度越快。修改好的xdc文件需要重新编译,再次重新生成bit和bin文件。

set_property BITSTREAM.CONFIG.SPI_BUSWIDTH 4 [current_design]

set_property CONFIG_MODE SPIx4 [current_design]

set_property BITSTREAM.CONFIG.CONFIGRATE 50 [current_design]

1168

1168

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?