基于平台:stm32f407ZGT6开发板

STM32–DMA

一、DMA简介

DMA是什么

DMA,全称为:Direct Memory Access,即直接存储器访问。其主要功能作用是用于数据传输并且不占用CPU。

DMA传输数据功能很强、很高效。为什么说DMA传输数据是高效的呢?这是因为DMA在传输实现高速数据移动过程无需任何 CPU 操作控制;DMA 传输方式无需 CPU 直接控制传输,也没有中断处理方式那样保留现场和恢复现场的过程,通过硬件为 RAM 与 I/O 设备开辟一条直接传送数据的通路,能使 CPU 的效率大为提高。

在STM32 最多有 2 个 DMA 控制器。DMA1 有 7 个通道。DMA2 有 5个通道。每个通道专门用来管理来自于一个或多个外设对存储器访问的请求。还有一个仲裁起来协调各个 DMA 请求的优先权。

二、DMA功能框图

在STM32F4系列的DMA可以实现外设寄存器与存储器之间或者存储器与存储器之间传输三种模式,这要得益于 DMA 控制器是采样 AHB 主总线的,可以控制 AHB 总线矩阵来启动 AHB 事务。

在功能框图上划分为六个部分:

●通道+流

●仲裁器

●FIFO

●存储器接口

●外设接口

●编程接口

在stm32编程上主要涉及到前面三部分,后面三大部分在本文就不多大费周章分析、讲解了。了解一下就可以了。

●通道+流

流:是数据传输的一条链路,每个DMA控制器有8条独立的数据流,每次传输的数据量最大为65535,如果数据的单位为字的话,那一次可以传输256KB。

通道:每个数据流有8个通道选择,每个通道对应不同的DMA请求。

部分DMA1通道的请求映像:

在DMA里每个外设请求都占用一个数据流通道,相同外设请求可以占用不同数据流通道。

●仲裁器

根据这个“仲裁器”的名字我们就可以大概推测出他的主要作用——仲裁。

我们已经知道了一个 DMA 控制器对应8个数据流数据流包含要传输数据的源地址、目标地址、数据等等信息。当我们只有一个外设请求时,就不需要使用到仲裁器,但与之相反如果我们需要同时使用同一个DMA 控制器多个外设请求时,那必然需要同时使用多个数据流,这时候就需要我们的仲裁器来判断让哪一个数据流优先的传输。

在这里我们分为软件阶段和硬件阶段:

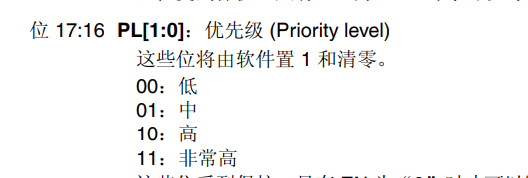

1、软件阶段上主要由寄存器DMA_SxCR的PL位进行优先级的控制。即:

2、硬件阶段,数据流编号小的优先级大。

●FIFO

FIFO是源和目标之间的一个数据中转站。

每个数据流都独立拥有四级 32 位 FIFO(先进先出存储器缓冲区)。DMA 传输具有 FIFO 模式和直接模式。

直接模式在每个外设请求都立即启动对存储器传输。在直接模式下,如果 DMA 配置为存储器到外设传输那DMA会见一个数据存放在 FIFO 内,如果外设启动 DMA 传输请求就可以马上将数据传输过去。

FIFO 用于在源数据传输到目标地址之前临时存放这些数据。可以通过 DMA 数据流xFIFO控制寄存器DMA_SxFCR的FTH[1:0]位来控制FIFO的阈值,分别为 1/4、1/2、3/4 和满。如果数据存储量达到阈值级别时,FIFO 内容将传输到目标中。

FIFO 对于要求源地址和目标地址数据宽度不同时非常有用,比如源数据是源源不断的字节数据,而目标地址要求输出字宽度的数据,即在实现数据传输时同时把原来 4 个 8 位字节的数据拼凑成一个 32 位字数据。此时使用 FIFO 功能先把数据缓存起来,分别根据需要输出数据。

FIFO另外一个作用使用于突发 (burst) 传输。

工作模式

上文介绍了DMA在stm32f4系列的三种工作模式:

●外设到存储器

●存储器到外设

●存储器到存储器

●外设到存储器

使能这种模式时,每次产生外设请求,数据流都 会启动数据源到 FIFO 的传输。达到 FIFO 的阈值级别时,FIFO 的内容移出并存储到目标中。

如果DMA_SxNDTR 寄存器达到零、外设请求传输终止(在使用外设流控制器的情况下)或DMA_SxCR 寄存器中的 EN 位由软件清零,传输即会停止。

在直接模式下,不使用 FIFO 的阈值。

级别控制:每完成一次从外设到 FIFO 的数据传输后,相应的数据立即就会移出并存储到目 标中。

●存储器到外设

使能这种模式时,数据流会立即启动传输,从源完 全填充 FIFO。

每次发生外设请求,FIFO 的内容都会移出并存储到目标中。当 FIFO 的级别小于或等于预定 义的阈值级别时,将使用存储器中的数据完全重载 FIFO。

如果DMA_SxNDTR 寄存器达到零、外设请求传输终止(在使用外设流控制器的情况下)或DMA_SxCR 寄存器中的 EN 位由软件清零,传输即会停止。

在直接模式下,不使用 FIFO 的阈值级 别。一旦使能了数据流,DMA 便会预装载第一个数据,将其传输到内部 FIFO。一旦外设请 求数据传输,DMA 便会将预装载的值传输到配置的目标。然后,它会使用要传输的下一个数据再次重载内部空 FIFO。预装载的数据大小为DMA_SxCR 寄存器中 PSIZE 位字段的值。

●存储器到存储器

DMA 通道在没有外设请求触发的情况下同样可以工作。

通过将DMA_SxCR 寄存器中的使能位 (EN) 置 1 来使能数据流时,数据流会立即开始填充FIFO,直至达到阈值级别。达到阈值级别后,FIFO 的内容便会移出,并存储到目标中。

如果DMA_SxNDTR 寄存器达到零或DMA_SxCR 寄存器中的 EN 位由软件清零,传输即会停止。

315

315

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?