更新日期:2024/07/22

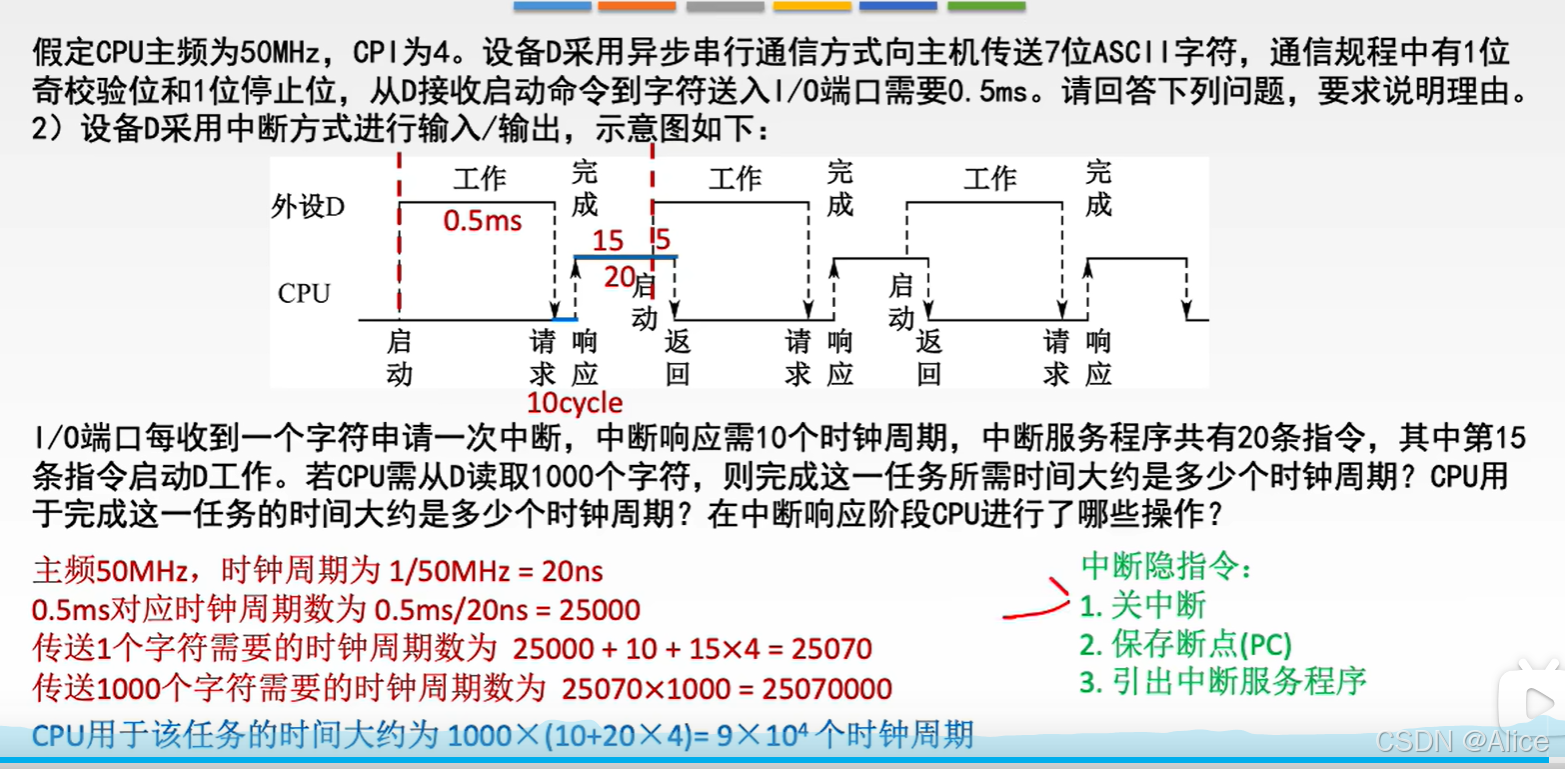

0. 前言

准备2024年12月考研,考408~~

我觉得总结,内化并输出,才表示学习到位了。所以总结了这门课的内容,记录的原则是:

- 根据考研大纲(2025年大纲还没发布 ,参考2024大纲)和王道书范围;

- 对我来说不算做重点或难点的章节,简单概括;

- 对我来说属于难点或重点的章节,详细记录,需要时举例说明。

- 历年真题,页码和题号均来自王道复习指导2025版

1. 计算机系统概述

2015-2023年共考察单选题15题,涉及大题2道。

1.1 计算机系统层次结构

1.1.1 冯·诺依曼计算机结构

思想:存储程序。指令和数据以二进制形式存储在存储器中,计算机按照存储器中的指令序列自动执行程序。

特点:

指令和数据以同等地位存储在存储器中,并可按地址寻访。

指令和数据均用二进制代码表示,指令由操作码和地址码组成。

以运算器为中心,现代计算机已发展为以存储器为中心。

1.1.2 计算机硬件

输入设备;输出设备

存储器:分为主存储器(内存)和辅助存储器(外存)。主存储器CPU能直接访问,辅助存储器信息需调入主存后才能被CPU访问。

MAR地址寄存器用于寻址,其位数反应了主存的容量。

MDR数据寄存器,位数通常等于存储字长。

MAR和MDR在现代计算机中在CPU中。

运算器:执行算术和逻辑运算的部件,核心是算术逻辑单元(ALU)。

控制器:计算机的指挥中心,包含程序计数器(PC)、指令寄存器(IR)和控制单元(CU)。

一般将运算器和控制器集成到同一个芯片上,称为中央处理器(CPU)。

1.1.3 计算机软件

系统软件:如操作系统、数据库管理系统、语言处理系统等,负责管理和控制计算机的硬件和软件资源。

应用软件:为解决特定问题而编写的程序,如科学计算、工程设计等。

三个级别的语言

机器语言:计算机唯一能直接识别和执行的语言,由二进制代码组成。

汇编语言:用英文单词或其缩写代替二进制指令代码,需通过汇编程序转换为机器语言执行。

高级语言:如C、C++、Java等,方便程序员编写,需通过编译或解释转换为机器语言执行。

翻译程序:

1)汇编程序(汇编器)。汇编语言 -> 机器语言

2)解释程序(解释器)。将源程序中的语句按执行顺序逐条翻译成机器指令并立即执行。

3)编译程序(编译器)。高级语言 -> 汇编语言或机器语言程序

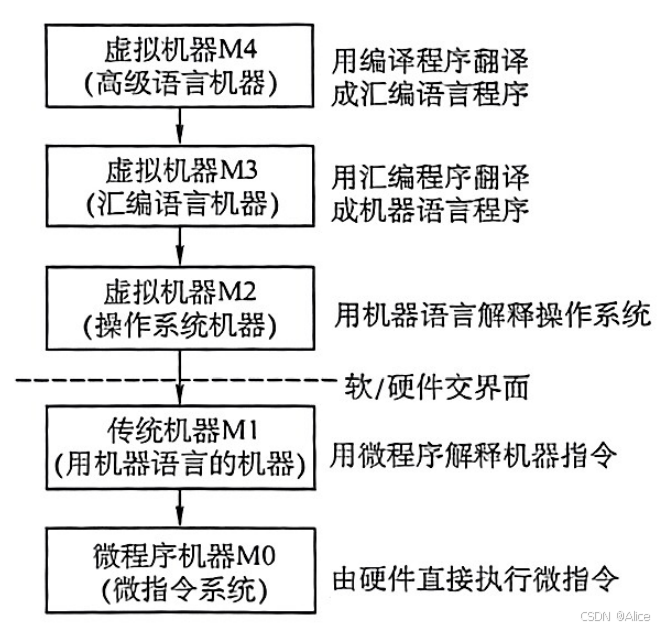

1.1.4 层次结构

没有配备软件的纯硬件系统称裸机。

第3层~第5层称为虚拟机,简单来说就是软件实现的机器。虚拟机器只对该层的观察者存在。

1.1.5 计算机系统的工作原理

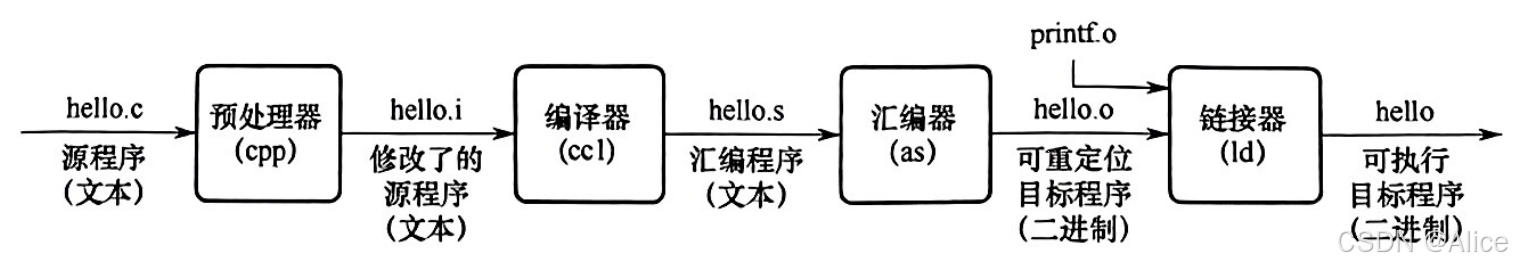

从源程序到可执行文件

预处理:预处理器对源程序进行初步处理,如宏定义展开、条件编译等,生成的文件通常以 i 为扩展名。

编译:编译器(ccl)将预处理后的文件转换成汇编语言源程序。汇编语言是一种低级语言,每条语句都对应一条机器指令,但更接近人类语言。

汇编:汇编器将汇编语言源程序翻译成机器语言指令,并将这些指令打包成可重定位目标文件(通常以.o为扩展名)。这是一个二进制文件,包含程序的机器码和数据。

链接:链接器(如ld)将多个可重定位目标文件以及标准库函数合并成一个可执行文件。链接过程中,链接器会解决外部符号引用,即将程序中引用的库函数或全局变量与实际的函数或变量地址关联起来。

1.2 计算机的性能指标

1.2.1 系统整体性能指标

机器字长:计算机进行运算所能处理的二进制数据的位数,如32位、64位等。字长一般等于通用寄存器的位数或 ALU的宽度。

数据通路带宽:数据总线一次能并行传送的信息的位数。

主存容量:存储器的容量由MAR(存储地址寄存器)的位数和MDR(存储数据寄存器)的位数共同决定。例如,MAR有32位,MDR有8位,则总容量=2^32 * 2^3 = 32*2^30 = 32GB(需注意实际容量可能小于理论值)。

1.2.2 运算速度

吞吐量: 指系统在单位时间内处理请求的数量。它取决于信息能多快地输入内存,CPU 能

多快地取指令,数据能多快地从内存取出或存入,以及所得结果能多快地从内存送给一台

外部设备。几乎每步都关系到主存储器,因此系统吞吐量主要取决于主存储器的存取周期。

响应时间:从用户向计算机发送一个请求,到系统产生响应并获得所需结果之间的时间。

CPU时钟周期:CPU中最小的时间单位,通常为主频的倒数,即每个脉冲的周期。

CPU主频(时钟频率):CPU内部主时钟的频率,表示CPU内数字脉冲信号振荡的频率,通常以GHz为单位。就是每秒有多少个时钟周期。

CPI(Clock Cycle Per Instruction):执行一条指令所需的时钟周期数。相同指令在不同情况下的CPI可能不同。

IPS(Instructions Per Second):每秒执行的指令数。IPS=主频/平均 CPI。

CPU执行时间: CPU执行周期数 / 主频 = (指令条数 * CPI) / 主频。

FLOPS(Floating-point Operations Per Second):每秒执行的浮点运算次数。

常用的单位有: Mg.TopEasy, M=10^6, 每个等级 +3

- MFLOPS 百万 10^6

- GFLOPS 十亿 10^9

- TFLOPS 万亿 10^12

- PFLOPS 千万亿 10^15

- EFLOPS 京 = 一亿亿 10^18

- ZFLOPS 十万京 10&21

1.3.3 数量的表示

描述速率/频率时,KMGT 通常用10为底的幂次表示,如1kb/s = 10^3 b/s。见上节。

在描述存储容量时,KMGT 通常用2为底的幂次表示,如1Kb = 2^10 b。

- K(Kilo,千)通常表示2^10 ,即1024

- M(Mega,兆)表示2^20

- G(Giga,吉)表示2^30

- T(Tera,太)表示2^40

1.3 专业术语

系列机:具有基本相同的体系结构,使用相同的基本指令体系的多个不同型号的计算机组成的一个产品系列。

固件 :将程序固定在ROM上,即具有软件特性的硬件。

1.4 常见问题

主频高的 CPU一定比主频低的 CPU快吗?

衡量 CPU运算速度的指标有很多,不能以单独的某个指标来判断 CPU的好坏。

基准程序执行得越快说明机器的性能越好吗?

一般情况下,基准测试程序能够反映机器性能的好坏。但是,由于基准程序中的语句存在频度的差异,因此运行结果并不能完全说明问题。

2. 数据的表示和运算

2015-2023年共考察单选题27题,涉及大题13道。

2.1 数制与编码

2.1.1 进位计数制及其相互转换

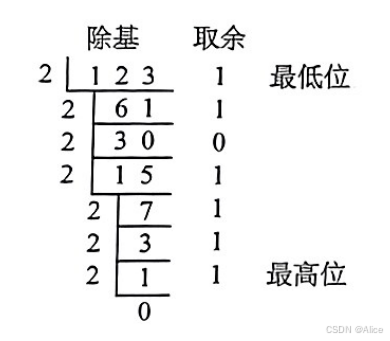

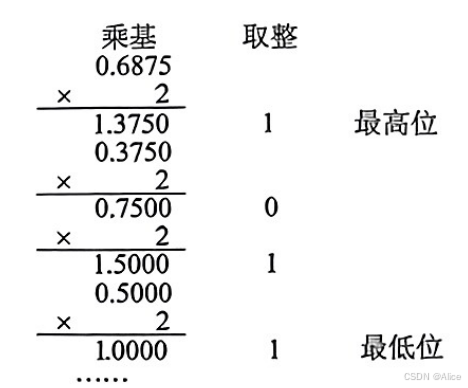

二进制 B,八进制 O,十进制 D,十六进制 H 或 0x

二进制数转换为八进制和十六进制数:以小数点为界,向左和右按3或4位一组(不足补齐)转换。

任意进制数转换为十进制数:按权展开相加。

十进制数转换为任意进制数:整数部分采用基数乘除法,小数部分采用乘基取余法,拼接。

注意:并不是每个十进制小数都可以准确的用二进制表达,比如0.3。

2.1.2 定点数的编码表示

真值:带正负号的数称为真值;

机器数:将符号一起编码了数字化的数称为机器数。0正1负。

根据小数点的位置是否固定,在计算机中有两种数据格式:定点表示和浮点表示。

在现代计算机中,通常用补码整数表示整数,用原码小数表示浮点数的尾数部分,用移码表示浮点数的阶码部分。

定点小数:纯小数,约定小数点位置在符号位之后、有效数值部分最高位之前。

定点整数:纯整数,约定小数点位置在有效数值部分最低位之后。

计算机内部并没有小数点~

定点数的编码表示法主要有4种:原码、补码、反码和移码。

真值 原码 反码 补码 移码

+23 0001 0111 - 0001 0111 - 0001 0111 - 1001 0111

-23 1001 0111 - 1110 1000 - 1110 1001 - 0110 1001

正数 - 原反补相同,移码是将符号位取反。(当偏置值不是2^n时,比如表示浮点数的阶时,移码就不是这样计算了)。

负数 - 原码的最高位为1(表示符号);反码最高位为1,其余位是原码按位取反;补码是反码加1;移码是将补码的符号位取反(当偏置值不是2^n的时候,比如表示浮点数的阶时,移码就不是这样计算了)。

原码

表示范围关于原点对称,字长为n+1时表示范围 -(2^n - 1)<= x <= 2^n - 1。

优点:与真值对应关系简单,实现乘除比较简单。

缺点:0的表示不唯一(正0和负0),加减法运算比较复杂。

反码:主要用于补码计算的中间步骤,不直接用于表示数值或进行运算。

补码:

0的表示唯一,因此表示范围比原码多一个数(-2^n)。字长为n+1时表示范围 -2^n <= x <= 2^n - 1。

优点:能够简化计算机的运算过程(特别是将减法转换为加法),因此广泛应用于计算机内部的整数表示和运算中。

变形补码 (模4补码)- 采用双符号位,00表示正,11表示负。

移码:

只能表示整数。

主要用于浮点数的阶码表示。

0的表示唯一,因此表示范围比原码多一个数。

实质就是在真值的基础上加一个常量(偏置值),相当于把数字在X轴上偏移了若干单位,=保持了数据原有的大小顺序。移码越大,真值就越大。

2.1.3 整数的表示

无符号整数

因为不需要一位表示符号,字长相等情况下,表示范围比有符号整数大。

可应用在地址运算中。

有符号整数

计算机中的有符号整数都用补码表示!

字长为n+1时表示范围 -2^n <= x <= 2^n - 1

2.1.4 C语言中整数类型及类型转换

char 8 bit (默认为无符号整数), short / short int 16 bit, int 32 bit, long or long int 32 or 64 bit

short/int/long 不指定 signed/unsigned 时默认有符号 。

C语言进行强制类型转换后,并不改变操作数本身,改变的是解读方式。比如,无符号数或CHAR转换为有符号数,原来机器数的第一位数值就被解读为符号;大字长转换为小字长,高位被截除,保留低位。

零扩展和符号扩展 - 小字长转换为大字长时,无符号整数高位用0补足,有符号数高位用原数的符号位填充(是补码,填充后值和原值一样)。

C语言中无符号数和有符号数参加运算,规定按无符号数运算。

2.2 运算方法和运算电路

2.2.1 基本运算部件

运算器的组成 - ALU 算数逻辑单元,移位器,PSW 状态寄存器,通用寄存器。

运算器的基本功能 - 加减乘除;与或非,异或等逻辑运算;移位,求补等。

ALU的额核心部件是加法器。

带标志(Flag)加法器

SF - Sign 符号,对于无符号数没有意义。

OF - Overflow 溢出标志,仅对有符号数有效,是符号位进位和数值最高位进位的异或。

CF - Carry 进位/借位,判溢出,仅对无符号数有效。加法时有进位,表明位数不够用,发生溢出;减法时需要借位,说明不够减,发生溢出(溢出了可处理的范围)。

ZF = 1,表示结果为 Zero 零。

逻辑算数单元(ALU)

因为加减乘除最终都能归结为加法,因此ALU的核心是带标志加法器,它同时也能执行与或非操作。

AB是操作数输入端。ALUop是操作控制端(发出控制信号),决定ALU执行的功能。ALUop的位数决定了操作的总类,如2位最多可以产生4种控制信号。

下图右图是一位ALU结构图,可以完成与或非和加法。

2.2.2 定点数的移位运算

当计算机中没有乘除运算电路时,可以通过加法和移位相机和来实现乘除运算。

左移一位,若不产生溢出,相当于乘以2。

右移一位,若不考虑因移出而舍弃的末尾小数,相当于除以2。

逻辑移位 - 不管符号位,左移右移后两边都直接补0。

算数移位 - 将操作数视为有符号数。因有符号数都是补码表示的,左移时,高位移出,低位补0,若移动后的高位符号和原来的不同,即发生了溢出。右移时,低位移出,高位补符号位,可能会影响精度。

2.2.3 定点数的加减运算

补码运算

加法直接加,减法转换为加法,2-3 = 2+(-3)。

符号位参与运算,结果的符号位会直接体现出来。

运算结果如有进位,丢弃。

溢出判别

思想:仅当两个符号相同的数相加(例如两个正数相加,结果符号位为1),或两个符号不同的数相减(负数减去整数,结果符号 为0),才有可能溢出。

采用一位符号法 - 由于都是转换成加法运算的,仅需判断两个操作数同号时,结果符号是否与之不同。V=0无溢出。

采用双符号位(模4补码) - 运算结果的两个符号位不同,判定为溢出,高位符号是正确的。

采用一位符号位根据数值位的进位情况判断,若符号位(最高位)的进位和数值最高位(次高位)的进位不一致,则为溢出。V=0无溢出。

加减运算电路

无符号数与有符号数加/减运算能用同一个加法器实现的理由(2011)

一个数的补码表示为Y,则这个数的负数的补码为Y补+1,为了实现将Y转换为Y补+1,在原加法器的Y输入端加 n 个反向器以实现各位取反的功能,然后加一个2选1多路选择器,用一个控制端 Sub来控制,以选择是将Y输入加法器还是将Y补输入加法器,并将Sub同时作为低位进位送到加法器(做减法时实现末位加1),做加法时输入0。该电路可实现模2"补码加减运算。

即当Sub为1时,做减法,实现X+Y补+1=[x]补+[-Y]补; 当Sub为0时,做加法,实现 X+ Y =[x]补+ [y]补。

2.2.4 定点乘法运算

乘法运算的基本原理 - 用加法移位指令实现,原码乘法步骤:

①乘积的符号位由两个乘数的符号位“异或”得到;

②乘积的数值位是两个乘数的绝对值之积。两个n为无符号数相乘共需进行n次加法和n次移位运算。部分积 Pi 是乘法运算的中间结果,初值 P0=0。从乘数的最低位开始,将前面所得的部分积加上,然后右移一位,此步骤重复n次。

由于参与运算的是两个数的数值位,因此运算过程中的右移操作均为逻辑右移。

乘法运算电路

乘法指令的溢出判断 - 在字长为 32 位的计算机中,对于两个 int 型变量x和y的乘积,若乘积高 32 位的每一位都相同(例如1111或0000),且都等于低32位的符号位,则表示不溢出(注意是是补码表示)。

2.2.5 定点除法运算

除法运算的基本原理

原码的除法运算与乘法运算很相似,都是移位和加减运算迭代的过程,但比乘法更复杂。

n位定点数的除法运算,需统一为一个 2n 位的数除以一个n位的数,得到一个n位的商,因此需要对被除数进行扩展。

商的符号位是两个数的符号位的“异或”结果,商的数值位是两个数的绝对值之商。

原码除法过程

① 被除数与除数相减,够减则上商为 1,不够减则上商为 0。

②每次得到差为中间余数,将除数右移后与上次的中间余数比较。用中间余数减除数,够减则上商为1,不够减则上商为0。如此重复,直到商的位数满足要求为止。

除法运算电路

2.3 浮点数的表示与运算

2.3.1 浮点数的表示

N = (-1)^S * M * R^E

S 符号位

M 尾数,定点小数,一般用原码表示

E 指数(阶码),定点整数,移码(偏置值 2^(n-1) - 1)

R 基数

正/负 上溢 - 需中断运算,进行溢出处理

正/负 下溢 - 当作机器零处理

浮点数的规格化 (左规/右规)- 为了尽可能多的保留有效数字,使尾数和阶码的最高位是有效值。

IEEE 754标准

基数 - 隐含为2。

尾数- 是原码且位数最高位的1隐藏(因为总是1),隐藏的一位的位置在小数点之前。

移码 - 偏置值 2^(n-1) - 1,和标准的移码(偏置值 2^(n-1) ,即补码+1)不一样!!!

阶码全为0或1时,特别的解释:

尾数为0,阶码为0,表达正负0。

尾数为0,阶码为1,表达正负无穷大。引入无穷大的目的是,计算出现异常后程序仍能进行。

尾数不为0(高位有一个或几个连续的零,即隐藏位为0),阶码为0,表达非规格化的数,即比规格化能表示的数还要小的数。可以用来处理下溢。

尾数不为0,阶码为1,表达“非数”,没有定义的数,NaN (not a number)。

2.3.2 浮点数的加减运算

对阶:小阶 -> 大阶

尾数加减:原码,定点小数相加。注意:有一位隐藏的尾数!

尾数规格化:左规/右规

舍入:为了保证精度 ,一般移出的低位保留下来,参加运算,最后再将运算结果进行舍入。就近舍入(0舍1入);正向舍入(正无穷的方向舍入);负向舍入;截断法。

溢出判断:如尾数溢出,调整尾数 和阶码;如阶码溢出,可能发生上溢或下溢。

2.3.3 C语言中的浮点数类型(略)

2.3.4 数据的大小端和对齐存储

表示数据的低位和高位:LSB表示最低有效字节;MSB表示最高有效字节。

大端方式:适合于人类观看的模式,即从左至右存储。每个地址存放一个字节 。

小端方式:机器方便识别的模式,从右至左按字节存储。

数据数据“边界对齐”方式存储

C语言中struct类型中边界对齐的要求:

1) 每个成员按其类型的大小对齐;

2)struct的总长度必须是成员中最大对齐值的整数倍。比如第一个成员占1字节,第二个成员占4字节,第二个成员的起始位置必须是第5个空位位置。

边界对齐方式相对边界不对齐方式:是空间换时间的思想。精简指令系统计算机RISC通常采用边界对齐方式,因为边界对齐方式取指令时间相同,因此能适应指令流水。

3. 存储系统

2015-2023年共考察单选题33题,涉及大题21道。

3.1 存储器概述

2015-2023年共考察单选题6题,涉及大题1道。

3.1.1 存储器的分类

-

按在计算机中的作用(层次)分类:主存,辅存,高速缓冲存储器(Cache)。

-

按存储介质分类: 磁表面存储器(磁盘、磁带)、磁芯存储器、半导体存储器(MOS型存储器、双极型存储器)和光存储器(光盘)。

-

按存取方式分类

- 随机存储器(RAM)。存取时间与存储单元的物理位置无关,用作主存或Cache。分为静态RAM 和动态RAM。

- 只读存储器(ROM)。也随机存储。断电内容不会丢失,通常存放固定不变的程序、常数和汉字字库等。与随机存储器可共同作为主存的一部分。ROM 派生出的存储器也含可重写的类型,但写入速度比读取速度慢很多。

- 串行访问存储器。需按其物理位置的先后顺序寻址, 包括顺序存取存储器(如磁带)和直接存取存储器(如磁盘、光盘)。

-

按信息的可保存性分类

- 断电后存储信息即消失的存储器,称为易失性存储器,如RAM。断电后信息仍然保持的存储器称为非易失性存储器,如ROM、磁表面存储器和光存储器。

- 信息被读出时原存储信息被破坏,则称为破坏性读出, 读出后必须再生。

3.1.2 存储器的性能指标

- 存储容量 = 存储字数x字长(如1Mx8位)。单位换算:1B(Byte,字节)=8b(bit,位)。存储字数表示存储器的地址空间大小,字长表示一次存取操作的数据量。

- 单位成本:(每位价格)总成本/总容量。

- 存储速度: 数据传输速率(每秒传送信息的位数)=数据的宽度/存取周期。

- 存取时间(T): 分为读出时间和写入时间。

- 存取周期(T): 存取周期是指存储器进行一次完整的读/写操作所需的全部时间,即连续两次独立访问存储器操作(读或写)之间所需的最小时间间隔。

- 主存带宽(Bm): 也称数据传输速率,每秒从主存进出信息的最大数量,单位为字/秒、字节/秒(B/s)或位/秒(b/s)。

- 注意: 存取时间不等于存取周期。

3.1.3 多级层次的存储系统

-

为了解决存储系统大容量、高速度和低成本这三个相互制约的矛盾。 主要思想是上一层的存储器作为低一层存储器的高速缓存。

-

从CPU的角度看cache - 主存层,速度接近于cache,容量和位价却接近于主存。

-

从主存-辅存层分分析,速度接近主存,容量和价格却接近与辅存。

3.2 主存储器

3.2+3.3:2015-2023年共考察单选题6题,涉及大题2道。

通常把存放一个二进制位的物理器件称为存储元,它是存储器的最基本的构件。地址码相同的多个存储元构成一个存储单元。若干存储单元的集合构成存储体。

3.2.1 SRAM 芯片和 DRAM 芯片(易失性存储器)

3.2.1.1 SRAM(静态随机存储器)的工作原理

- 存储元用==双稳态触发器(六晶体管MOS)==记忆信息。

- 静态是指即使信息被读出后,它仍保持其原状态而不需要再生(非破坏性读出)。

- 存取速度快但集成度低(六个晶体管啊)、功耗较大,价格昂贵、一般用高速缓冲存储器。

3.2.1.2 DRAM(动态随机存储器)的工作原理

-

利用存储元电路中栅极电容上的电荷来存储信息的,基本存储元通常只使用一个品体管,所以它比SRAM集成度高商、位价低,功耗低。

-

DRAM 电容上的电荷一般只能维持1~2ms, 因此即使电源不断电,信息也会消失。此外,读操作会使其状态发生改处(破坏性读出),需读后再生。

-

刷新:可以采用读出的方法进行,根据读出内容对相应单元进行重写,即读后再生。对同一行进行相邻两次刷新的时间间隔称为刷新周期,通常取2ms。常用的刷新方式:

- 集中刷新: 在一个刷新周期内,利用一段固定的时间,依次对存储器的所有行进行逐行再生。在此期间停止对存储器的读/写操作,称为死时间,也称访存死区。

- 分散刷新: 将一个存储器系统的工作周期分为两部分: 前半部分用于正常的读/写操作,后半部分用于刷新。这种刷新方式增加了系统的存取周期。优点是没有死区,缺点是加长了系统的存取周期。

- 异步刷新: 结合前两种方法,使得在一个刷新周期内每一行仅刷新一次。具体做法是将刷新周期除以行数,得到相邻两行之间刷新的时间间隔1,每隔时间t产生一次刷新请求。这样就使“死时间”的分布更加分散,避免让CPU连续等待过长的时间。

-

DRAM 的刷新需要注意以下问题:

- 刷新对CPU是透明的,即刷新不依赖于外部的访问;

- 刷新单位是行,由芯片内部自行生成行地址;

- 刷新操作类似于读操作,但又有所不同。另外,刷新时不需要选片,即整个存储器中的所有芯片同时被刷新。

-

注意:虽然 DRAM 的==刷新和再生==都是恢复数据,但刷新与再生的过程并不完全相同,刷新是以行为单位,逐行恢复数据的,而再生需恢复被读出的那些单元的数据。

-

目前更常用的是SDRAM(同步DRAM)芯片,SDRAM与CPU的数据交换同步于系统的时钟信号,并且以CPU-主存总线的最高速度运行,而不需要插入等待状态。

3.2.1.3 DRAM 芯片的读/写周期(略)

3.2.1.4 SRAM和DRAM 的比较

3.2.1.4 存储器芯片的内部结构

- 存储体(存储矩阵)):存储单元的集合,由行选择线(X)和列选择线(Y)来选择所访问革元,相同行、列上的多位(位平面数)同时被读出或写入。

- 地址译码器:将地址转换为译码输出线上的高电平,以便驱动相应的读/写电路。

- 单译码法:只有一个行译码器,同一行中所有存储单元的字线连在一起,同一行中的各单元构成一个字,被同时读出或写入。缺点是地址译码器的输出线数过多。

- 双译码法:分为X和方向两个译码器,在选中的行和交叉点上确定一个存储单元,这是DRAM芯片目前普遍採用的译码结构。

- IO 控制电路:控制被选中的单元的读或写,具有放大信息的作用。

- 片选控制信号

- 读/写控制信号

3.2.2 只读存储器(ROM)

- 特点:支持随机访问;结构简单(所以位密度比可读/写存储器的高);非易失性(可靠性高)。

- 根据制造工艺的不同,分为:

- 掩模式只读存储器(MROM Mask):写入后任何人都无法改变其内容。

- 一次可编程只读存储器(PROM Programming):允许用户利用专门的设备(编程器)写入自己的程序,一旦写入,内容就无法改变。

- 可擦除可编程只读存储器(EPROM Erasable): 可以对其内容进行多次改写,但不能取代RAM,因为编程次数有限,且写入时间过长。

- Flash 存储器:兼有 ROM 和 RAM 的优点,可长期保存信息,又能快速擦除与重写。

- 固态硬盘(SSD Solid State Drive):基于闪存的固态硬盘,用固态电子存储芯阵列制成的硬盘,由控制单元和存储单元(Flash芯片)组成。优点诸多,缺点是价格高。

3.2.3 主存储器(Main Memory MM)的基本组成

- 现代计算机通常采用字节编址方式,此时存储体内的一个地址中有1字节。

- 数据线的位数通常等于存储字长,因此 MDR的位数通常等于存储字长(若数据线的位数不等于存储字长,则 MDR 的位数由数据线的位数决定。

- DRAM 芯片的地址引脚复用技术:芯片容量较大,地址位数较多。通常采用地址引脚复用技术,行地址和列地址通过相同的引脚分无后两次输入,使地址引脚数可减少一半。

- DRAM 芯片行列数的优化原则:应尽量使行、列位数相同,为减少行刷新开销,应使行数较少。

3.2.4 多模块存储器(空间并行技术)

-

思想:CPU运行速度比存储器快得多,若同时从存储器中取出n条指令,就可以充分利用CPU资源,提高运行速度。因此利用多个结构完全相同的存储模块的并行工作来提高存。

-

单体多字存储器

- 每个存储单元存储m个字,总线宽度也为m个字,一次并行读出m个字。

- 缺点:只有指令和数据在- 主存中连续存放时,这种方法才能有效提升存取速度。

-

多体拼行存储器

由多体模块组成,每个模块都有相同的容量和存取速度,各模块都有独立的读/写控制电路、地址寄存器和数据寄存器。它们既能并行工作,又能交叉工作。-

高位交叉编址 (顺序方式)

高位地址表示模块号(或体号),低位地址为模块内地址(或体内地址)。如图存储器共有4个模块,每个模块有n个单元。

在高位交叉方式下,总把低位的体内地址送到由高位体号确定的模块内进行译码。访问一个连续主存块时,总是先在一个模块内访问,等到该模块访问完才转到下一个模块访问,CPU总是按顺序访问存储模块,各模块不能被并行访问,因而不能提高存储器的吞吐率。

-

低位交叉编址(交叉方式)

低位地址为模块号,高位地址为模块内地址。把高位的体内地址送到由低位体号所确定的模块内进行译码。程序连续存放在相邻模块中,因此称采用此编址方式的存储器为交又存储器。交叉存储器可以采用轮流启动或同时启动两种方式。

-

-

轮流启动方式

-

每个模块一次读/写的位数正好等于数据总线位数,模块的存取周期为T,总线周期为r, 为实现轮流启动方式,存储器交叉模块数应大于或等于m = T/r。

-

下图展示了4体交叉轮流启动的时间关系。交叉存储器要求其模块数大于或等于m,以保证启动某模块后经过 mxr 的时间后再次启动该模块时,其上次的存取操作已经完成(以保证流水线不间断)。这样连续存取m个字所需的时间为 t=T+(m-1)r。

-

而顺序方式连续读取m个字所需的时间为=mT。可见交叉存储器的带宽大大提高。

-

交叉存储器中访存冲突的分析:若相邻的 m 次访问的访存地址出现在同一个模块内,则会发生访存冲突,此时需延迟发生冲突的访问请求。

-

-

同时启动方式:所有模块一次并行读/写的总位数正好等于数据总线位数,例如上图。

3.3 主存储器与CPU的连接

3.2+3.3:2015-2023年共考察单选题6题,涉及大题2道。

3.3.1 连接原理

- 主存通过数据总线、地址总线和控制总线与CPU连接。

- 数据总线的位数与工作频率的乘积正比于数据传输速率。

- 地址总线的位数决定了可寻址的最大内存空间。

- 控制总线(读/写)指出总线周期的类型和本次输入/输出操作完成的时刻。

通过存储器芯片扩展技术,将多个芯片集成在一个内存条上, 然后由多个内存条及主板上的 ROM 芯片组成计算机所需的主存空间,再通过总线与 CPU 相连。

3.3.2 主存容量的扩展

3.3.2.1 位扩展法(数据线数 > 芯片的数据位数)

位扩展是指对字长进行扩展(增加存储字长)。当CPU的系统数据线数多于存储芯片的数据位数时,必须对存储芯片扩位,使其数据位数与CPU的数据线数相等。

位扩展的连接方式: 各芯片的地址线、片选线和读/写控制线与系统总线相应并联;各芯片的数据线单独引出,分别连接系统数据线。各芯片同时工作。

如图所示,用8片8Kx1位的RAM 芯片组成8Kx8位的存储器。8片RAM芯片的地址线 A1~A12、片选线CS上划线、读/写控制线WE上划线都分别连在一起,每片的数据线依次作为 CPU 数据线的一位。

3.3.2.2 字扩展法(地址线位数 > 芯片地址线位数)

字扩展是指对存储字的数量进行扩展,而存储字的位数满足系统要求。系统数据线位数等于芯片数据线位数,系统地址线位数多于芯片地址线位数。

字扩展的连接方式:

- 各芯片的地址线与系统地址线的低位对应相连;

- 芯片的数据线和读/写控制线与系统总线相应并联;

- 由系统地址线的高位译码得到各芯片的片选信号。

- 各芯片分时工作。

如图所示,4片RAM 芯片的数据线 D0~D7和读写控制线 WE上划线分别连在一起。将 A15A14用作片选信号,A15A14=00时,译码器输出端0有效,选中最左边1号芯片。 以此类推。第一片芯片的的地址范围:最低地址:0000000000000000; 最高地址:0011111111111111。

3.3.2.3 字位同时扩展法

- 字位同时扩展是前两种扩展的组合。 将进行位扩展的芯片作为一组,各组的连接方式与位扩展的相同。由系统地址线高位译码产生若干片选信号,分别接到各组芯片的片选信号。

- 如下图, 用8片16Kx4位的RAM芯片组成64Kx8位的存储器。每两片构成一组16Kx8位的存储器(位扩展),4组便构成64Kx8位的存储器(字扩展)。

3.3.3 存储芯片的地址分配和片选(CPU怎样选择要访问的存储单元)

先进行片选(选择存储芯片),再进行字选(选择具体的存储单元)。

- 字选通常是由CPU送出的N条低位地址线完成(N由片内存储容量2^n决定)。

- 片选信号的产生方法分为线选法和译码片选法。

3.3.3.1 线选法 选片(直接选)

用除片内寻址外的高位地址线直接连接至各个存储芯片的片选端,当某位地址线信息为“0”时,就选中与之对应的存储芯片。例如下表,4位中哪位是0,表示哪片被选中。

优点:不需要地址译码器,线路简单。

缺点:地址空间不连续。选片的地址线必须分时为低电平(否则不能工作)WHY,不能充分利用系统的存储器空间,造成地址资源的浪费。

3.3.3.2 译码片选法 选片(通过地址译码器)

译码片选法用除片内寻址外的高位地址线通过地址译码器产生片选信号。

采用译一片74LS138作为地址译码器,高3位用于片选,则 A15A14A13=000 时选中第1片,=001时选中第二片,以此类推。

3.3.3.3 字+位扩展后求地址(2010真题)

假定用若千 2Kx4位的芯片组成一个 8Kx8 位的存储器,则地址 0B1FH 所在芯片的最小地址是( )

A. 0000H B. 0600H C. 0700H D.0800H

解答:用2Kx4位的芯片组成一个8Kx8位存储器,共需8片2Kx4位的芯片,分为4组,每组由2

片2Kx4位的芯片并联组成2Kx8位的芯片。

2Kx8位的芯片地址范为2K,即2^11,因此第一片的最小地址为11个0(000 0000 0000,0000H),最大地址为11个(111 1111 1111,07FFH)。加上第二片后,第二片的最大地址为12个1(1111 1111 1111)即0FFFH,最小地址为第一片的最大地址+1(111 1111 1111+ 1= 1000 0000 0000,0800H)。

各组芯片的地址分配如下:

第一组(两个芯片并联):0000H~07FFH

第二组(两个芯片并联):0800H~0FFFH

第三组(两个芯片并联):1000H~17FFH

第四组(两个芯片并联):1800H~1FFFH

3.3.4 存储器与 CPU 的连接

-

合理选择存储芯片

- 主要指存储芯片的类型(RAM或ROM)和数量的选择。

- 通常选用ROM存放系统程序、标准子程序和各类常数. RAM则是为用户编程而设置的。

- 在考虑芯片数量时,要尽量使连线简单、方便。

-

地址线的连接

- CPU的地址线数往往比存储芯片的地址线数要多。

- 通常将CPU地址线的低位与存储芯片的地址线相连,以选择芯片中的某一单元(字选),这部分的译码是由芯片的片内逻辑完成的。

- 而CPU地址线的高位则在扩充存储芯片时使用,用来选择存储芯片(片选),这部分译码由外接译码器逻辑完成。

-

数据线的连接

CPU的数据线数与存储芯片的数据线数不等时必须对存储芯片扩位,使其数据位数与CPU的数据线数相等。 -

读/写命令线的连接

- CPU 读/写命令线一般可直接与存储芯片的读/写控制端相连,通常高电平为读,低电平为写。

- 有些 CPU的读/写命令线是分开的(读为RD上划线,写为WE上划线,均为低电平有效)。

-

片选线的连接

- 存储器由许多存储芯片叠加而成,哪一片被选中完全取决于该存储芯片的片选控制端CS上划线是否能接收到来自CPU的片选有效信号。

- 片选有效信号与CPU的访存控制信号MREQ(低电平有效)有关,因为只有当CPU要求访存时,才要求选中存储芯片。若CPU访问IO,则MREQ为高,表示不要求存储器工作。

3.4 外存

2015-2023年共考察单选题4题,涉及大题0道。

3.4.1 磁盘存储器

-

优点:存储容量大,位价格低;可重复使用;记录信息可长期保存而不丢失,甚至可脱机存档;非破坏性读出,读出时不需要再生。

-

缺点:存取速度慢,机械结构复杂,对工作环境要求较高。

-

组成:磁盘驱动器、磁盘控制器和盘片。

- 扇区(也称块)是磁盘读/写的最小单位,即磁盘按块存取。

- 磁头数(Heads)=记录面数

- 柱面数(Cylinders)=每面盘片上有多少条磁道

- 扇区数(Sectors),表示每条磁道上有多少个扇区。

-

由于扇区按固定圆心角度划分,因此位密度从最外道向里道增加,磁盘的存储能力受限于最内道的最大记录密度。

-

磁盘高速缓存(Disk Cache):在内存中开辟一部分区域,用于缓冲将被送到磁盘上的数据。优点:写磁盘时是按“簇”进行的,可以避免频繁地用小块数据写盘;有些中间结果数据在写回磁盘之前可被快速地再次使用。

-

磁记录原理:磁头和磁性记录介质相对运动时,通过电磁转换完成读/写操作。

-

磁记录方式:通常采用调频制(FM)和改进型调频制(MFM)的记录方式。

-

性能指标:

- 记录密度:盘片单位面积上记录的二进制信息量。道密度是沿磁盘半径方向单位长度上的磁道数,位密度是磁道单位长度上能记录的二进制代码位数,面密度是位密度和道密度的乘积。

- 磁盘的容量:非格式化容量是指磁记录表面可利用的磁化单元总数,非格式化容量=记录面数x柱面数x每条磁道的磁化单元数。格式化容量是指按照某种特定的记录格式所能存储信息的总量。格式化容量=记录面数x面数x每道扇区数x每个区的容量。

- 存取时间:寻道时间(磁头移动到目的磁道的时间) +旋转延迟时间(磁头定位到要读/写扇区的时间) + 传输时间(传输数据所花费的时间)。因寻道和找扇区的距离远近不一,所以通常取平均值。

- 数据传输速率:磁盘存储器在单位时间内向主机传送数据的字节数。设磁盘转数为r转/秒,每条磁道容量为N字节,则数据传输速率为D= r N。

-

磁盘地址:柱面(磁道)号 盘面(磁头)号 扇区号

-

磁盘的工作过程:第一步是取控制字,第二步是执行控制字(寻址、读盘、写盘)。磁盘属于机械式部件,其读/写操作是串行的,不可能在同一时刻既读又写,也不可能在同一时刻读两组数据或写两组数据。

-

RAID (独立冗余 磁盘阵列)

将多个独立的物理磁盘组成一个逻辑盘,数据在多个物理盘上分割交叉存储、并行访问。- RAID0:无几余和无校验的磁盘阵列(把连续多个数据块交替地存放在不同物理磁盘的扇区中,几个磁盘交叉并行读/写, 即条带化技术。扩大了存储容量,提高了存取速度,但是没有容错能力)。

- RAID1:镜像磁盘阵列(使用两个磁盘同时进行读/写,互为备份。容量减少一半)。

- RAID2:采用纠错的海明码的磁盘阵列。

- RAID3:位交叉奇偶校验的磁盘阵列。

- RAID4:块交叉奇偶校验的磁盘阵列。

- RAID5:无独立校验的奇偶校验磁盘阵列。

优点

- RAID1:镜像磁盘阵列同时使用多个磁盘,提高了传输速率;

- 通过在多个磁盘上并行存取来大幅提高存储系统的数据吞吐量;

- 通过镜像功能,提高安全可靠性;

- 通过数据校验,提供容错能力。

3.4.2 固态硬盘(SSD)

-

基于闪存技术的存储器。它与U盘并无本质差别,只是容量更大,存取性能更好。

-

一个 SSD由一个或多个闪存芯片和闪存翻译层组成。闪存芯片替代传统旋转磁盘中的机械驱动器,而闪存翻译层将来自CPU的逻辑块读/写请求翻译成对底层物理设备的读/写控制信号,因此,这个闪存翻译层相当于代替了磁盘控制器的角色。

-

一个闪存由B块组成,每块由P页组成。

- 通常,页的大小是512B~4KB

- 每块由32~128页组成

- 块的大小为16KB~512KB

-

数据是以页为单位读/写的。只有在一页所属的块整个被擦除后,才能写这一页。不过,进行了若干次重复写之后,就会磨损坏,不能再使用。

-

随机写很慢:

- 首先,擦除块较慢,通常比访问页高一个数量级。

- 其次,若写操作试图修改一个包含已有数据的页P,则这个块中所有含有用数据的页都必须被复制到一个新(擦除过的)块中,然后才能进行对页P的写操作。

-

优点:半导体存储器构成,没有移动的部件,因而随机访问时间比机械磁盘要快很多,也没有任何机械噪声和振动,能耗更低,抗震性好,安全性高等。

-

磨损均衡(Wear Leveling)技术

-

动态均衡:写入数据时,自动选择较新的闪存块。老的闪存块先歇一歇。

-

静态磨损均衡:先进,没有数据写入时,自动监测并进行数据分配,让老的闪存块承担无须写数据的存储任务,同时让较新的闪存块腾出空间,平常的读/写操作在较新的闪存块中进行。

3.5 高速缓冲存储器(Cache)

2015-2023年共考察单选题12题,涉及大题9道。

Cache由SRAM组成,通常直接集成在CPU中。

3.5.1 程序访问的局部性原理

- 时间局部性:最近的未来要用到的信息,很可能是现在正在使用的信息,因为程序中存在循环和需要多次重复执行的子程序段,以及对数组的存储和访问操作。

- 空间局部性:近的未来要用到的信息,很可能与现在正在使用的信息在存储空间上是邻近的,因为指令通常是顺序存放、顺序执行的,数据一般也是以向量、数组等形式簇聚地存储的。

- 高速缓冲技术就是利用局部性原理,把程序中正在使用的部分数据存放在一个高速的、容量较小的 Cache 中,使 CPU的访存操作大多数针对 Cache 进行,从而提高程序的执行速度。

3.5.2 Cache 的基本工作原理

- 工作原理:Cache 和主存都被划分为大小相等的块, Cache 中的块数要远少于主存中的块数,仅保存主存中最活跃的若干块的副本,预测 CPU 在未来一段时间内欲访存的数据,将其装入Cache。

- 当CPU 发出读请求时,若在Cache 中,直接对 Cache 进行读操作,与主存无关。否则,访问主存,并把此字所在的块一次性地从主存调入 Cache。若Cache 已满,用这个块替换 Cache 中原来的某块信息。过程由硬件实现。CPU与Cache之间的数据交换以字为单位(传输所需数据进行操作),而Cache 与主存之间的数据交换则以Cache 块为单位(根据局部性原理,将Cache中信息暂存进主存以备后用)。

- 当CPU 发出写请求时,若Cache 命中,有可能会遇到 Cache 与主存中的内容不一致的问题。例如,由于CPU写Cache,把Cache某单元中的内容从X修改成X,而主存对应单元中的内容仍然是X,没有改变,因此若Cache命中,需要按照一定的写策略处理。

- 某些计算机中也采用同时访问 Cache 和主存的方式,若 Cache 命中则终止访存。

- 命中率:CPU 欲访问的信息已在Cache 中的比率。

- 平均访问时间(略)

根据 Cache 的读、写流程,可知实现 Cache 时需解决以下关键问题:数据查找;地址映射。;替换策略;写入策略。

3.5.3 Cache 和主存的映射方式

- Cache的标记位:指明它是主存中哪一块的副本,其内容相当于主存中块的编号。

- 有效位:说明Cache 行中的信息是否有效。

3.5.3.1 直接映射(装入Cache中唯一指定的位置)

-

直接映射关系:Cache行号 = 主存块号mod Cache 总行数

-

假设 Cache 共有 2 行,主存有 2^m块,在直接映射分式中,主存的第0块、第2^c块…只能映射到 Cache 的第0行,以此类推。可看出主存块号的低c位上好是它要装入的Cache行号.

-

给每个 Cache 行设置一个长为 t =m-c的标记(tag),当主存某块调入 Cache 后,就将其块号的高t 位设置在对应 Cache 行的标记中。

- Cache块中的信息是 标记项+数据,不含Cache行号和块内地址! -

CPU访存过程:找Cache行 -> 核对标记位 -> 按块内地址取信息

首先根据访存地址中间的c位,找到对应的Cache 行,将对应Cache 行中的标记和主存地址的高t位标记进行比较,若相等且有效位为1,则访问Cache“命中”,此时根据主存地址中低位的块内地址,在对应的Cache行中存取信息;若不相等或有效位为0,则“不命中”,此时CPU从主存中读出该地址所在的一块信息送到对应的Cache 行中,将有效位置1,并将标记设置为地址中的高位,同时将该地址中的内容送CPU。

3.5.3.2 全相联映射(可装入任何位置)

- 行标记用于指出该行来自主存的哪一块,访存时需要与所有Cache 行的标记进行比较。

- 优点:Cache 块的冲突概率低,只要有空闲Cache行,就不会发生冲突:空间利用率高;命中率高。

- 缺点:标记的比较速度较慢;实现成本较高,通常需采用按内容寻址的相联存储器。

- CPU访存过程:将主存地址的高位标记与Cache 各行的标记进行比较,若有一个相等且对应有效位为1,则命中,此时根据块内地址从该Cache行中取信息;若都不相等,则不命中,此时 CPU从主存中读出该地址所在的一块信息送到Cache 的任一个空闲行中,将有效位置1,并设置标记,同时将该地址中的内容送CPU。

- 通常为每个Cache 行都设置一个比较器(位数等于标记字段的位数),访存时根据标记字段的内容来访问Cache 行中的主存块,其査找过程是一种“按内容访问”的存取方式,所以是一种“相联存储器”。这种方式的时间开销和硬件开销都较大,不适合大容量 Cache。

3.5.3.3 组相联映射(组间直接映射、组内全相联映射)

-

选定适当的数量,可使组相联映射的成本接近直接映射,性能上接近全相联映射。

-

r 路组相联:每组有 r 个Cache行。

-

映射方式:Cache组号=主存块号mod Cache组数(Q)

-

访存过程:根据访存地址中组号找到对应的Cache组,将对应Cache组每个行的标记与主存地址的高位标记进行比较,若有一个相等且有效位为1则Cache 命中,此时根据主存地址中的块内地址,在对应Cache行中存取信息;若不命中,略。

-

每个 Cache 行对应一个标记项(包括有效位、脏位、替换算法位、标记位),在组相联中,将每组各行的标记项排成一行,将各组从上到下排列,构成一个二维的标记阵列。查找Cache时就是查找标记阵列的标记项是否符合要求。二路组相联的标记阵列如图所示。

-

组相联映射中比较器的个数和位数:直接映射因为每块只能映射到唯一的 Cache 行,因此只需设置1个比较器。而r路组相联映射需要在对应分组中与r个Cache行进行比较,因此需设置r个比较器。

-

例题:假设某个计算机的主存地址空间大小为 256MB,按字节编址,其数据 Cache 有 8个Cache 行,行长为64B。

-

采用直接映射方式,不考虑一致维护性位(脏位)和替换算法控制位,Cache 的总容量为多少?

因 Cache 包括了可以对 Cache 中所包含的存储器地址进行跟踪的硬件,即 Cache 的总容量=存储容量+标记阵列容量(有效位、标记位),不考虑脏位和替换算法位。

标记字段长度的计算:主存地址有28位(256MB=2^28 B);

其中6位为块内地址(2^6 B=64B);

3位为行号(2^3=8);

剩余 28-6-3=19 位为标记字段

故数据 Cache 的总容量为 8x(1+19+512)=4256 位。WHY 一共28位,体现在下图的哪里???

-

采用直接映射方式,主存地址为 3200(十进制)的主存块对应的 Cache 行号是多少?采用二路组相联映射时又是多少?

直接接映射方式中,主存按照块的大小划分,主存地址 3200对应的字块号为3200B/64B = 50。而Cache只有8行,则 50 mod 8=2,因此对应的 Cache 行号为2。

二路组相联映射方式,实质上就是将两个Cache 行合并,内部采用全相联方式,外部用直接映射方式,50 mod 4=2,对应的组号为2,即对应的Cache行号为4或5。 -

简述直接映射方式的访存过程(设访存的地址为0123456H)。

直接映射方式中,28位主存地址可分为19位的主存标记位,3位的块号,6位的块内地址,即0000 000100100011010为主存标记位,001为块号,010110为块内地址。

首先按照块号001找到相应块,然后查找对应的主存标记位,看是否相同。

若相同,再看Cache行中的有效位是否为1,若是,称此访问命中,按块内地址010110读出Cache 行所对应的单元并送入CPU中,完成访存。

若出现标记位不相等或有效位为0的情况,则不命中,访问主存将数据取出并送往CPU和Cache 对应块中,把主存地址的高19位写入001行的标记位,并将有效位置1。

-

3.5.4 Cache 中主存块的替换算法

- 随机算法(RAND):实现比较简单,但未依据程序访问的局部性原理,可能命中率较低。

- 先进先出算法(FIFO):选择最早调入的Cache行进行替换。比较容易实现,也未依据程序访问的局部性原理,因为最早进入的主存块也可能是目前经常要用的。

- 近期最少使用算法(LRU:Least Recently Used):

- 依据程序访问的局部性原理,选择近期内长久未访问过的Cache 行进行替换,其平均命中率要比FIFO的高,是堆栈类算法。对每个 Cache 行设置一个计数器(也称LRU替换位),用计数值来记录主存块的使用情况,并根据计数值选择淘汰某个块,计数值的位数与Cache 组大小有关。例如二路时有1位LRU位,四路时有2位LRU 位。

- 计数器的变化规则: 命中时,所命中的行的计数器清零,比其低的计数器加1,其余不变;未命中且还有空闲行时,新装入的行的计数器置0,其余全加1;未命中且无空闲行时,计数值为3(四路时有2位LRU 位,表示0123)的行的信息块被替换,新装入的行的计数器置0,其余全加1。

- 抖动:当集中访问的存储区超过Cache 组的大小时,命中率可能变得很低,如上例的访问序列变为1,2,3,4,5,1…,而 Cache 每组只有4行,则命中率为0,这种现象称为抖动。

- 最不经常使用算法(LFU:Least Frequently Used):

- 将一段时间内被访问次数最少的Cache行换出。每行设一个计数器,新行装入后从0开始计数,每访问一次加1,需要替换时比较各特定行的计数值,将最小的换出。

- 缺点:有些内容累计使用了很多次,会长期存在;计数器一直累计,可能需要更多为的数据为来计数。

3.5.5 Cache 的一致性问题

因Cache 中的内容是主存块副本,当对Cache 中的内容进行更新时,需选用写操作策略使 Cache 内容和主存内容保持一致。

-

对于Cache 写操作命中 (write hit):

-

全写法(直写法、write-through)。把数据同时写入 Cache和主存。当某一块需要替换时,就不必把这一块写回主存了,用新调入的块直接覆盖即可。实现简单,能随时保持主存数据的正确性。缺点是增加了访存次数,降低了Cache的效率。写缓冲:为减少直接写入主存的时间损耗,在Cache和主存之间加一个写缓冲(Write Bufer),如下图所示。CPU 同时写数据到 Cache 和写缓冲中,写缓冲再将内容写入主存。写缓冲是一个FIFO队列,可解决速度不匹配的问题。但若出现频繁写时,会使写缓冲饱和溢出。

-

回写法(write-back。写回法)。当CPU对Cache 写命中时,只把数据写入 Cache,而不立即写入主存,只有当此块被替换出时才写回主存。这种方法减少了访存次数,但存在数据不一致的隐患。为了减少写回主存的次数,给每个Cache 行设置一个修改位(脏位)。若修改位为1,则说明对应Cache行中的块被修改过,替换时须写回主存;若修改位为0,替换时无须写回主存。

-

-

对于 Cache 写操作不命中:

- 写分配法(write-alocate):更新主存单元,然后把这个主存块调入 Cache。它试图利用程序的空间局部性,缺点是每次写不命中都要从主存读一个块到Cache中(本来不是也要送的嘛)。

- 非写分配法(not-write-allocate):只更新主存单元,而不把主存块调入 Cache。

-

非写分配法通常与全写法合用,写分配法通常和回写法合用。

-

采用分离的指令Cache 和数据 Cache 的主要目的:

- Cache 的优点是设计和实现相对简单,但由于执行部件存取数据时,指令预取部件要从同一个Cache 读指令,因此会引发冲突。采用分离的Cache 结构可以解决这个问题。

- 而且分离的指令和数据 Cache 可以充分利用指令和数据的不同局部性来优化性能。

-

现代计算机的 Cache通常设立多级Cache。

-

假定设2级Cache,按离CPU的远近可各自命名为L1 Cache、L2 Cache,离 CPU越远,访问速度越慢,容量越大。

-

指令 Cache 与数据 Cache 分离一般在L1级,此时通常为写分配法与回写法合用。

-

下图是一个含有两级Cache的系统,L1Cach对L2 Cache 使用全写法,L2Cache 对主存使用回写法,由于L2Cache 的存在,其访问速度大于主存,因此避免了因频繁写时造成的写缓冲饱和溢出。

-

3.5.6 历年真题

2009

某计算机的 Cache 共有 16 块,采用二路组相联映射方式 (即每组 2块 )。每个主存块大小为 32B,按字节编址,主存129 号单元所在主存块应装入的 Cache组号是(4).

解一:Cache共16块,二路组相联,分为8组。Cache 块的大小和主存块一致。

计算块号:主存地址除以块大小(32)的商。129号单元块号是129÷32取整=4。

映射到Cache组:通过块号对组数取模。块号4对应的组号是 4 mod 8=4。

解二:Cache分为8组,因此组号占3位。

主存块大小为 32B,按字节编址,因此块内地址占5位。

主存单元地址129 = 0…0 100 00001,其中最后5位是块内地址,倒数6-8位是组号,4。

2012

计算机按字编址,Cache有4行,Cache 和主存之间交换的块大小为1个字。 Cache 内容初始为空,二路组相联映射方式和 LRU 替换策略,访问主存地址依次为0,4,8,2,0,6,8,6,4,8时,命中 Cache 的次数是( )。

解:LRU R= recently,近期最少使用算法。 地址映射采用二路组相联,4块Cache分为两组,其和主存字地址对应关系为:

第0组:01 45 89

第1组:23 67

访存过程如下。注意在第二次访问8后,8比组内后进的0新,因此下一次把0替换出去。 注:“_”表示当前访问块,“*”表示本次访问命中。

2016

有C语言程序段 for(k=0;k<1000;k++) a[k]= a[k]+ 32,若数组a和变量k均为 int型(占 4B),数据Cache 采用直接映射方式,数据区大小为 1KB、块大小为16B,该程序段执行前 Cache 为空,则该程序段执行过程中访问数组a的Cache缺失率约为 (25%)。

解:分析语句“a[k]= a[k]+ 32:首先读取 a[k]需要访问一次 a[k],之后将结果赋值给 a[k]需要访问一次,共访问两次。缓存块大小为16B,一次将载入4个4B大小的int型数据。对于 a[0]-a[3]的4次计算中,第一次访问a[0]未命中后,载入a[0]-a[3],接下来对a[0]的赋值访问以及共计6次的对a[1]-a[3]的访问均命中,失败率为1/8。后序每个块的访存失败率都相同。

2021

若计算机主存地址为 32位,按字节编址,Cache 数据区大小为 32KB,主存块大小为 32B,采用直接映射方式和回写(Write Back)策略,则Cache 行的位数至少是( 275 )。

解:需要的地址位(含行地址+行内偏移量):Cache 数据区大小为 32KB -> 2^5 * 2^10,共15位。

标记位tag还剩17bit (32-15)。

采用回写法:需要一个有效位,一个脏位。

32B(数据位):32*8bit = 256

Cache 行的总位数: 17bit(tag位)+1bit(脏位)+1bit(有效位) + 256(数据位)。

注意:Cache块中的信息是 标记项(标记位+其他)+数据,不含Cache行号和块内地址!

2022

若计算机主存地址为 32位,按字节编址,某 Cache 的数据区容量为32KB,主存块大小为64B,采用8路组相联映射方式,该Cache中比较器的个数和位数分别为( 8,20)。

解:组相联映射主存地址结构:Tag标记+组号+块内地址

块内地址:64B=2^6B,6位。

组号:Cache 数据区容量32KB,每块64B,块数=32KB/64B=2^9。8个块一组,共 2^9 /8 = 2^6 组,组号占6位。

因此标记位tag占32-6-6=20位。

访存过程:先根据组号定位到组,然后用物理地址的高 20位(T标记)与组中8个 Cache 行的 Tag 标记做并行比较(用20位比较器实现),

比较器用于并行地比较分组中所有C行的 标记位与要访问物理地址的标记位,因此比较器的个数就是分组中的 Cache 行数,比较器的位数就是Tag标记位数20。

2010

某计算机的主存地址空间大小为 256MB,按字节编址,指令 Cache 和数据 Cache分离)均有8个 Cache 行,每个 Cache 行大小为 64B,数据 Cache 采用直接映射方式。现有两个功能相同的程序A和B,程序 A按行访问 a[256][256],B按列访问。

假定 int 型数据为 32 位补码表示。程序编译时,i、j和 sum 均分配在寄存器中。数组 a按行优先方式存放,其首地址为 320(十进制数)。请回答下列问题,要求说明理由或给出计算过程。

1.不考虑用于 Cache 一致性维护和替换算法的控制位,数据 Cache 的总容量为多少?

2.数组元素 a[0][31]和 a[1][1]各自所在的主存块对应的 Cache 行号是多少(Cache 行号

从0开始)?

3.程序A和B的数据访问命中率各是多少?哪个程序的执行时间更短?

解:

1.地址总长度为28位 (主存地址空间 256MB = 2^8 * 2^20B),块内地址6位(每块64B=2^6B),Cache块号3位(8个块=2^3),因此Tag的位数为28-6-3=19位,还需一个有效位。每行 64B数据。

数据Cache 总容量:每行(64B数据 + 20位标记项/8(换算为B))*8行 = 532B。

2.数组a在主存的存放位置及其与 Cache 映射关系如下图。数组按行优先存放,首地址为320,数组元素占4B。

a[0][31]所在的主存块对应的Cache行号:[(320+(0x256+31)x4)div2^6] mod 2^3=6。

320B:按字节分配地址,B;

31*4:每个int 占32 位,占4B;

div 2^6(每行 64B,2^6B):除以每行大小得出在主存中的行数;

mod 2^3(8个 Cache 行):按照直接映射方式计算出对应的Cache中的行号。

a[1][1]所在的主存块对应的 Cache行号:[(320+(1x256 + 1)x4)div2^6] mod 2^3=5。

另解:由1)可知主存和 Cache 的地址格式如下图所示,数组按行优先方式存放,首地址为320,数组元素占4B。地址的最低6位是块内地址,倒数7-9位是块号,直接取倒数7-9位。

a[0][31]的地址为320+31x4 110 111100,因此其对应的cache行号为110=6。

a[1][1]的地址为320+256x4+1x4=1348=101010 00100:,因此其对应的Cache行号为101=5。

3.编译时i, j,sum 均分配在寄存器中,所以数据访问命中率仅考虑数组a的情况。

数组a大小为 256x256x4B=2^18B,占2^18/64=2^12个个块,按行优先存放,程序A逐行访问数组,共访问为2^16次,未命中2^12次(即每个字块的第一个数未命中),因此程序A命中率为(2^16-2^22)/2^16=93.75%。

另解:数组a按行存放,程序A按行存取。每个字块存16个int型数据,除访问的第一个不命中外,随后的 15个全命中,全部字块都符合这一规律,且数组大小为字块大小的整数倍,因此程序A命中率为15/16=93.75%。

程序 B逐列访问数组a,Cache 总数据容量为64Bx8=512B,数组一行为1KB,是 Cache 容量的2倍,可知不同行的同一列数组元素使用的同一个Cache 单元,因此逐列访问时每次都会将之前的字块置换出,即每次访问都不会命中,命中率为0。

因为从Cache 读数据比从主存读数据快很多,所以程序A的执行比程序B快得多。

2013

某 32位计算机,CPU主频为800MHz,Cache 命中时的CPI为4,Cache块大小为 32B;主存采用 8体交叉存储方式,每个体的存储字长为32位,存储周期为40ns,存储器总线宽度为 32位,总线时钟频率为 200MHz,支持突发传送总线事务。每次读突发传送总线事务的过程包括:传送首地址和命令、存储器准备数据、传送数据。每次突发传送 32B,传送地址或 32位数据均需要一个总线时钟周期。请回答下列问题要求给出理由或计算过程。

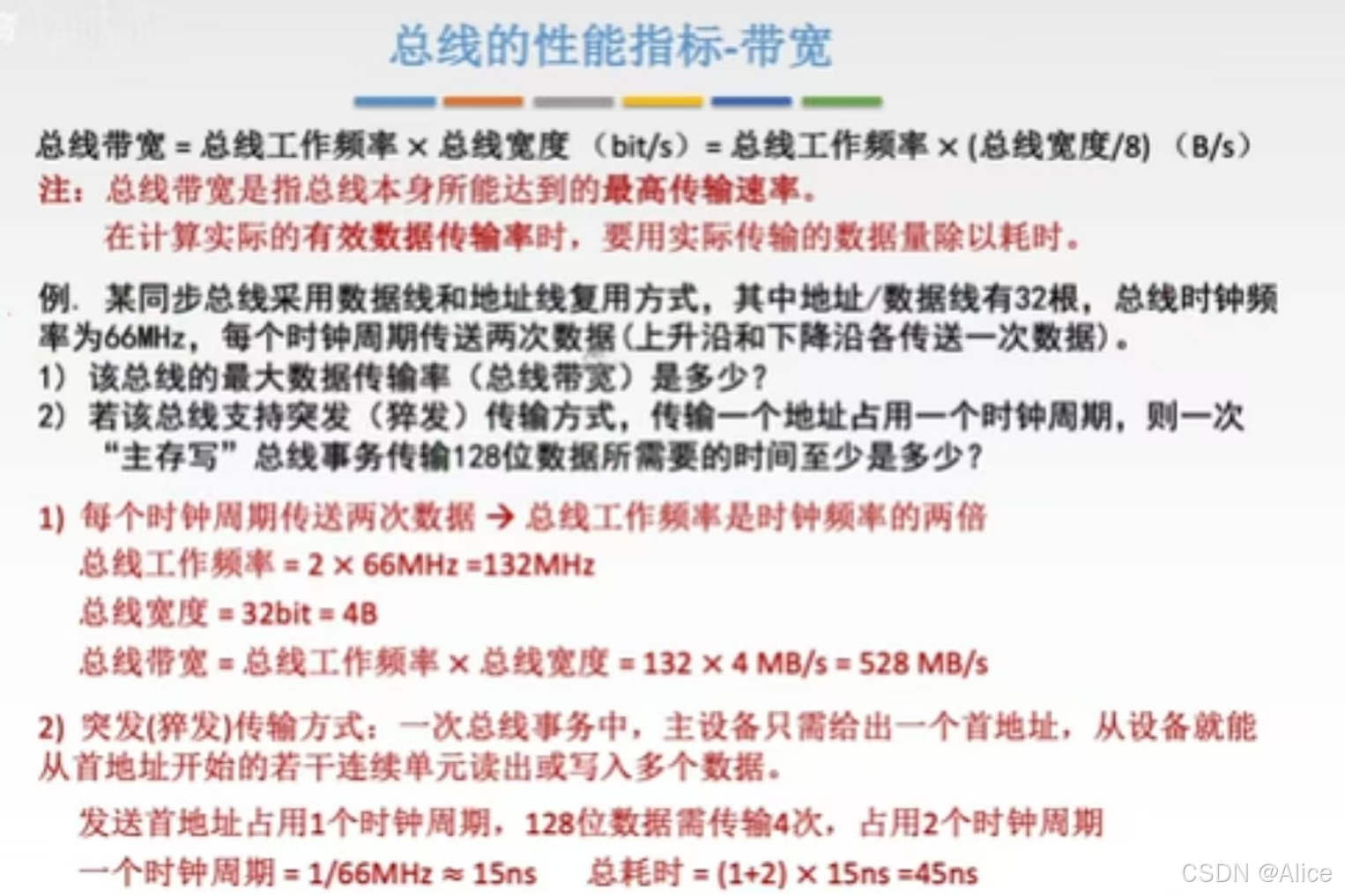

1)CPU和总线的时钟周期各为多少?总线的带宽(即最大数据传输速率)为多少?

2)Cache 缺失时,需要用几个读突发传送总线事务来完成一个主存块的读取?

3)存储器总线完成一次读突发传送总线事务所需的时间是多少?

4)若程序 BP 执行过程中共执行了 100条指令,平均每条指令需进行 1.2 次访存,Cache缺失率为 5%,不考虑替换等开销,则BP的CPU执行时间是多少?

解:

1)CPU 的时钟周期是主频的倒数,即1/800MHz=1.25ns(1S/800M=10^9 ns/(800* 10^6) = 1000 ns/8)。

总线的时钟周期是总线频率的倒数,即1/200MHz=5ns。

总线宽度为 32(4B)位,因此总线带宽为 4Bx200MHz=800MBs,或4B/5ns=800MB/S。

2)块大小是 32B,且每次突发传送 32B,因此 Cache 缺失时需要一个读突发传送总线事务读取一个主存块。

3)一次读突发传送总线事务时间为5ns+40+(8-1)*5ns+5ns=85ns。

一次读突发传送总线事务包括:一次地址传送,以及32B数据准备和传送。

5ns:一次地址传送;

(8-1)*5ns:一个体准备数据花费 40ns。第一个体开始准备5ns(一个总线周期)后,第二个体开始准备第二个数据, 并行进行。因此从8个体分别各取一分数据的时间是40+(8-1)*5=75,见下图。

5ns:第1-7个数据的传输和以上操作并行,最后一个数据的传输时间单独加上。

4)CPU 执行时间= Cache指令执行时间(每次都必须访问Cache,即100%) + Cache未命中时的额外访存开销x缺失率(需要额外访问主存的时间)。

一条指令在 Cache 中的执行时间=Cache 执行的 CPI x CPU时钟周期=4x1.25ns=5ns。

一条指令因 Cache 缺失而导致的额外访存开销(一次突发传送总线事务时间 ) x 缺失率=85ns*5%。

因此BP的100 条指令(平均每条进行 1.2 次访存)的CPU 执行时间=100*1.2*(5ns + 85ns*5%)=1010ns。

2020

主存地址为 32 位,按字节编址,指令 Cache 和数据 Cache 与主存之间均采用8路组相联映射方式,直写(WriteThrough)写策略和LRU替换算法,主存块大小为 64B,数据区容量各为32KB。开始时Cache均为空。请回答下列问题。

1)Cache 每一行中标记(Tag)、LRU 位各占几位?是否有修改位?

解:主存块大小为 64B=2^6字节,故主存地址低6位为块内地址,Cache 组数为 32KB-(64Bx8)=64=2^6(数据区容量为32KB,块大小为 64B,8路组相联),故主存地址中间6位为Cache 组号,主存地址中高32-6-6=20 位为标记。采用8路组相联映射,故每行中的LRU位占3位(2^3),采用直写方式,故无需修改位。

2)有如下C语言程序段:for(k=0:k<1024; k++) s[k].=2 * s[k];若数组s及其变量k均为int型(占4B),变量k分配在寄存器中,数组s在主存中的起始地址为0080 00C0H,则在该程序段执行过程中,访问数组s的数据Cache 缺失次数为多少?

解:008000C0H=00000000100000000000000011 000000B,主存地址的低6位为块内地址,为全0,故s位于一个主存块的开始处,占1024x4B(一个int)/64B(一个块)=64个主存块。在执行程序段的过程中,每个主存块中的 64B/4B=16个数组元素依次读、写1次,因而对每个主存块,总是第一次访问缺失,此时会将整个主存块调入Cache,之后每次都命中。综上,数组s的数据 Cache 访问缺失次数为 64 次(即访问次数)。

3)若 CPU 最先开始的访问操作是读取主存单元 0001 0003H 中的指令,简要说明从Cache 中访问该指令的过程,包括Cache 缺失处理过程。

解:00010003H=0000000000000001000 000000 0000011B,根据主存地址划分可知,组索引为0,故该地址所在主存块被映射到指令Cache的第0组。因为Cache初始为空,所有Cache行的有效位均为0,所以Cache访问缺失。此时,将该主存块取出后存入指令Cache的第0组的任意一行,并将主存地址高20位(00010H)填入该行标记字段,设置有效位,修改LRU位,最后根据块内地址000011B(最后6位)从该行中取出相应的内容。

3.6 虚拟存储器

2015-2023年共考察单选题5题,涉及大题9道。

对于应用程序员而言,虚拟存储器是透明的。虚拟存储器具有主存的速度和辅存的容量。

3.6.1 虚拟存储器的基本概念

用户编程允许涉及的地址称为虚地址或逻辑地址,虚地址对应的在储空间称为虚拟空间或程序空间。

实际的主存单元地址称为实地址或物理地址,实地址对应的是主存地址空间,也称实地址空间。

CPU使用虚地址时,先判断这个虚地址对应的内容是否已装入主存。若已在主存中,则通过地址变换,CPU 可直接访问主存指示的实际单元;若不在主存中,则把包含这个字的一页或一段调入主存后再由CPU访问。若主存已满,则采用替换算法置换主存中的交换块(页面)。

虚拟存储器也采用和 Cache 类似的技术,将辅存中经常访问的数据副本存放到主存中。但缺页(或段)而访问辅存的代价很大,提高命中率是关键,因此虚拟存储机制采用全相联映射每个虚页面可以存放到对应主存区域的任何一个空闲页位置。

当进行写操作时,不能每次写操作都同时写回磁盘,因而,在处理一致性问题时,采用回写法。

3.6.2 页式虚拟存储器(参见操作系统)

主存空间中的页称为物理页,实页、页框。

虚拟地址空间中的页称为虚拟页、虚页。

页表记录了程序的虚页调入主存时被安排在主存中的位置,一般长久地保存在内在中。

3.6.2.1 页表

有效位:也称装入位,1表示已装入主存,0表示没有调入主存。 页表项:存放该页的物理页号。位主存或磁盘地址。

脏位:也称修改位,表示页面是否被修改过。虚存机制中采用回写策略,利用脏位可判断替换时是否需要写回磁盘。

引用位:也称使用位。配合替换策略进行设置,例如是否实现最先调入(FIFO位)或最近最少用(LRU位)策略等。

有效位为0,表示发生“缺页”异常,需调用操作系统的缺页异常处理程序。缺页处理程序根据对应表项中的存放位置字段,将所缺页面从磁盘调入一个空闲的物理页框。若主存中没有空闲页框,还需要选择一个页面替换。由采用回写策略,因此换出页面时根据脏位确定是否要写回磁盘。缺页处理过程中需要对页表进行相应的更新。

优点:页面的长度固定,页表简单,调入方便。

缺点:因为程序不可能正好是页面的整数倍,最后一页的零头将无法利用而造成浪费。并且页不是逻辑上独立的实体,所以处理、保护和共享都不及段式虚拟存储器方便。

3.6.2.1 地址转换

指令给出的地址是虚拟地址,CPU执行指令时,要先将虚拟地上转换为主存物理地址,才能到主存中存取指令和数据。

虚拟地址分为两个字段:高位为虚页号,低位为页内偏移地址。

物理地址也分为两个字段:高位为物理页号,低位为页内偏移地址。

由于两者的页面大小相同,因此页内偏移地址是相等的。

页表:虚拟地址到物理地的转换是由页表实现的,页表是一张存放在内存中的虚页号和实页号的对照表。

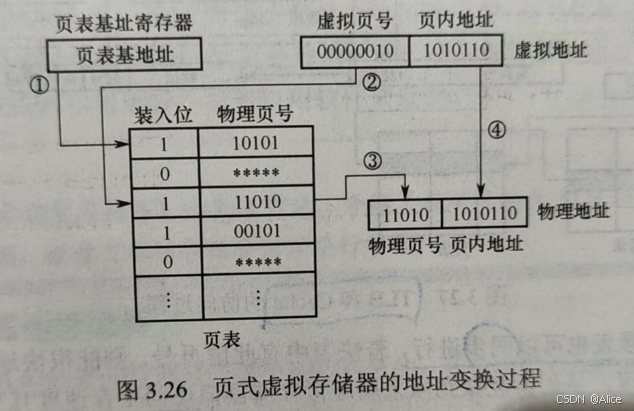

每个进程都有一个页表基地址寄春器,存放该进程的页表首地址,据此找到对应的页表首地址(对应①),然后根据虚拟地址高位的虚拟页号找到对应的页表项(对应②),若装入位为1,则取出物理页号(对应③),和虚拟地址低位的页内地址拼接,形成实际物理地址(对应④)。若装入位为0,说明缺页,需要操作系统进行缺页处理。地址变换过程如下图。

3.6.2.3 快表(TLB)

由地址转换过程可知,访存时先访问一次主存去查页表,再访问主存才能取得数据。若缺页,则还要进行页面替换、页面修改等,因此采用虚拟存储机制后,访问主存的次数更多了。

依据程序访问的局部性原理,把这些页对应的页表项存放在高速缓冲器组成的快表(TLB)中,则可以明显提高效率。相应地把放在主存中的页表称为慢表(Page))。址转换时,首先查找快表,若命中,则无须访问主存中的页表。

快表用 SRAM 实现,其工作原理类似于Cache,通常采用全相联或组相联映射方式。

TLB 表项由页表表项内容和 TLB 标记组成。全相联映射下,TLB 标记就是对应页表项的虚拟页号。组相联方式下,TLB 标记则是对应虚拟页号的高位部分,而虚拟页号的低位部分作为TLB组的组号。

3.6.2.4 具有 TLB 和 Cache 的多级存储系统(略)

3.6.3 段式虚拟存储器

段式虚拟存储器中的段是按程序的逻辑结构划分的,各个段的长度因程序而异。 把虚拟地址分为两部分:段号和段内地址。

虚拟地址到实地址之间的变换是由段表来实现的。

段表是程序的逻辑段和在主存中存放位置的对照表。段表的每行记录与某个段对应的段号、装入位、段起点和段长等信息。

因为段的长度可变,所以段表中要给出各段的起始地址与段的长度。

CPU根据虚拟地址访存时,首先根据段表基地址与段号拼接成对应的段表项,然后根据该段表项的装入位判断该段是否已调入主存(装入位为“1”,表示该段已调入主存;装入位为“0”,表示该段不在主存中)。已调入主存时,从段表读出该段在主存中的起始地址,与段内地址(偏移量)相加,得到对应的主存实地址。

因为段本身是陈旭逻辑结构所决定的一部分,所以分段对程序员来说是不透明的。而分页对程序员来说是透明的,程序员编写程序时不需知道程序将如何分页。

优点:段的分界与程序的自然分界相对应,因而具有逻辑独立性,使得它易于编译、管理、修改和保护,也便于多道程序的共享。

-

缺点:因为段长度可变,分配空间不便,容易在段间留下碎片,不好利用,造成浪费。

3.6.4 段页式虚拟存储器

把程序按逻辑结构务段,每段再划分为固定大小的页。主存空间也划分为大小相等的页。程序对主存的调入、调出仍以页为基本交换单位。

每个程序对应一个段表每段对应一个页表,段的长度必须是页长的整数倍,段的起点必须是某一页的起点。

虚地址分为段号、段内页号、页内地址三部分。

CPU根据虚地址访存时,首先根据段号得到段表地址;然后从段表中取出该段的页表起始地址,与虚地址段内页号合成,得到页表地址;最后从页表中取出实页号,与页内地址拼接形成主存实地址。

优点:兼具页式和段式虚拟存储器的优点,可以按段实现共享和保护。

缺点:在地址变换过程中需要两次查表,系统开销较大。

3.6.5 虚拟存储器与 Cache 的比较

相同之处

- 最终目标都是为了提高系统性能,两者都有容量、速度、价格的梯度。

- 2)都把数据划分为小信息块,并作为基本的交换单位,虚存系统的信息块更大。

- 3)都有地址映射、替换算法、更新策略等问题。

- 4)都依据局部性原理应用“快速缓存”的思想,将活跃的数据放在相对高速的部件中。

不同之处

- 1)Cache 主要解决系统速度,而虚拟存储器却是为了解决主存容量。

- 2)Cache 全由硬件实现,是硬件存储器,对所有程序员透明;而虚拟存储器由OS和硬件共同实现,是逻辑上的存储器,对系统程序员不透明,但对应用程序员透明。

- 3)对于不命中性能影响,因为CPU的速度约为Cache的10倍,主存的速度为硬盘的 100倍以上,因此虚拟存储器系统不命中时对系统性能影响更大。

- 4)CPU与Cache 和主存都建立了直接访问的通路,而辅存与CPU 没有直接通路。也就是说在Cache 不命中时主存能和CPU直接通信,同时将数据调入Cache;而虚拟存储器系统不命中时,只能先由硬盘调入主存,而不能直接和CPU通信。

3.6.6 历年真题(小题OVER 大题没做,看完操作做系统再处理)

4. 指令系统

2015-2023年共考察单选题14题,涉及大题14道。

4.1 指令系统

2015-2023年共考察单选题4题,涉及大题6道。

4.1.1 指令集体系结构

ISA规定的内容主要包括:

- 1)指令格式,指令寻址方式,操作类型,以及每种操作对应的操作数的相应规定。

- 2)操作数的类型,操作数寻址方式,以及是按大端方式还是按小端方式存放。

- 3)程序可访问的寄存器编号、个数和位数,存储空间的大小和编址方式。

- 4)指令执行过程的控制方式等,包括程序计数器、条件码定义等。

ISA规定了机器级程序的格式,机器语言或汇编语言程序员必须熟悉。

高级语言抽象层太高,隐藏了许多机器级程序的 细节。若程序员对 ISA 和底层硬件实现细节有充分的了解,则可以更好地编制高性能程序。

4.1.2 指令的基本格式

指令字长与机器字长没有固定的关系,既可以等于机器字长,又可以大于或 小于机器字长。

通常,把指令长度等于机器字长的指令称为单字长指令,指令长度等于半个机器 字长的指令称为半字长指令,指令长度等于两个机器字长的指令称为双字长指令。

注意:指令长度的不同会导致取指令时间开销的不同,单字长指令只需访存1次就能将指令完整取出;而双字长指令则需访存2次才能完整取出,耗费2个存取周期。

定长指令字结构:在一个指令系统中,所有指令的长度都是相等的。执行速度快,控制简单。

变长指令字结构:各种指令的长度随指令功能而异,则称为变长指令字结构。

因主存一般是按字节编址的,所以指令字长通常为字节的整数倍。

根据指令中操作数地址码的数目的不同,可将指令分成以下几种格式:

- 零地址指令: OP 只给出操作码 OP,没有显式地址。两种可能: 1)不需要操作数的指令,如空操作指令、停机指令、关中断指令等。零地址的运算类指令仅用在堆栈计算机中。通常参与运算的两个操作数隐含地从栈顶和次栈顶弹出,送到运算器进行运算,运算结果再隐含地压入堆栈。

- 一地址指令: 两种常见的形态,要根据操作码的含义确定究竟是哪一种。 1)只有目的操作数的单操作数指令,按A地址读取操作数,进行 OP 操作后,结果存回原 地址。如求反。隐含约定目的地址的双操作数指令,按指令地址A?可读取源操作数,指令可隐含约定另一个操作数由ACC(累加器)提供,运算结果也将存放在ACC中。若地址码字段均为主存地址,则完成一条一地址指令需要3次访存(取指令1 次,取操作数1次,存结果1次)。

- 二地址指令:常用于算术和逻辑运算指令。若地址码字段均为主存地址,则完成一条二地址指令需要4次访存(取指令1 次,取两个操作数2次,存结果1次)。

- 三地址指令:若地址码字段均为主存地址,则完成一条三地址需要4次访问存储器(取指令1 次,取两个操作数2次,存结果1次)。

- 四地址指令: 完成一条四地址指令需要4次访存(取指令1次, 取两个操作数2 次,存结果1次)。

4.1.3定长操作码指令格式

令在指令字的最高位部分分配固定的若干位(定长)表示操作码。

对于简化计算机硬件设计,提高指令译 码和识别速度很有利。

当计算机字长为32位或更长时,这是常规用法。

4.1.4 扩展操作码指令格式

为了在指令字长有限的前提下仍保持比较丰富的指令种类,可采取可变长度操作码,即全部 指令的操作码字段的位数不固定,且分散地放在指令字的不同位置上。

这将增加指令译码 和分析的难度,使控制器的设计复杂化。最常见的变长操作码方法是扩展操作码,它使操作码 的长度随地址码的减少而增加,不同地址数的指令可具有不同长度的操作码,从而在满足需 要的前提下,有效地缩短指令字长。

下图,指令字长为16位,其中4位为基本操作码字段OP,另有3个4位长的地址字。

- 4位基本操作码若全部用于三地址指令,则有16条。三地址指令为15条,1111留作扩展操作码之用。

- 二地址指令为15条,11111111留作扩展操作码之用;

- 一 地址指令为15条,111111111111留作扩展操作码之用;

- 零地址指令为16条。

除这种安排外,还有其他多种扩展方法,如形成15条三地址指令、12条二地址指令、63条 一地址指令和16条零地址指令,共106条指令。

在设计扩展操作码指令格式时,须注意两点:

- 1)不允许短码是长码的前缀,即短操作码不能与长操作码的前面部分的代码相同。

- 2)各指令的操作码一定不能重复。 通常情况下,对使用频率较高的指令分配较短的操作码,对使用频率较低的指令分配较长的 操作码,从而尽可能减少指令译码和分析的时间。

4.1.5 指令的操作类型

设计指令系统时必须考虑应提供哪些操作类型,指令操作类型按功能可分为以下几种。

- 1.数据传送 传送指令通常有寄存器之间的传送(MOV)、从内存单元读取数据到CPU寄存器(LOAD)、 CPU寄存器写数据到内存单元(STORE)、进栈操作(PUSH)、出栈操作(POP)等。

- 2.算术和迈辑运算 这类指令主要有加(ADD)、减(SUB)、乘(MUL)、除(DIV)、加1(INC)、减1(DEC)、 与(AND)、或(OR)、取反(NOT)、异或(XOR)等。

- 3.移位操作 移位指令主要有算术移位、逻辑移位、循环移位等。

- 4.转移操作主要有无条件转移(JMP)、条件转移(BRANCH)、调用(CALL)、返回(RET)、 陷阱(TRAP)等。转移条件一般是某个标志位的值,或几个标志位的组合。 调用指令和转移指令的区别:执行调用指令时必须保存下一条指令的地址(返回地址),当 子程序执行结束时,根据返回地址返回到主程序继续执行;而转移指令则不返回执行。

- 5.输入输出操作 这类指令用于完成 CPU 与外部设备交换数据或传送控制命令及状态信息。

4.1.6 历年真题

2017

某计算机按字节编址,指令字长固定且只有两种指令格式,其中三地址指令 29条、二地址指令107条,每个地址字段为6位,指令字长至少应该是 ( 32位 )。

**解:**三地址指令29条,操作码至少为5位。因 2^5 = 32 (32>29)。剩余 3(32-29)数个借给二地址用。==

二地址指令107条,操作码至少需要6位。因为 3*2^6 = 192 (192>107), (3表示从三地址借来的,在高位,因此和已有的6位(2^6)是相乘的关系。

每个地址字段为6位,三地址指令时总位数为5+6*3=23;二地址指令时总位数为11+6*2=23。

因计算机按字节编址,需要是8的倍数,所以指令字长至少应该是24位。

2022

设计某指令系统时,假设采用16位定长指令字格式,操作码使用扩展编码方式,地址码为6位,包含零地址、一地址和二地址3种格式的指令。若二地址指令有12条,一地址指令有254条,则零地址指令的条数最多为 (128 ).

解一:==若全都是零地址指令,最多有 2\^16条,减去一地址指令和二地址指令所占用的零地址指令空间.

2^16 - 2^12 * 12 (二地址指令占用的数量:12位地址码 * 12种指令)- 2^6 * 254 (一地址指令占用的数量:1位地址码 * 256种指令)= 128==。

解二:指令总长度16位,一位地址码占6位。

二地址操作码可以占用4位(16-6\*2),即有2^4(16)条,实际有12条。借4种给一地址指令。

一地址操作码可以占用第5-10位,即有2^6条。算而地址指令码借来的4,共可以有64\*4 = 256 条,实际有254条,可以借给零指令操作码2条。

零地址指令可以占用余下的6位 ,还有从一地址借来的2,因此共有2*2^6=128条指令。

4.2 指令的寻址方式

2015-2023年共考察单选题9题,涉及大题5道。

4.2.1 指令寻址和数据寻址

指令寻址:寻找下一条将要执行的指令

(1)顺序寻址

通过程序计数器PC加1(1条指令的长度),自动形成下一条指令的地址。

PC 自增的大小与编址方式、指令字长有关。现代计算机通常是按字节编址的,若指令字长为16位,则PC自增为(PC)+2;若指令字长为32位,则PC自增为(PC)+4。

(2)跳跃寻址

通过转移类指令实现。跳跃是指由本条指令给出下条指令地址的计算方式。而是否跳跃可能受到状态寄存器的控制。

绝对转移:地址码直接指出转移目标地址。

相对转移:地址码指出转移目的地址相对于当前PC值的偏移量。于CPU总是根据PC的内容去主存取指令的,因此转移指令执行的结果是修改 PC值,下一条指令仍然通过PC给出。

数据寻址:寻找本条指令的数据地址

如何在指令中表示一个操作数的地址,或怎样计算出操作数的地址。

通常在指令字中设置一个寻址特征字段,用来指明属于哪种寻址方式(其位数决定了寻址方式的种类)。

指令中的地址码字段并不代表操作数的真实地址,这种地址称为形式地址(A)。形式地址结合寻址方式,可以计算出操作数在存储器中的真实地址,这种地址称为有效地址(EA)。

立即寻址,则形式地址的位数决定了操作数的范围。

直接寻址,则形式地址的位数决定了可寻址的范围。

寄存器寻址,则形式地址的位数决定了通用寄存器的最大数量。

寄存器间接寻址,则寄存器的位数决定了可寻址的范围。

注意:(A)表示地址为A的数值,A既可以是寄存器编号,又可以是内存地址。

4.2.2常见的数据寻址方式

4.2.2.1 隐含寻址

不明显地给出操作数的地址,例如,单地址的指令格式就隐含约定第二个操作数由累加器(ACC)提供。

优点是有利于缩短指令字长;缺点是需增加存储操作数或隐含地址的硬件。

4.2.2.2 立即(数)寻址

地址字段指出的不是操作数的地址,而是操作数本身,也称立即数,采用补码表示。

优点是指令在执行阶段不访存,指令执行速度最快;缺点是A的位数限制了立即数的范围。

4.2.2.3 直接寻址

形式地址 A就是操作数的真实地址 EA,即 EA=A。

优点是简单,不需要专门计算操作数的地址,指令在执行阶段仅需访存一次;

缺点是A的位数限制了该指令操作数的寻址范围,操作数的地址不易修改。

4.2.2.4 间接寻址

地址字段给出的是操作数地址的地址,即EA=(A)。

优点是可扩大寻址范围(有效地址 EA 的位数大于形式地址 A的位数),便于编制程序(用间接寻址可方便地完成子程序返回);

缺点是指令在执行阶段要多次访存(一次间接寻址需 2 次访存)。由于执行速度较慢,一般为了扩大寻址范围时,通常采用寄存器间接寻址。

4.2.2.5 寄存器寻址

与直接寻址的原理一样,只是把访问主存改为访问寄存器,指令的地址字段给出的是操作数所在寄存器的编号,即 EA=R,其操作数在由R,所指的寄存器内。

优点是指令在执行阶段不用访存,只访问寄存器,执行速度快;寄存器数量远小于内存单元数,所以地址码位数较少,指令字长较短;

缺点是寄存器价格昂贵,CPU的寄存器数量有限。

4.2.2.6 寄存器间接寻址

综合了间接寻址和寄存器寻址各自的特点,指令字中的R所指寄存器给出的是操作数所在主存单元的地址,即EA=®。

相比间接寻址,这种方式既扩大了寻址范围,又减少了访存次数,在执行阶段仅需访存1次。

相比寄存器寻址,这种方式在执行阶段需要访存(因操作数在主存中)获得操作数。

4.2.2.7 相对寻址

把 PC的内容加上指令格式中的形式地址 A 而形成操作数的有效地址,即 EA=(PC)+A,其中A是相对于当前PC值的偏移量,可正可负,补码表示。

优点是操作数的地址不是固定的,它随 PC 值的变化而变化,且与指令地址之间总是相差一个固定的偏移量,因此便于程序浮动。相对寻址广泛应用于转移指令。

4.2.2.8 基址寻址

将基址寄存器(BR)的内容加上指令字中的形式地址 A 而形成操作数的有效地址,即 EA=(BR)+A。

其中基址寄存器既可采用专用寄存器,又可指定某个通用寄存器作为基址寄存器。

基址寄存器是面向操作系统的,其内容由操作系统或管理程序确定,主要用于解决程序逻辑空间与存储器物理空间的无关性。在程序执行过程中,基址寄存器的内容不变(作为基地址),形式地址可变(作为偏移量)。

采用通用寄存器作为基址寄存器时,可由用户决定哪个寄存器作为基址寄存器,但其内容仍由操作系统确定。

优点:可以扩大寻址范围(基址寄存器的位数大于形式地址 A的位数);用户不必考虑自己的程序存于主存的具体位置,因此有利于多道程序设计,并可用于编制浮动程序,但偏移量(形式地址 A)的位数较短。

4.2.2.9 变址寻址

将变址寄存器(IX)的内容加上指令字中的形式地址 A 而形成操作数的有效地址,即EA=(IX)+A,其中IX为变址寄存器(专用),也可用通用寄存器作为变址寄存器。

变址寄存器是面向用户的,在程序执行过程中,变址寄存器的内容可由用户改变(作为偏移量),形式地址 A不变(作为基地址)。

优点:可扩大寻址范围(变址寄存器的位数大于形式地址A的位数);在数组处理过程中,可设定A为数组的首地址,不断改变变址寄存器IX的内容,便可很容易形成数组中任意一个数据的地址,特别适合编制循环程序。偏移量(变址寄存器IX)的位数足以表示整个存储空间。

变址寻址与基址寻址的有效地址形成过程极为相似:

- 基址寻址面向系统,主要用于为多道程序或数据分配存储空间,因此基址寄存器的内容通常由操作系统或管理程序确定,在程序的执行过程中其值不可变,而指令字中的A是可变的。

- 变址寻址立足于用户,主要用于处理数组问题,在变址寻址中,变址寄存器的内容由用户设定,在程序执

行过程中其值可变,而指令字中的A是不可变的。

偏移寻址:相对寻址、基址寻址和变址寻址三种寻址方式非常类似,都将某个寄存器的内容与一个形式地址相加而生成操作数的有效地址,通常把这三种寻址方式称为偏移寻址。

4.2.2.10 堆栈寻址

堆栈是存储器(或寄存器组)中一块特定的、按后进先出(LIFO)原则管理的存储区,该存储区中读/写单元的地址是用一个特定寄存器给出的,该寄存器称为堆栈指针(SP) Stack Pointer。

堆栈可分为硬堆栈和软堆栈两种。

- 硬堆栈:寄存器堆栈也称硬堆栈,硬堆栈的成本较高,不适合做大容量的堆栈。

- 软堆栈:从主存中划出一段区域来做堆栈是最合算且最常用的方法。

在采用堆栈结构的计算机中,大部分指令表面上都表现为无操作数指令的形式,因为操作数地址都隐含使用了 SP。因此在读/写堆栈的前后都伴有自动完成对 SP的加减操作。

4.2.2.11 寻址方式、有效地址及访存次数表

4.2.3 历年真题

选择题 - 2009

某机器字长为16位,主存按字节编址,转移指令采用相对寻址,由2字节组成,第一字节为操作码字段,第二字节为相对位移量字段。假定取指令时,每取一字节 PC自动加 1。若某转移指令所在主存地址为 2000H,相对位移量字段的内容为06H,则该转移指令成功转移后的目标地址是(B)。

A. 2006H B. 2007H C.2008H D. 2009H

相对寻址 EA=(PC)+A,首先计算取指令后的 PC值。转移指令由2字节组成,每取一字节PC加1,取指令后的PC值为2002H,因此EA=(PC)+A=2002H+06H=2008H。本题易误选A或 B,选项A未考虑PC值的自动更新,选项B虽然考虑了PC值的自动更新,但未注意到该转移指令是一条2字节指令,PC值应是“+2”而不是“+1”。

选择题 - 2011

某机器有一个标志寄存器,其中有进位/借位标志CF、零标志ZF、符号标志 SF和溢出标志 OF,条件转移指令 bgt(无符号整数比较大于时转移)的转移条件是( ).

A. CF+OF=1B.SF+ZF=1 C. CF+ZF=1 D. CF+SF=1

假设两个无符号整数A和B,bgt指令会将A和B进行比较,也就是将A和B相减。若A>B,

则A-B肯定无进位/借位,也不为0(为0时表示两数相等),因此CF和ZF均为0,选C。其余选项中用到了符号标志SF和溢出标志OF,SF表示结果的符号,OF是有符号整数的溢出标志位,对于无符号数运算,SF和 OF没有意义,显然应当排除。

选择题 - 2014

28 某计算机有16个通用寄存器,采用32位定长指令字,操作码字段(含寻址方式位)为8位,STORE 指令的源操作数和目的操作数分别采用寄存器直接寻址和基址寻址方式。若基址寄存器可使用任意一个通用寄存器,且偏移量用补码表示,则STORE指令中偏移量的取值范围是( )。

A.-32768~+32767 B.-32767~+32768 C.-65536~+65535 D.-65535~+65536

采用32位定长指令字,其中操作码为8位,两个地址码共占用32-8=24位,而 STORE指令的源操作数和目的操作数分别采用寄存器直接寻址和基址寻址,机器中共有 16个通用寄存器,因此寻址一个寄存器需要log?16=4位,源操作数中的寄存器直接寻址用掉4位,而目的操作数采用基址寻址也要指定一个寄存器,同样用掉4位,则留给偏移量的位数为24-4-4=16位,而偏移量用补码表示,因此16位补码的表示范围为-32768~+32767。(负数多一个!)

选择题 - 2018

按字节编址的计算机中,某 double型数组 A的首地址为 2000H,使用变址寻址和循环结构访问数组A,保存数组下标的变址寄存器的初值为0,每次循环取一个数组元素,其偏移地址为变址值乘以 sizeof (double),取完后变址寄存器的内容自动加1。若某次循环所取元素的地址为2100H,则进入该次循环时变址寄存器的内容是( )。

A. 25 B. 32 C.64 D.100

根据变址寻址的公式EA=(IX)+A,有(IX)=2100H-2000H=100H=256,sizeof(double)= 8

(双精度浮点数用8位字节表示),因此数组的下标为256/8=32。

选择题 - 2019

某计算机采用大端方式,按字节编址。某指令中操作数的机器数为1234FF00H,该操作数采用基址寻址方式,形式地址(用补码表示)为FF12H,基址寄存器的内容为F0000000H,则该操作数的 LSB(最低有效字节)所在的地址是( )。

A.F000 FF12H B.F000 FF15H C. EFFF FF12H D. EFFF FF15H

注意,内存地址是无符号数。

操作数采用基址寻址方式,EA=(BR)+A,基址寄存器BR的内容为F0000000H,形式地址用补码表示为FF12H即1111111100010010B,因此有效地址为F000 0000H+( - 00EEH)= EFFFFF12H。计算机采用大端方式编址,所以低位字节存放在字的高地址处,机器数一共占4字节,该操作数的 LSB所在的地址是 EFFF FF12H+3=EFFF FF15H。

选择题 - 2020

某计算机采用16位定长指令字格式,操作码位数和寻址方式位数固定,指令系统有48 条指令,支持直接、间接、立即、相对4种寻址方式。在单地址指令中,直接寻址方式的可寻址范围是( )。

A.0~255 B. 0~1023 C.-128~127 D.-512~511

48条指令需要6位操作码字段(2?<48<26),4种寻址方式需要2位寻址特征位(4=22),

还剩16-6-2=8位作为地址码,所以直接寻址范围为0~255。注意,主存地址不能为负。

大题 - 2010

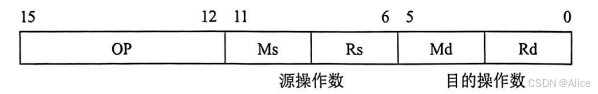

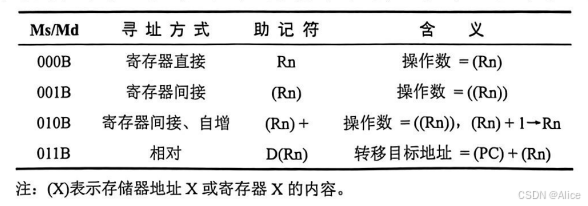

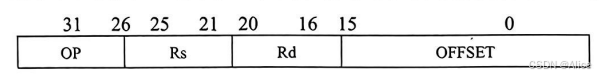

某计算机字长为 16 位,主存地址空间大小为 128KB,按字编址,采用单字长指令格式,指令各字段定义如下:

转移指令采用相对寻址方式,相对偏移量用补码表示,寻址方式定义见下表。

回答下列问题:

1)该指令系统最多可有多少条指令? 该计算机最多有多少个通用寄存器? 存储器地址寄存器(MAR)和存储器数据寄存器(MDR)至少各需要多少位?

操作码占4位,则该指令系统最多可有2^=16条指令。

操作数占6位,其中寻址方式占3 位、寄存器编号占3位,因此该机最多有2^3=8个通用寄存器。

主存地址空间大小为128KB,按字编址,字长为16位,共有128KB/2B=2^16个存储单元,因此 MAR至少为16位;

本题已说明了存储字长为16位,因此MDR至少为16位。

2)转移指令的目标地址范围是多少?

寄存器字长为16位(和机字长一致),因此PC可表示的地址范围为0~2^16-1。Rn(16位)可表示的相对偏移量为-2^15~2^15 -1(补码,负数多一个), 而主存地址空间为2^16, 因此转移指令的目标地址范围为0000H~FFFFH(0~2^16-1)。(位数这么多,可以全覆盖了)

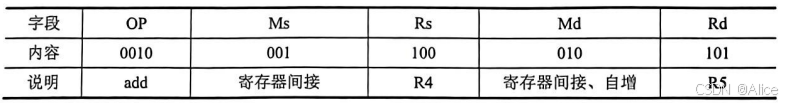

3)若操作码0010B表示加法操作(助记符为add), 寄存器R4和R5的编号分别为100B和101B,。

R4的内容为1234H, R5的内容为5678H, 地址1234H中的内容为5678H, 5678H中的内容为1234H。

则汇编语句“add(R4),(R5)+”(逗号前为源操作数,逗号后为目的操作数)对应的机器码是什么(用十六进制表示)?

该指令执行后,哪些寄存器和存储单元的内容会改变?改变后的内容是什么?

汇编语句“add (R4),(R5)+”对应的机器码为

将对应的机器码写成十六进制形式为0010 001 100 010 101B = 2315H。

该指令的功能是将 R4 的内容所指的存储单元的数据与 R5 的内容所指的存储单元的数据相加,并将结果送入R5的内容所指的存储单元中。(R4)=1234H,(1234H)=5678H;(R5)=5678H,(5678H)=1234H; 执行加法操作5678H+1234H=68ACH。之后R5自增。

该指令执行后,**R5和存储单元5678H的内容会改变,R5的内容从5678H变为5679H,**存储单元5678H中的内容变为该指令的计算结果68ACH。

大题 - 2013

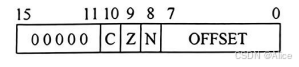

某计算机采用16位定长指令字格式,其CPU中有一个标志寄存器,其中包含进位/借位标志 CF、零标志 ZF和符号标志NF。假定为该机设计了条件转移指令,其格式如下:

其中,00000为操作码 OP;C、Z和N分别为CF、ZF和NF的对应检测位(根据指令中这3位是否为1,决定是否需要去检测相应的标识位),某检测位为1时表示需检测对应标志(检测置相应的FLAG,如FLAG值为1,则进行),需检测的标志位中只要有一个为1就转移,否则不转移。例如,若C=1,Z=0,N=1,则需检测CF和NF的值,当CF=1或NF=1时发生转移;OFFSET 是相对偏移量,用补码表示。转移执行时,转移目标地址为 (PC)+2 + 2×OFFSET; 顺序执行时,下一条指令地址为(PC)+2。

请回答下列问题:

1)该计算机存储器是按字节编址还是按字编址?该条件转移指令向后(反向)最多可跳转多少条指令?

因为指令长度为16位,且下一条指令地址为(PC)+2,因此编址单位是字节。

相对偏移量OFFSET为8位补码,表示范围为-128~127,根据转移目标地址为(PC)+2+2×OFFSET,若要向后跳转,则要求OFFSET必须为负数,OFFSET的最小值为-128,但在执行转移指令之前,PC进行了自增+2的操作,所以向后最多可跳转127条指令。

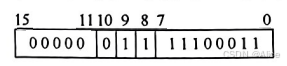

2)某条件转移指令的地址为200CH,指令内容如下图所示,若该指令执行时CF=0, ZF=0,NF=1,则该指令执行后PC的值是多少?若该指令执行时CF=1,ZF=0, NF=0,则该指令执行后 PC的值又是多少?请给出计算过程。

指令中C=0,Z=1,N=1,因此应根据 ZF和NF的值来判断是否转移。CF=0,ZF=0, NF=1时,需转移。已知指令中的偏移量为11100011B=E3H,符号扩展后为FFE3H, 左移一位(乘以2)后为FFC6H,因此PC的值(即转移目标地址)为200CH+2+FFC6H= 1FD4H。

CF=1,ZF=0,NF=0时不转移。PC的值为200CH+2=200EH。

3)实现“无符号数比较小于或等于时转移”功能的指令中,C、Z和N应各是什么?

指令中的 C、Z和N应分别设置为C=Z=1,N=0。

两个数之间的大小比较通常是对两个数做减法运算,即两个数相减当结果为0或为负时转移,若为0,则ZF标志应当是1,若为负,则借位标志应该是1,而无符号数并不涉及符号标志NF。

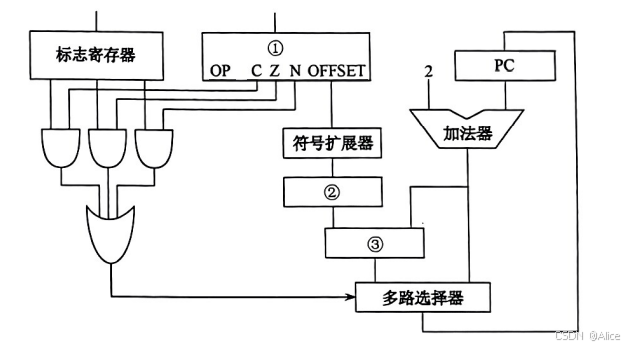

4)以下是该指令对应的数据通路示意图,要求给出图中部件①~③的名称或功能说明。

部件①用于存放当前指令,不难得出为指令寄存器;

多路选择器根据符号标志 C/Z/N来决定下一条指令的地址是PC+2还是PC+2+2×OFFSET,因此多路选择器左边线上的结果应是PC+2+2×OFFSET。根据运算的先后顺序及与 PC+2的连接,部件②用于左移一位实现乘以2,为移位寄存器。部件③用于PC+2和2×OFFSET 相加,为加法器,部件②:移位寄存器(用于左移一位);部件③:加法器(地址相加)。

大题 - 2015

题中描述的计算机,某部分指令执行过程的控制信号如下所示。

该机指令格式如下图所示,支持寄存器直接和寄存器间接两种寻址方式,寻址方式位分别为0和1,通用寄存器R0~R3的编号分别为0,1,2和3。

回答下列问题:

1)该机的指令系统最多可定义多少条指令?

指令操作码有7位,因此最多可定义2^7=128条指令。

2)假定inc、shl和sub指令的操作码分别为01H、02H和03H,则以下指令对应的机器代码各是什么?

① incR1 ;(R1)+1→R1

② shlR2,R1 ;(R1)<<1→R2

③ sub R3,(R1),R2 ; ((R1))-(R2)→R3

指令得前7为是指令码,即土木给出的01H、02H和03H。

后面3*3个数字,根据指令格式分别写出。

①“inc R1”的机器码为 0000001 001 (寄存器直接寻址1位+R1的位置代码) 000 000(单地址指令末6位为0), 即0240H。

②“shl R2,R1”的机器码为 0000010 010 (寄存器直接寻址1位+R2的位置代码) 001 000(二地址指令末3位为0), 即0488H。

③“sub R3,(R1),R2”的机器码为0000011 011 (寄存器直接寻址1位+R3的位置代码) 101(注意第一位是1,寄存器间接寻址) 010, 即06EAH。

3)假设寄存器X的输入和输出控制信号分别为Xin和Xout,其值为1表示有效,为0表示无效(如PCout=1表示PC内容送总线);存储器控制信号为MEMop,用于控制存储器的读(read)和写(write)操作。写出本题第一幅图中标号①~⑧处的控制信号或控制信号的取值。

①0;②mov;③mova;④left;⑤read;⑥sub;⑦mov;⑧SRout。 WHY

4)指令“sub R1,R3,(R2)”和“incR1”的执行阶段至少各需要多少个时钟周期?

指令“subR1,R3,(R2)”的执行阶段至少包含4个时钟周期。取R2中间接地址,按R2中的地址访存取数,取R3数,计算并存入R1。

指令“inc R1”的执行阶段至少包含2个时钟周期。取R1数,计算并存入R1。

大题 - 2021

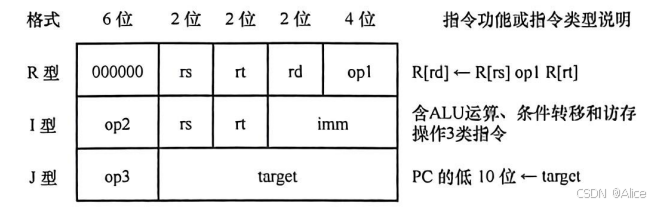

假定计算机M字长为16位,按字节编址,连接CPU和主存的系统总线中地址线为20位、数据线为8位,采用16位定长指令字,指令格式及说明如下:

其中,opl~op3为操作码,rs,rt和rd为通用寄存器编号,R[r]表示寄存器r的内容,imm为立即数,target为转移目标的形式地址。请回答下列问题。

1)ALU 的宽度是多少位?可寻址主存空间大小为多少字节?指令寄存器、主存地址寄存器(MAR)和主存数据寄存器(MDR)分别应有多少位?

解:

ALU的宽度即ALU运算对象的宽度,因此宽度为16位(通常与字长相同)。

寻址主存空间根据地址线位数计算,地址线为20位,且按字节编址,所以可寻址主存空间为2^20字节(或1MB)。

指令寄存器长度和单条指令长度相同,所以是16位。

MAR有20位,和地址线位数相同。

MDR有8位,和数据线宽度相同。

2)R型格式最多可定义多少种操作?I型和J型格式总共最多可定义多少种操作?通用寄存器最多有多少个?

解:R型格式的==操作码有4位,最多有24种操作==。I型和J型格式的**操作码有6位**,因为它们的操作码部分重叠,所以**共享这6位**的操作码空间,**且前6位全为0的编码已被R型格式占用**,因此I和J型格式最多有26-1=63种操作。

从R型和I型格式的寄存器编号部分可知,只用2位对寄存器编码,因此通用寄存器最多有4个。

3)假定opl为0010和0011时,分别表示有符号整数减法和有符号整数乘法指令,则指令01B2H的功能是什么(参考上述指令功能说明的格式进行描述)?若1,2,3号通用寄存器当前内容分别为B052H,0008H,0020H,则分别执行指令01B2H和01B3H后,3号通用寄存器内容各是什么?各自结果是否溢出?

解:指令01B2H=000000 01 10 11 0010B为一条R型指令,操作码0010表示有符号整数减法指令,其功能为R[3]-R[1]-R[2]。

执行指令01B2H后,R[3]=B052H-008H=B04AH,结果未溢出。

指令01B3H=000000 01 10 11 0011B,操作码 0011表示有符号整数乘法指令,执行指令01B3H后,R[3]=R[1]×R[2] = B052H×0008H = 8290H, B052H乘以8, 相当于将B052H算术左移3位,由于B052H是一个负数,符号位为1,在算术左移的过程中移出了101,不全为1,由此可以判断结果溢出(或者说B*8已经超出了一位16进制数表达的范围,因此溢出)。

4)若采用I型格式的访存指令中imm(偏移量)为有符号整数,则地址计算时应对 imm进行零扩展还是符号扩展?

解:在进行指令的跳转时,偏移量是一个有符号整数,因此在地址计算时,应对 imm进行符号扩展。

5)无条件转移指令可以采用上述哪种指令格式?

解:无条件转移指令可以采用J型格式,将 target 部分写入PC的低10位,完成跳转。

4.3 程序的机器级代码表示(难)

2015-2023年共考察单选题0题,涉及大题2道。

本节是 2022 年才新增的考点,但历年统考真题曾多次以综合题的形式考查过,难度较大。统考大纲没有指定具体指令集,但历年统考真题主要考查的是x86汇编指令。

4.3.1 常用汇编指令

4.3.1.1 相关寄存器

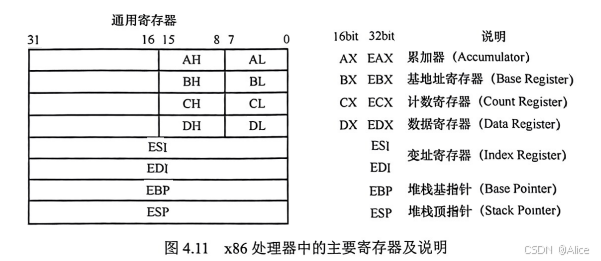

x86处理器中有8个32位的通用寄存器。

为了向后兼容,EAX、EBX、ECX和 EDX的高两位字节和低两位字节可以独立使用,E表示 Extended,表示 32位的寄存器。例如,EAX 的低两位字节称为AX,而AX的高低字节又可分别作为两个8位寄存器,分别称为 AH和AL。除 EBP 和 ESP 外,其他几个寄存器的用法是比较灵活的。

4.3.1.2 汇编指令格式

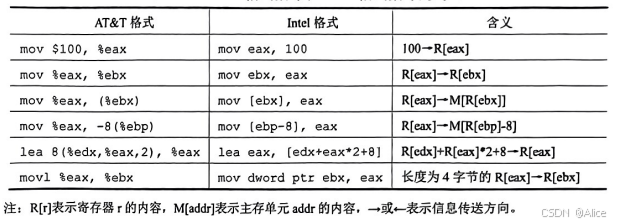

一般有两种不同的汇编格式:AT&T格式和Intel格式。主要区别:

① AT&T格式的指令只能用小写字母,而Intel格式的指令对大小写不敏感。

② 在AT&T格式中,第一个为源操作数,第二个为目的操作数,方向从左到右,合乎自然;在Intel格式中,第一个为目的操作数,第二个为源操作数,方向从右向左。

③在AT&T格式中,寄存器需要加前缀“%",立即数需要加前缀“$”;在Intel 格式中,寄存器和立即数都不需要加前缀。

④在内存寻址方面,AT&T格式使用“()”,而Intel格式使用“[ ]”。

⑤在处理复杂寻址方式时,例如AT&T格式的内存操作数 “disp(base, index, scale)”分别表示偏移量、基址寄存器、变址寄存器和比例因子,如“8(%edx,%eax,2)”表示操作数为M[R[edx]+R[eax]*2+8],其对应的Intel格式的操作数为“[edx+eax*2+8]”。

⑥在指定数据长度方面,AT&T格式指令操作码的后面紧跟一个字符,表明操作数大小,“b”表示 byte(字节)、“w”表示 word(字)或“1”表示long(双字)。Intel 格式也有类似的语法,它在操作码后面显式地注明 byte ptr、word ptr 或 dword ptr。

注 意:由于32或 64位体系结构都是由16位扩展而来的,因此用 word(字)表示16位。

mov 指令用于在内存和寄存器之间或者寄存器之间移动数据;

lea指令用于将一个内存地址(而不是其所指的内容)加载到目的寄存器。

4.3.1.3 常用指令

汇编指令通常可分为数据传送指令、算术和逻辑运算指令和控制流指令。

x86 中的指令机器码长度为1字节.

- <reg>表示任意寄存器,若其后带有数字,则指定其位数,如<reg32>表示32位寄存器(eax,ebx, ecx, edx, esi, edi, esp或 ebp);<reg16>表示16位寄存器(ax,bx,cx或 dx);<reg8>表示8位寄存器(ah,al,bh,bl,ch,cl, dh,dl)。

- <mem>:表示内存地址(如[eax]、[var+4]或 dword ptr [eax+ebx])。

- <con>:表示8位、16位或32位常数。<con8>表示8位常数;<conl6>表示16位常数;

- <con32>表示32位常数。

(1)数据传送指令

-

1)mov 指令。将第二个操作数复制到第一个操作数。mov <reg>,<reg>

举例:mov eax,ebx #将 ebx值复制到 eax

mov byte ptr [var],5 #将 5保存到 var 值指示的内存地址的一字节中.双操作数指令的两个操作数不能都是内存,即mov指令不能用于直接从内存复制到内存,若需在内存之间复制,可先从内存复制到一个寄存器,再从这个寄存器复制到内存。

-

2)push指令。将操作数压入内存的栈,常用于函数调用。ESP(E Stack P)是栈顶,入栈前先将 ESP 值减4(栈增长方向与内存地址增长方向相反),然后将操作数压入ESP指示的地址。注意,栈中元素固定为32位。push <reg32>

将eax 值入栈 push eax

将 var 值指示的内存地址的4字节(32位)值入栈 push [var] -

3)pop指令。出栈工作,出栈前先将 ESP指示的地址中的内容出栈,然后将 ESP 值加 4。

pop eax #弹出栈顶元素送到 eax

pop [ebx] #弹出栈顶元素送到 ebx 值指示的内存地址的 4字节中

(2)算术和逻辑运算指令

-

1)add/sub指令。add指令将两个操作数相加,相加的结果保存到第一个操作数中。sub 指令用于两个操作数相减,相减的结果保存到第一个操作数中。

add <reg>,<reg> / sub <reg>,<reg>sub eax,10 #eax<- eax-10

add byte ptr [var],10 #10 与 var 值指示的内存地址的一字节值相加,并将结果保存在 var 值指示的内存地址的字节中。 -

2)inc/dec 指令。将操作数自加1、自减1。inc <reg> / dec <reg>

dec eax #eax 值自减1

inc dword ptr [var] #var 值指示的内存地址的 4字节值自加1 -

- imul 指令。有符号整数乘法指令,有两种格式,两操作数或三操作数,结果都保存在第一个操作数中,第一个操作数必须为寄存器。

imul <reg32>,<reg32>

imul <reg32>,<mem>,<con>

imul eax, [var] #eax <- -eax *[var]

imul esi, edi,25 #esi <- edi * 25

乘法操作结果可能溢出,则编译器置溢出标志OF=1,以使CPU 调出溢出异常处理程序。

-

4)idiv指令。有符号整数除法指令,它只有一个操作数,即除数。被除数则为 edx:eax 中的内容(共64位)。操作结果有两部分:商和余数,商送到 eax,余数则送到 edx。idiv <reg32>

idiv ebx

idiv dword ptr[var] -

5)and/or/xor指令。and、or、xor指令分别是逻辑与、逻辑或、逻辑异或操作指令,用于操作数的位操作,操作结果放在第一个操作数中。

and <reg>,<con>/ or <reg>,<con> / xor <reg>,<con>

and eax, 0fH #将eax中的前28位全部置为0,最后4位保持不变

xor edx,edx #置edx中的内容为0 -

6)not指令。位翻转指令,将操作数中的每一位翻转,即0→1、1→0。not <mem>

not byte ptr [var] #将 var 值指示的内存地址的一字节的所有位翻转

-

7)neg 指令。取负指令。neg <reg>

neg eax #eax <- eax -

8)shl/shr 指令。逻辑移位指令,shl (left)为逻辑左移,shr (right)为逻辑右移。第一个操作数表示被操作数,第二个操作数指示移位的位数。

shl<mem>,<con8>/ shr <mem>,<con8>

shl eax,1 #将 eax 值左移 1位

shr ebx,cl #将 ebx值右移n位(n为cl中的值)

(3)控制流指令

x86处理器维持着一个指示当前执行指令的指令指针(IP),当一条指令执行后,此指针自动指向下一条指令。

IP寄存器不能直接操作,但可以用控制流指令更新。通常用标签(label)指示程序中的指令地址, 在x86汇编代码中,可在任何指令前加入标签。例如:

mov esi,[ebp+8]

begin: xor ecx,ecx

mov eax,[esi]

-

1)jmp指令。控制IP转移到label所指示的地址(从label中取出指令执行)。jmp<label>

jmp begin # 转跳到 begin 标记的指令执行

-

2)jcondition 指令。条件转移指令,依据 CPU 状态字中的一系列条件状态转移。CPU 状态字中包括指示最后一个算术运算结果是否为0,运算结果是否为负数等。

je <label>(jump when equal)

jz <label>(jump when last result was zero)

jne <label>(jump when not equal)

jg <label>(jump when greater than)

jge <label>(jump when greater than or equal to)

jl <label>(jump when less than)

jle <label>(jump when less than or equal to)cmp eax, ebx

jle done #若 eax 值<=ebx值,则跳转到 done 执行;否则执行下一条指令 -

3)cmp/test指令。cmp指令的功能相当于sub指令,用于比较两个操作数的值。test 指令的功能相当于 and指令,对两个操作数进行逐位与运算。与 sub 和 and 指令不同的是,这两类指令都不保存操作结果,仅根据运算结果设置CPU状态字中的条件码。

cmp <reg>,<mem>/ test <reg>,<mem>

cmp dword ptr [var],10 #将 var 指示的主存地址的4字节内容,与10比较

jne loop #若相等则继续顺序执行;否则跳转到loop处执行

test eax,eax #测试 eax 是否为零

jz xxxx #为零则置标志ZF为1, 转跳到xxxx处执行 -

4)call/ret 指令。分别用于实现子程序(过程、函数等)的调用及返回。

call <label>: call 指令首先将当前执行指令地址入栈,然后无条件转移到由标签指示的指令。与其他简单的跳转指令不同,call指令保存调用之前的地址信息(当 call 指令结束后,返回调用之前的地址)。

ret: ret指令实现子程序的返回机制,ret 指令弹出栈中保存的指令地址,然后无条件转移到保存的指令地址执行。

4.3.2 选择语句的机器级表示

编译器通过条件码(标志位)设置指令和各类转移指令来实现程序中的选择结构语句。条件码描述了最近的算术或逻辑运算操作的属性,可以检测这些寄存器来执行条件分支指令,最常用的条件码有CF、ZF、SF和OF。

常见的算术逻辑运算指令(add,sub,imul, or,and,shl,inc, dec,not,sal 等)会设置条件码,还有 cmp 和 test 指令只设置条件码而不改变任何其他寄存器。

4.3.3 循环语句的机器级表示

常见的循环结构语句有 while、for 和 do-while。

汇编中没有相应的指令存在,可以用条件测试和转跳组合起来实现循环的效果.。

大多数编译器将这三种循环结构都转换为 do-while 形式来产生机器代码。

4.3.4过程调用的机器级表示

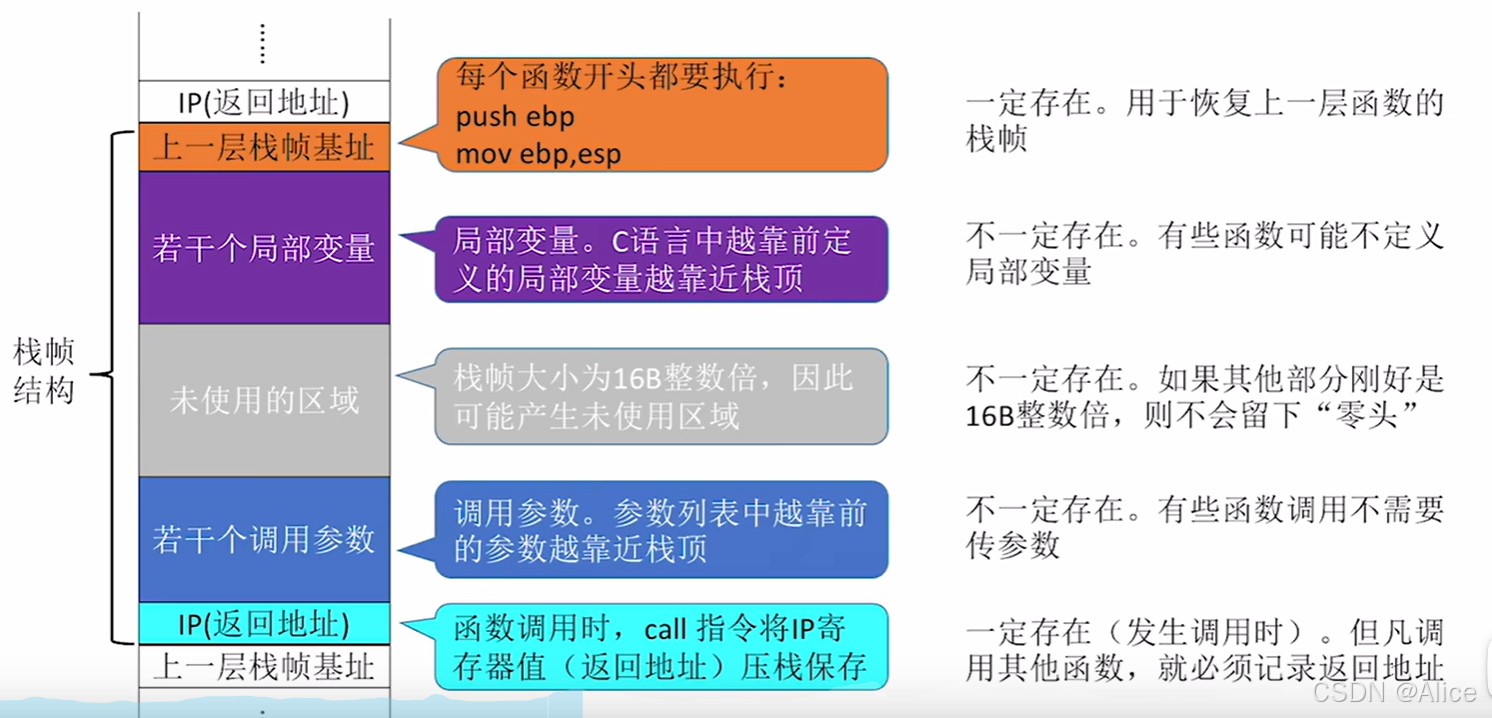

假定过程P(调用者)调用过程Q(被调用者),过程调用的执行步骤如下:

1)P将入口参数(实参)放到Q能访问到的地方。

2)P将返回地址存到特定的地方,然后将控制转移到Q。

3)Q保存P的现场(通用寄存器的内容),并为自己的非静态局部变量分配空间。

4)执行过程Q,

5)Q恢复P的现场,将返回结果放到P能访问到的地方,并释放局部变量所占空间。

6)Q取出返回地址,将控制转移到P。

用户可见寄存器数量有限,调用者和被调用者需共享寄存器,若直接覆盖对方的寄存器,则会导致程序出错。因此有如下规范:寄存器 EAX、ECX和 EDX 是调用者保存寄存器,当P调用Q时,若Q需用到这些寄存器,则由P将这些寄存器的内容保存到栈中,并在返回后由P恢复它们的值。寄存器 EBX、ESI、EDI是被调用者保存寄存器,当P调用Q时,Q必须先将这些寄存器的内容保存在栈中才能使用它们,并在返回P之前先恢复它们的值。

每个过程都有自己的栈区,称为栈帧,因此,一个栈由若干栈帧组成,寄存器 EBP (stack)指示栈帧的起始位置,寄存器 ESP n(Base)指示栈顶,栈从高地址向低地址增长。过程执行时,ESP会随着数据的入栈而动态变化,而EBP固定不变。当前栈帧的范围在 EBP和 ESP指向的区域之间。

GCC为保证数据的严格对齐, 规定每个函数的栈帧大小必须是16字节的倍数。

-

leave 指令功能相当于以下两条指令的功能:

mov esp, ebp # 使 ESP指向当前 EBP的位置

pop ebp $ EBP恢复为P中的旧值,并使 ESP指向返回地址 -

下图为调用函数的基本过程:

上方为栈底BASE;

主存地址从上放到下方递减;

栈帧建立后,首先按照倒序存入本函数的局部变量(如有);

中间是函数过程;

出现调用下一级函数的指令后,将IP返回地址存放在最下方位置,以供下一级函数的栈帧记录在其栈底,返回时导航使用。

然后在IP地址上方逆序存放将要给下一级函数使用的形参。下一级函数可以使用其栈帧内的地址+n从上方获得形参。

4.3.5 历年真题

2017 TO BE DONE

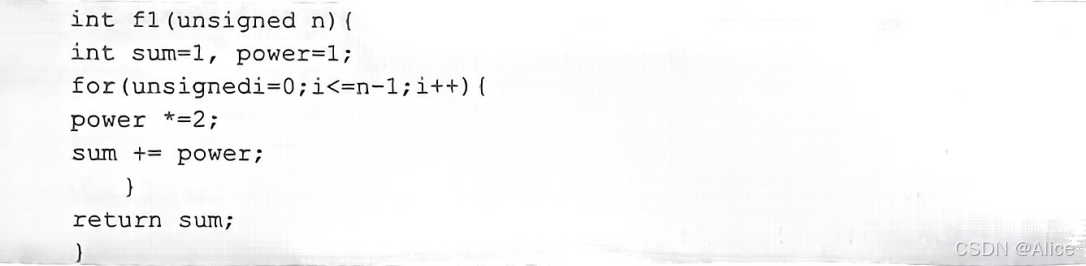

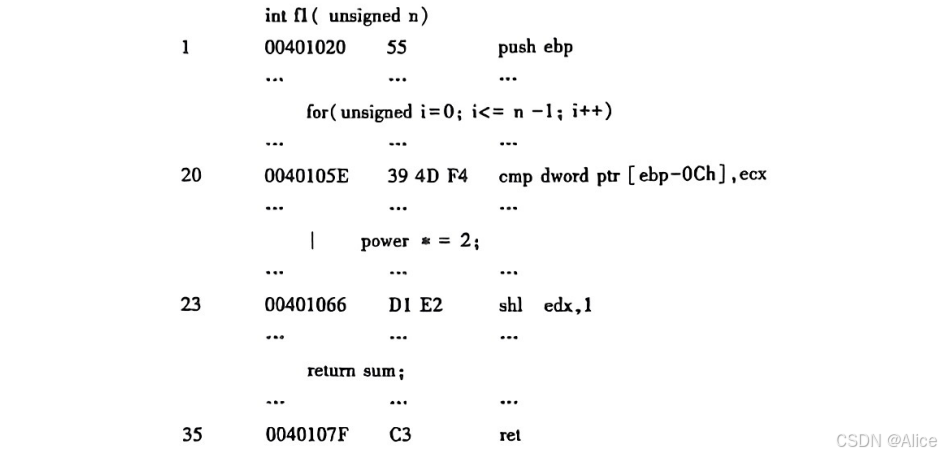

在按字节编址的计算机M上,fl的部分源程序(阴影部分)如下。将fl 中的 int 都改成 float,可得到计算f(n)的另一个函数 f2。

对应的机器级代码(包括指令的虚拟地址)如下:

其中,机器级代码行包括行号、虚拟地址、机器指令和汇编指令。

1)计算机 M是RISC还是CISC?为什么?

解 1)M为CISC。M的指令长短不一,不符合RISC指令系统的特点。

2)fl 的机器指令代码共占多少字节?要求给出计算过程。

解 2) 共占96B。因为fl的第一条指令“push ebp”所在的虚拟地址为0040 1020H,最后一条指令“ret”所在的虚拟地址为0040 107FH,所以 fl 的机器指令代码长度为 0040 107FH - 0040 1020H+1=60H=96B。

**3)第20条指令cmp通过i减n-1实现对i和n-1的比较。**执行fl(0)的过程中,当i=0时,cmp指令执行后,进位/借位标志CF的内容是什么?要求给出计算过程。

解 3)CF=1。cmp指令实现i与n-1的比较功能,进行的是减法运算。在执行 fl(0)的过程中,n=0,当i=0时,i=00000000H, 并且n-1=FFFFFFFFH。因此,执行第20条指令时,在补码加/减运算器中执行“0减FFFFFFFFH”操作,即00000000H+00000000H+1=00000001H,此时进位输出Cout=0(0-(-1) = 1,没有进位),低位进位Sub=1(执行减法时,移码减法中Sub设置为1),CF=Cout田Sub = 0田1=1。WHY

4)第23条指令shl通过左移操作实现了power *2运算,在f2中能否用 shl指令实现power *2? 为什么?

解 4)f2中不能用shl指令实现 power*2。因为shl指令把一个整数的所有有效数位整体左移,而f2中的变量 power 是 float型,其机器数中不包含最高有效数位,但包含了阶码部分,将其作为一个整体左移时并不能实现“乘以2”的功能,因此f2中不能用shl指令实现power*2。浮点数运算比整型运算要复杂,耗时也较长。

2019 TO BE DONE

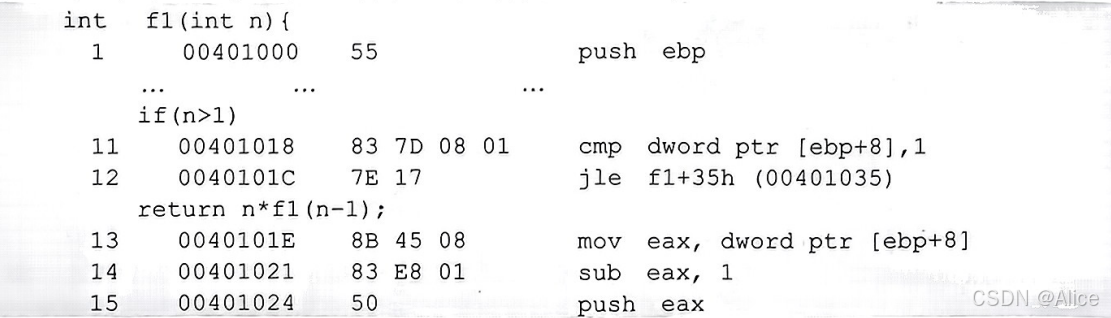

已知f(n)=n!=n×(n-1)×(n-2)x…×2×1,计算?(n)的C语言函数 fl 的源程序(阴影部分)及其在32位计算机M上的部分机器级代码如下. 其中,机器级代码行包括行号、虚拟地址、机器指令和汇编指令,计算机 M按字节编址,int型数据占32位。请回答下列问题:

1)计算 f(10)需要调用函数 fl多少次?执行哪条指令会递归调用 fl?

1)计算f(10)需要调用函数fl共10次,执行第16行的 call指令会递归调用fl。

2)上述代码中,哪条指令是条件转移指令?

哪几条指令一定会使程序跳转执行?

2)第12行的jle 指令是条件转移指令,其含义为小于或等于时转移,本行代码的意义为:当n≤1时,跳转至地址 00401035H。

第16行的 call指令为函数调用指令,第20行的jmp指令为无条件转移指令,第30行的 ret 指令为子程序的返回指令,这三条指令一定会使程序跳转执行。

3)根据第16行的 call指令,第17行指令的虚拟地址应是多少?已知第16行的 call 指令采用相对寻址方式,该指令中的偏移量应是多少(给出计算过程)?已知第16行的 call指令的后 4字节为偏移量,M是采用大端方式还是采用小端方式? TO BE COD

3)在计算机M上按字节编址,第16行的call指令的虚拟地址为0040 1025H,长度为5字节,因此第17行的指令的虚拟地址为0040 1025H+5=0040 102AH。第16行的 call 指令采用相对寻址方式,即目标地址 =(PC)+偏移量,call 指令的目标地址为0040 1000H,所以偏移量 =目标地址-(PC)=0040 1000H-0040 102AH= FFFF FFD6H。根据第 16行的 call 指令的偏移量字段为 D6 FF FFFF,可以确定M采用小端方式。

4)(13)=6227020800,但fl(13)的返回值为1932053504,为什么两者不相等?要使fl(13)能返回正确的结果,应如何修改fl的源程序?

4)因为/(13)=6227020800,其结果超出了32位int型数据可表示的最大范围,因此(13)的返回值是一个发生了溢出的错误结果。为使fl(13)能返回正确结果,可将函数 fl 的返回值类型改为 double(或 long long,或 long double,或 float)类型。

5)第19行的imul指令(有符号整数乘)的功能是R[eax]—R[eax]×R[ecx],当乘法器输出的高、低32位乘积之间满足什么条件时,溢出标志OF=1?要使CPU在发生溢出时转异常处理,编译器应在imul指令后加一条什么指令?

5)若乘积的高33位不全为0或不全为1,则OF=1。编译器应在imul指令后加一条“溢出自陷指令”,使得CPU 自动查询溢出标志OF,当OF=1时调出“溢出异常处理程序”。

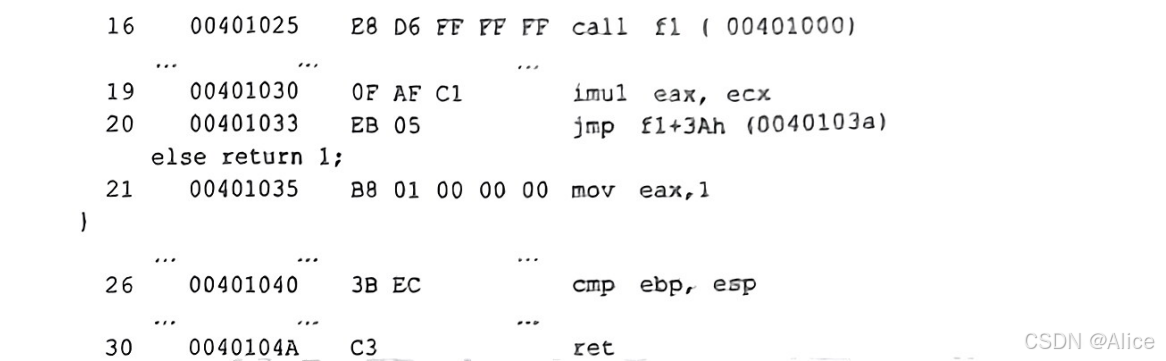

2019-2 TO BE DONE

对于上题

1) 若计算机M的主存地址为32位,采用分页存储管理方式,页大小为4KB,则第1行的push指令和第30行的 ret指令是否在同一页中(说明理由)?

解:因为页大小为4KB,所以虚拟地址的高20位为虚拟页号。第1行的 push指令和第30 行的ret 指令的虚拟地址的高20位都是00401H,因此两条指令在同一页中。

2) 若指令 Cache有64行,采用4路组相联映射方式,主存块大小为64B,则 32 位主存地址中,哪几位表示块内地址?

解:指令 Cache有64块,采用4路组相联映射方式,因此指令 Cache共有 64/4=16组,Cache组号共4位。主存块大小为64B,因此块内地址为低6位。综上所述,在32位主存地址中,低6位为块内地址,中间4位为组号,高22位为标记。

**3) 哪几位表示 Cache组号?**哪几位表示标记(tag)信息?读取第16行的 call指令时,只可能在指令 Cache的哪一组中命中(说明理由)?

解:因为页大小为4KB,所以虚拟地址和物理地址的最低12 位完全相同,因此 call 指令虚拟地址 00401025H中的025H=0000 0010 0101B 为物理地址的低12位,对应的7~10 位为组号,因此对应的 Cache 组号为0。

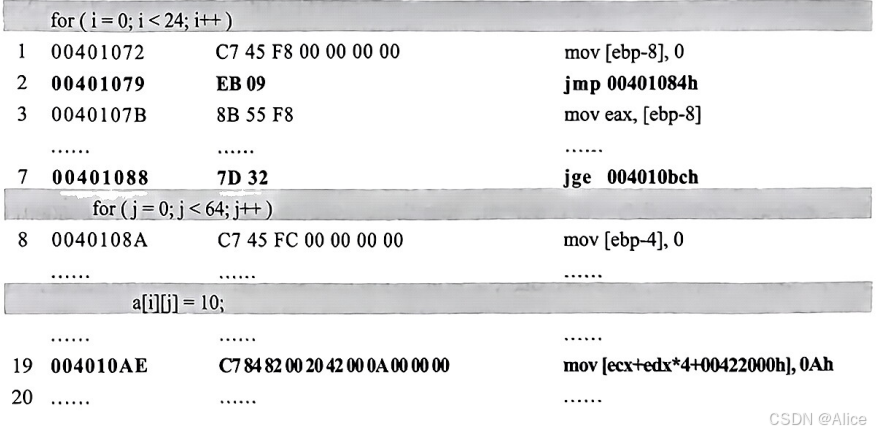

2023

某C语言程序段在计算机M上的部分机器级代码如下,数组a的定义为“int a[24][64];”,每个机器级代码行中依次包含指令序号、虚拟地址、机器指令和汇编指令。

请回答下列问题。

1)第 20 条指令的虚拟地址是多少?

解:注意:可以看出指令长度不固定。第19条指令的虚拟地址为0040 10AEH, 且第19条指令占11字节,因此第20条指令的虚拟地址为0040 10AEH+11(十进制) =0040 10B9H。

2)已知第2条jmp和第7条jge都是跳转指令,其操作码分别是EBH和7DH,跳转目标地址分别为0040 1084H、0040 10BCH,这两条指令都采用什么寻址方式?给出第2条指令 jmp的跳转目标地址计算过程。

解:第2条指令的虚拟地址为0040 1079H, 指令(EB 09)长度为2字节,取指后,PC+2变为0040 107AH,而需要转移指令的目标地址为0040 1084H, 因此偏移量需设为0040 1084H - 0040 107AH=09H。根据第2条指令的机器码可知,09H 恰好是第2条指令给出的偏移量。第7条指令的分析同理。因此,第2条jmp和第7条jge指令都采用相对寻址方式。

第2条指令jmp的跳转目标地址 =0040 1079H+2(十进制)+09H=00401084H。

3)已知第19条mov指令的功能为“a[i][j] <-10”,其中ecx和edx为寄存器名,0042 2000H是数组 a的首地址,指令中源操作数采用什么寻址方式?

已知edx中存放的是变量 j,ecx中存放的是什么?

根据该指令的机器码判断M采用的是大端还是小端方式。

解:第19条指令的源操作数为0AH, 直接在机器指令中(0A 00 00 00)给出,因此采用立即(数)寻址方式。

数组a的一行有64个元素,每个元素占4字节,因此a[i][j]的地址应为0042 2000h + i×64×4 + j×4 = 00422000h + i×256 + j×4, 根据汇编指令中给出的计算公式 ecx+edx*4+00422000h 可知,ecx 中存放的是i×256。

根据本指令中的0AH在指令中存放为0A 00 00 00形式,推测出M采用小端方式。

4)第一次执行第19条指令时,取指令过程中是否会发生缺页异常?为什么?

解:不会。因为该指令所在的该程序段都在页号为00401H 的同一个页面中,执行时该页已在主存。

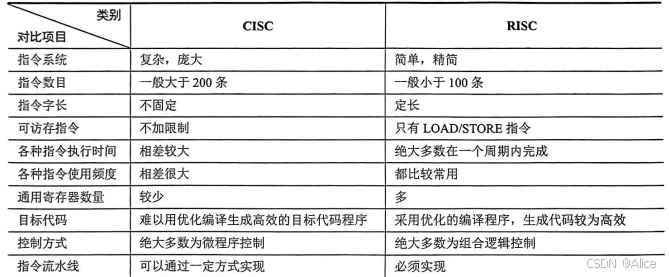

4.4 CISC和RISC的基本概念

2015-2023年共考察单选题1题,涉及大题1道。

复杂指令系统计算机(CISC),典型的有采用 x86 架构的计算机。主要用于台式机和笔记本(体积大,可以容下大的硬件)。Complex Instruction Set Computer。

精简指令系统计算机(RISC),典型的有ARM、MIPS 架构的计算机。主要用于收集和平板。

5. 中央处理器 CPU

2015-2023年共考察单选题27题,涉及大题17道。

5.1 CPU的功能和基本结构

2015-2023年共考察单选题5题,涉及大题4道。

5.1.1 CPU的功能 (运算器 + 控制器)

控制器:负责协调并控制计算机各部件执行程序的指令序列;

运算器:对数据进行加工。

CPU 的具体功能:

1)指令控制。完成取指令、分析指令和执行指令的操作,即程序的顺序控制。

2)操作控制。产生完成一条指令所需的操作信号,把各种操作信号送到相应的部件,从而控制这些部件按指令的要求正确执行。

3)时间控制。严格控制各种操作信号的出现时间、持续时间及出现的时间顺序。

4)数据加工。对数据进行算术和逻辑运算。

5)中断处理。对运行过程中出现的异常情况和中断请求进行处理。

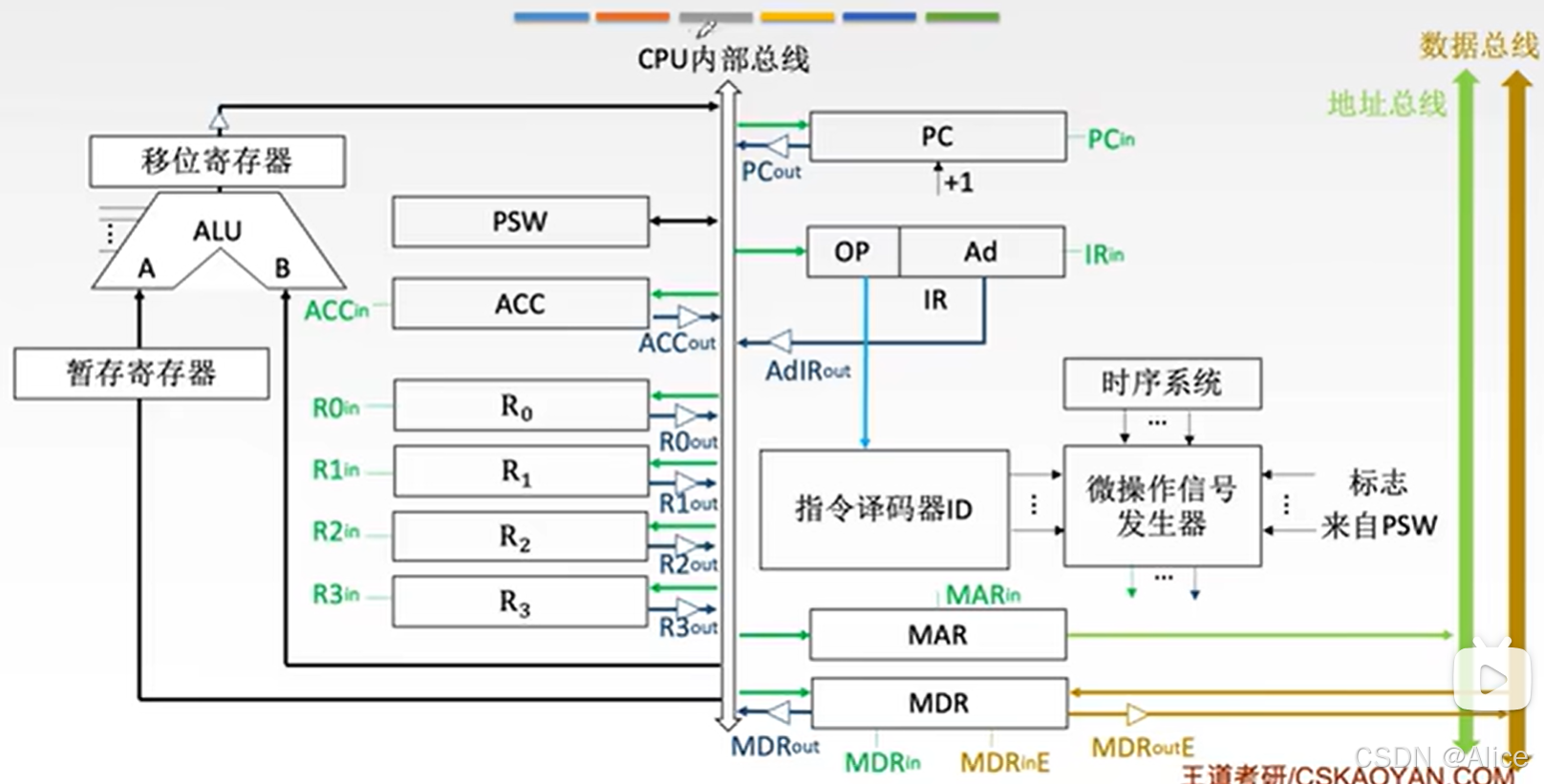

5.1.2 CPU 的基本结构

主要由运算器和控制器两大部分组成;

也可分为数据通路和控制部件两大组成部分。

1.运算器

根据控制器送来的命令,对数据执行算术运算(加、减、乘、除)、逻辑运算(与、或、非、异或、移位、求补等)或条件测试(用于设置ZF、SF、OF和CF等标志位,作为条件转移的判断条件)。

2.控制器

执行指令,每条指令的执行是由控制器发出的一组微操作实现的。

控制器的工作原理:根据指令操作码、指令的执行步骤(微命令序列)和条件信号来形成当前计算机各部件要用到的控制信号。计算机整机各硬件系统在这些控制信号的控制下协同运行,产生预期的执行结果。控制器是整个系统的指挥中枢,在控制器的控制下,运算器、存储器和输入/输出设备等功能部件构成一个有机的整体,根据指令的要求指挥全机协调工作。

5.1.3 CPU的寄存器

按汇编语言(或机器语言)程序是否可访问分为两类:

一类是用户可见寄存器,可对这类寄存器编程,可以通过使用这类寄存器减少对主存储器的访问次数,如通用寄存器组(含基址/变址寄存器)、程序状态字寄存器、程序计数器、累加寄存器、移位寄存器;

另一类是用户不可见寄存器,对用户是透明的,不可对这类寄存器编程,它们被控制部件使用,以控制CPU的操作,如存储器地址寄存器、存储器数据寄存器、指令寄存器、暂存寄存器。

1.运算器中的寄存器

1)通用寄存器组(GPRs)。用于存放操作数(包括源操作数、目的操作数及中同结果)和各种地址信息等,如 AX、BX、CX、DX、SP等。在指令中要指定寄存器的编号,才能明确是对哪个寄存器进行访问。SP是堆栈指针,用于指示栈顶的地址。

2)累加寄存器(ACC)。通用寄存器,用于暂存ALU 运算的结果。

3)移位寄存器(SR)。可用来存放操作数;在控制信号的作用下,此寄存器中的数据可根据需要向左或向右移位。

4)暂存寄存器。用于暂存从数据总线或通用寄存器送来的操作数,以便在取出下一个操作数时将其同时送入 ALU。暂存寄存器对应用程序员是透明的(不可见)。

5)程序状态字寄存器(PSW)。保留由算术/逻辑运算指令或测试指令的运行结果而建立的各种状态信息,如溢出标志(OF)、符号标志(SF)、零标志(ZF)、进位标志(CF)等。每个标志位通常由一位触发器来保存,这些标志位组合在一起称为程序状态字。

2.控制器中的寄存器

1)程序计数器(PC)。用于指出欲执行指令在主存储器中的存放地址。若 PC和主存储器均按字节编址,则PC的位数等于主存储器地址位数。CPU 根据 PC 的内容从主存储器中取指令,然后送入指令寄存器。指令通常是顺序执行的,因此 PC具有自动加1的功能(这里的“1”是指一条指令的字节数);当遇到转移类指令时,PC的新值由指令计算得到。

2)指令寄存器(IR)。用于保存当前正在执行的指令,IR 的位数等于指令字长。

3)存储器地址寄存器(MAR)。用于存放要访问的主存储器单元的地址,MAR的位数等于主存储器地址线数,它反映了最多可寻址的存储单元的个数。

4)存储器数据寄存器(MDR)。用于存放向主存储器写入的信息或从主存储器读出的信息,MDR 的位数等于存储字长。当CPU和主存储器交换信息时,都要用到MAR和 MDR。

5.1.4 历年真题 2016 选择

某计算机的主存储器空间为 4GB,字长为 32 位,按字节编址,采用32 位字长指令字格式。若指令按字边界对齐存放,则程序计数器(PC)和指令寄存器(IR)的位数至少分别是( )。

解:程序计数器(PC)用于指出下一条指令在内存中的地址,虽然可以用32位的地址来表示指令地址,但实际上内存中最多只能存放4GB/32位 =2^30条指令(注意B是8bit),故可以用30位的字地址来表示指令地址。

题干已说明指令按字边界对齐的方式存放,也就是说,指令地址都是4字节的整数倍,因此为了让PC的位数最少,可以采用字地址,取指令时将PC值左移2位到主存中取指令。

指令寄存器(IR)用于存放从内存中取出的指令,它取决于指令字长,故 IR 的位数至少是32位。

5.2 指令执行过程

2015-2023年共考察单选题2题,涉及大题2道。

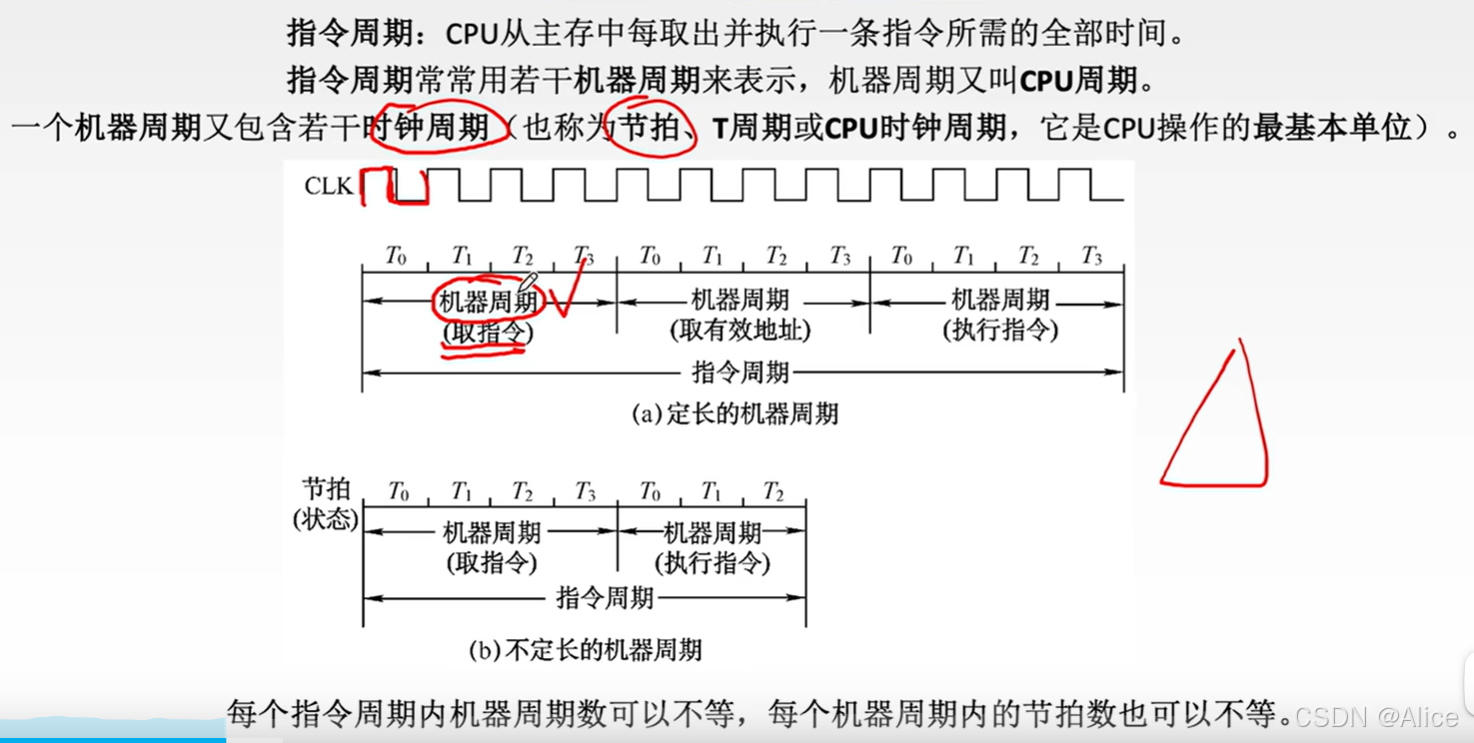

5.2.1 指令周期

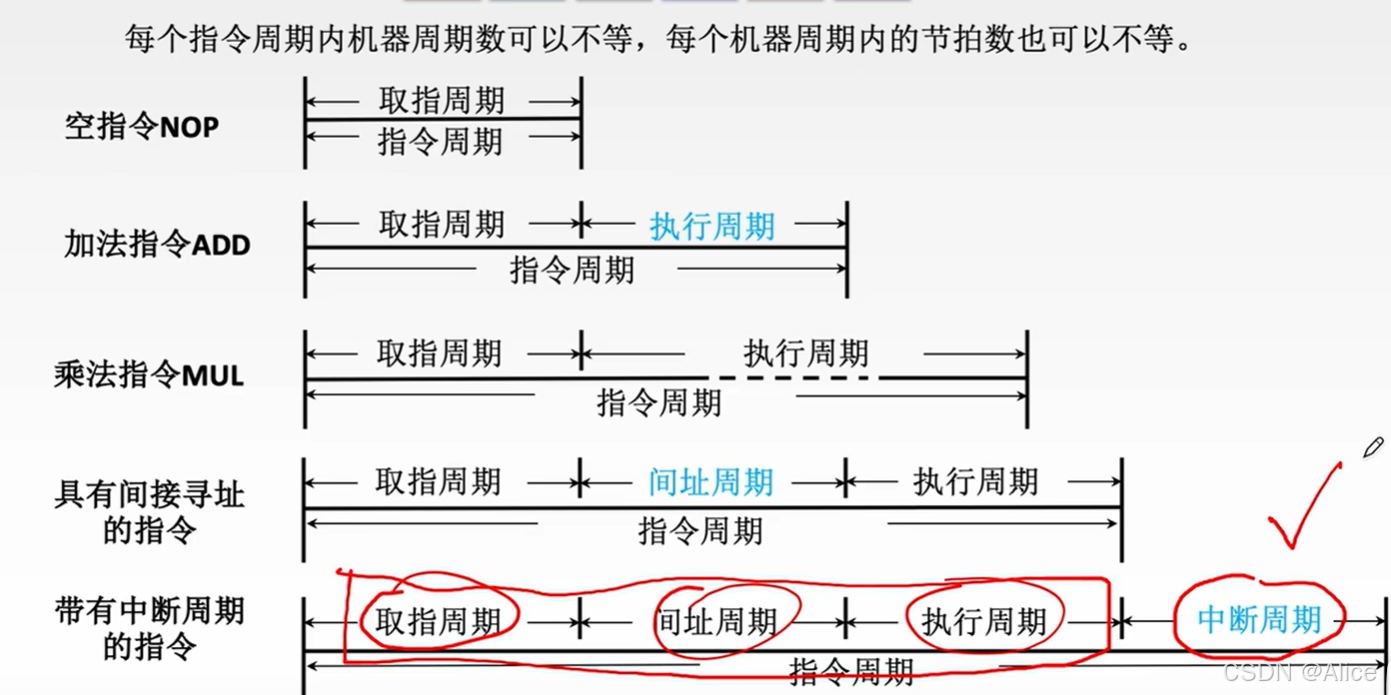

CPU每取出并执行一条指令所需的全部时间称为指令周期,不同指令的指令周期可能不同。

指令周期通常可用若干机器周期来表示,每个指令周期内的机器周期数可以不等。

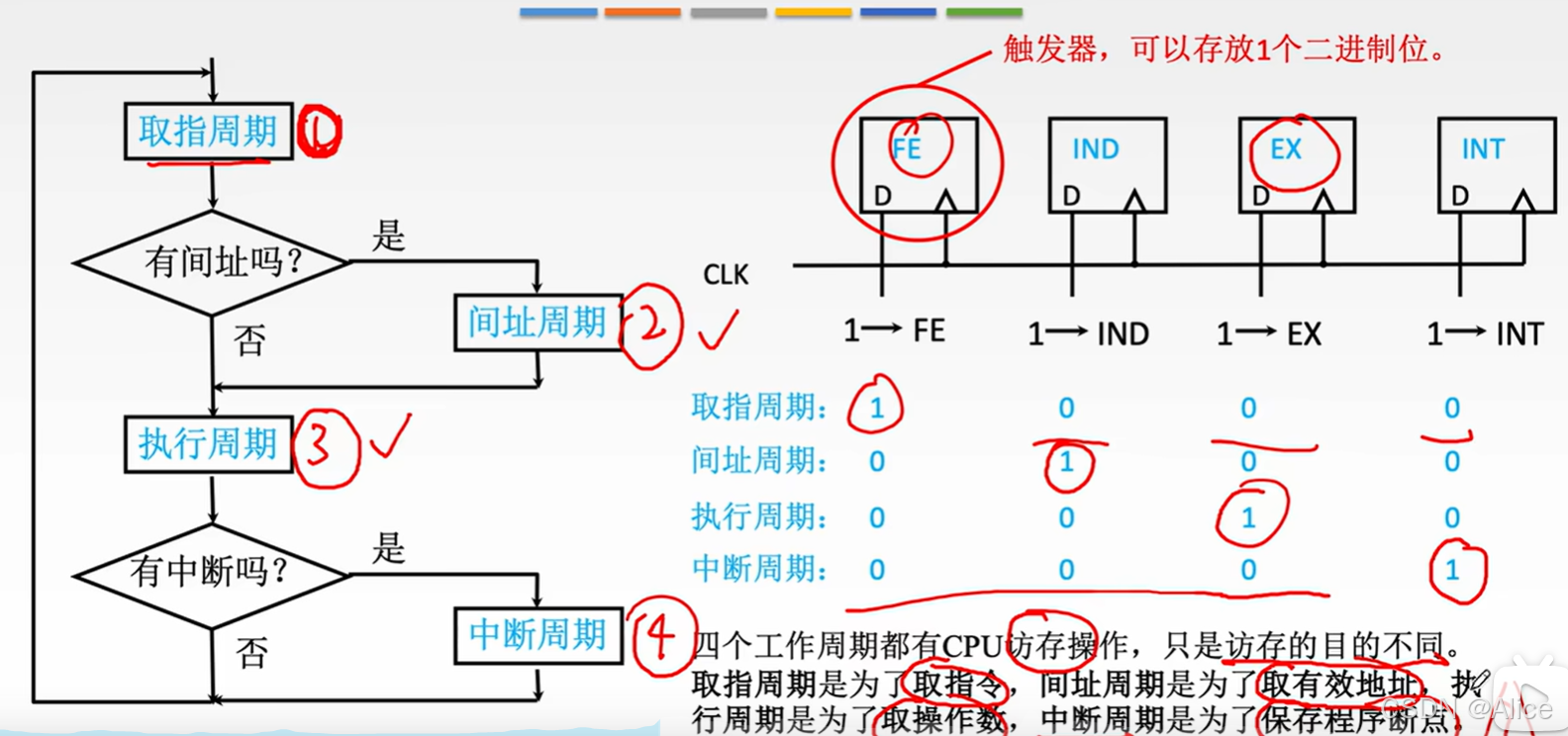

注 意:中断周期中的进栈操作是将 SP减“1”,这和传统意义上的进栈操作相反,原因是计算机中的堆栈都是向低地址方向增长,所以进栈操作是减“1”而不是加“1”。

5.2.2 指令周期的数据流

根据指令要求依次访问的数据序列。

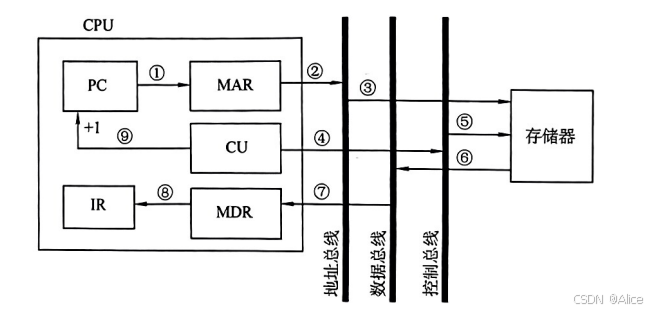

1.取指周期:根据 PC中的内容从主存中取出指令代码并存放在IR中。

1)PC①MAR②地址总线③存储器。

2)CU 发出读命令④控制总线⑤存储器。

3)主存(6)数据总线(7)MDR(8)IR(存放指令)。

4)CU发出控制信号(9)PC内容加1。

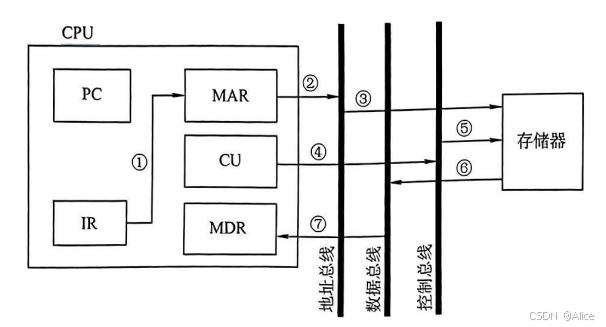

2.间址周期:取操作数有效地址。

1)Ad(IR)(或 MDR)①MAR②地址总线③存储器。(Ad(IR)表示取出IR中存放的指令字的地址字段)

2)CU 发出读命令④控制总线⑤存储器。

3)主存(6)数据总线(7)MDR(存放有效地址)。

3.执行周期:取操作数,并根据IR中的指令字的操作码通过ALU操作产生执行结果。不同指令的执行周期操作不同,因此没有统一的数据流向。

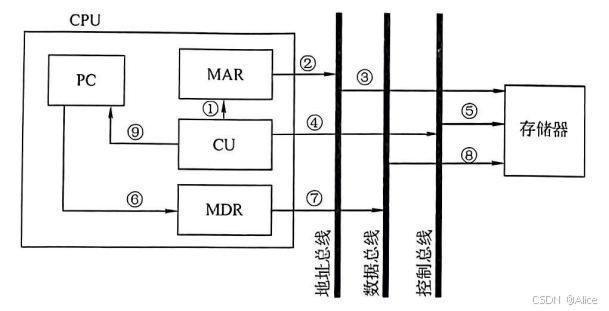

4.中断周期:处理中断请求。假设程序断点存入堆栈中,并用 SP指示栈顶地址,而且进栈操作是先修改栈顶指针,后存入数据。

1)CU 控制将 SP减1,SP①MAR②地址总线③存储器。

2)CU发出写命令④控制总线⑤存储器。

3)PC⑥MDR⑦数据总线(8)主存(程序断点存入存储器)。

4)CU(中断服务程序的入口地址)⑨PC。

5.2.3 指令执行方案

不同的处理器采用不同的方案来安排指令的执行步骤。

1.单周期处理器

所有指令都选用相同的执行时间来完成。此时每条指令都在一个时钟周期内完成(即 CPI=1),指令之间串行执行,因此指令周期取决于执行时间最长的指令的执行时间。

2.多周期处理器

指令需要几个周期就为其分配几个周期,指令之间仍是串行执行。

3.流水线处理器

采用指令之间并行执行的方案,其追求的目标是力争在每个时钟周期完成一条指令的执行过程(只在理想情况下才能达到该效果,此时 CPI=1)。

这种方案通过在每个时钟周期启动一条指令,尽量让多条指令同时运行,但各自处在不同的执行步骤中。

5.2.4 历年真题 (选择)

2009

冯·诺依曼计算机中指令和数据均以二进制形式存放在存储器中,CPU区分它们的依据是( )。

A.指令操作码的译码结果 B. 指令和数据的寻址方式

C.指令周期的不同阶段 D.指令和数据所在的存储单元

虽然指令和数据都以二进制形式存放在存储器中,但 CPU 可以根据指令周期的不同阶段来区分是指令还是数据,通常在取指阶段取出的是指令,在执行阶段取出的是数据。

本题容易误选选项A,需要清楚的是,CPU 只有在确定取出的是指令后,才会将其操作码送去译码,因此不可能依据译码的结果来区分指令和数据。

2011

假定不采用 Cache和指令预取技术,且机器处于“开中断”状态,则在下列有关指令执行的叙述中,错误的是( )。

A.每个指令周期中 CPU都至少访存一次

B. 每个指令周期一定大于或等于一个 CPU时钟周期

C.空操作指令的指令周期中任何寄存器的内容都不会被改变

D.当前程序在每条指令执行结束时都可能被外部中断打断

由于不采用指令预取技术,每个指令周期都需要取指令;而不采用Cache 技术,因此每次取指令都至少要访存一次(当指令字长与存储字长相等且按边界对齐时),A正确。时钟周期是CPU的最小时间单位,每个指令周期一定大于或等于一个 CPU 时钟周期,B正确。即使是空操作指令,在取指操作结束后,PC也会自动加1,C错误。由于机器处于**“开中断”状态,在每条指令执行结束时都可能被外部中断打断**。

5.3 数据通路的功能和基本结构

2015-2023年共考察单选题3题,涉及大题4道。

5.3.1 数据通路的功能

CPU的内部结构由 数据通路(Data Path) 和 控制部件(Control Unit) 两大部分组成。

数据通路:数据在指令执行过程中所经过的路径,包括路径上的部件。

ALU、通用寄存器、状态寄存器、异常和中断处理逻辑等都是指令执行时数据流经的部件,都属于数据通路的一部分。

数据通路描述了信息从哪里开始,中间经过哪些部件,最后被传送到哪里。

数据通路由控制部件控制,控制部件根据每条指令功能的不同,生成对数据通路的控制信号。

5.3.2 数据通路的组成

组成数据通路的元件主要分为组合逻辑元件和时序逻辑元件两类。

1.组合逻辑元件(操作元件)

任何时刻产生的输出仅取决于当前的输入。组合电路不含存储信号的记忆单元,也不受时钟信号的控制,输出与输入之间无反馈通路,信号是单向传输的。

数据通路中常用的组合逻辑元件有加法器、算术逻辑单元(ALU)、译码器、多路选择器、三态门等。

译码器可用于操作码或地址码译码,n 位输入对应2^n种不同组合。

多路选择器(MUX) 需要控制信号 Select 来确定选择哪个输入被输出。

三态门可视为一种控制开关,由控制信号 EN 决定信号线的通断,当 EN =1时,三态门被打开,输出信号等于输入信号;当EN=0时,输出端呈高阻态(隔断态),所连寄存器与总线断开。

2.时序逻辑元件(状态元件)

任何时刻的输出不仅与该时刻的输入有关,还与该时刻以前的输入有关,因而时序电路必然包含存储信号的记忆单元。

此外,时序电路必须在时钟节拍下工作。各类寄存器和存储器,如通用寄存器组、程序计数器、状态/移位暂存/锁存寄存器等,都属于时序逻辑元件。

5.3.3 数据通路的基本结构

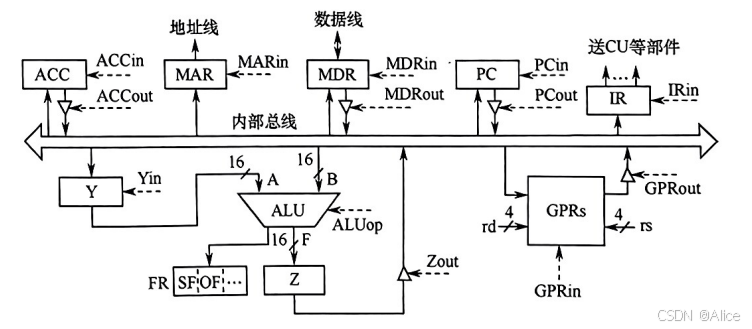

1.CPU内部单总线方式

将ALU及所有寄存器都连接到一条内部公共总线上。结构比较简单,数据传输存在较多的冲突现象,性能较低。

GPRs为通用寄存器组,rs、rd分别为所读、写的通用寄存器的编号;

Y和Z为暂存器;

FR为标志寄存器,用于存放ALU产生的标志信息。

带箭头的虚线表示控制信号,字母加“in”表示该部件允许写入,字母加“out”表示该部件允许输出。例如MDRin表示内部总线上信息写入MDR,MDRout 表示 MDR 的内容送入内部总线。

能输出到总线的部件均通过一个三态门与内部总线相连,用于控制该部件与内部总线之间数据通路的连接与断开。

注意:单周期处理器(CPI=1)不能采用单总线方式,因为单总线将所有寄存器都连接到一条公共总线上,一个时钟内只允许一次操作,无法完成一条指令的所有操作。

2.CPU内部多总线方式

CPU 内部有两条或更多的总线时,构成双总线结构或多总线结构,效率高。

3.专用数据通路方式

根据指令执行过程中的数据和地址的流动方向安排连接电路,避免使用共享的总线,性能较高,但硬件量大。

注意:

内部总线是指同一部件,如CPU内部连接各寄存器及运算部件之间的总线;

系统总线是指同一台计算机系统的各部件,如CPU、内存和各类I/O接口间互相连接的总线。

5.3.4 数据通路的操作举例

总线是一组共享的传输信号线,它不能存储信息,任一时刻也只能有一个部件把信息送到总线上。下面以图5.8所示的单总线数据通路为例,介绍一些常见操作的流程及控制信号。

1.通用寄存器之间传送数据

在寄存器和总线之间有两个控制信号:Rin和Rout。当Rin有效时,控制将总线上的信息存到寄存器 R中;当 Rout有效时,控制将寄存器R的内容送至总线。

下面以程序计数器 PC 为例,将 PC的内容送至 MAR。实现该操作的流程及控制信号为 (PC)→MAR,PCout和 MARin有效,PC内容→MAR

2、从主存读取数据

从主存中读取的信息可能是数据或指令,现以 CPU 从主存中取指令为例,实现该操作的流程及控制信号为

第一步,将 PC的内容通过内部总线送至MAR,需要1个时钟周期。

(PC)→MAR,PCout 和 MARin 有效,现行指令地址→MAR

第二步,CU 向主存发出读命令,从 MAR所指主存单元读取一个字,并送至MDR;同时 PC加 1为取下一条指令做准备,需要1个主存周期。

MEM(MAR)→MDR,(PC)+1→PC,MDRin 有效,CU发出读命令,取出指令后 PC+1

第三步,将 MDR的内容通过内部总线送至IR,需要1个时钟周期。

(MDR)→IR,MDRout 和 IRin有效,现行指令→IR

3.将数据写入主存

将寄存器 R1的内容写入寄存器 R2 所指的主存单元:

(R1)→MDR,Rlout和MDRin有效

(R2)→MAR,R2out和 MARin 有效

MDR→MEM(MAR),MDRout 有效,CU发出写命令

4.执行算术或逻辑运算

在单总线数据通路中,每一时刻总线上只有一个数据有效。由于 ALU 是一个没有存储功能的组合逻辑元件,在其执行运算时必须保持两个输入端同时有效,因此先将一个操作数经内部总线送入暂存器Y保存,Y的内容在ALU 的左输入端始终有效,再将另一个操作数经内部总线直接送到ALU 的右输入端。

此外,ALU 的输出端也不能直接与总线相连,否则其输出会通过总线反馈到输入端,影响运算结果,因此将运算结果暂存在暂存器 Z 中。

加法指令ADD ACC,R1,实现将ACC的内容和R1的内容相加并写回ACC,完成该操作的流程及控制信号为:

(R1)→Y,Rlout 和Yin有效,操作数→Y

(ACC)+(Y)→Z,ACCout 和ALDin有效,CU向ALU 发出加命令,结果→Z

(Z)→ACC,Zout 和 ACCin有效,结果→ACC

以上3步不能同时执行,否则会引起总线冲突,因此该操作需要3个时钟周期。

5.修改程序计数器的值

转移指令通过修改程序计数器PC的值来达到转跳的目的。

转移指令JMPaddr, addr 为目标转移地址,实现将IR中的地址字段写入PC,完成该操作的流程及控制信号为: Ad (IR)→PC,IRout 和 PCin有效。

数据通路结构直接影响 CPU 内各种信息的传送路径,数据通路不同,指令执行过程的微操作序列的安排也不同,它关系着微操作信号形成部件的设计。

5.3.5 历年真题 (大题)

2009

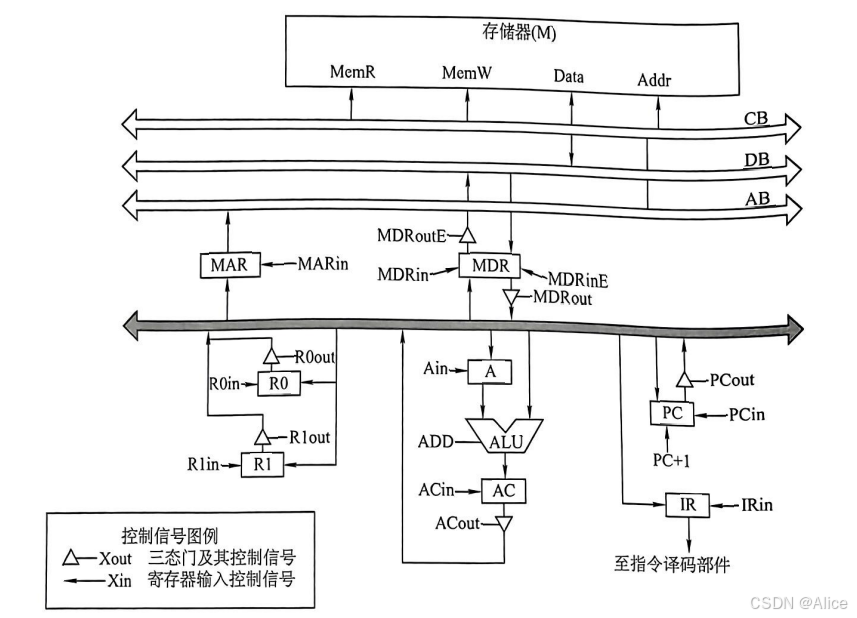

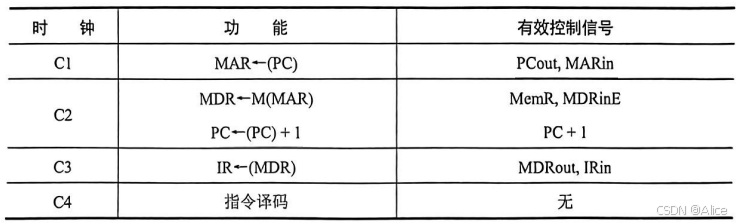

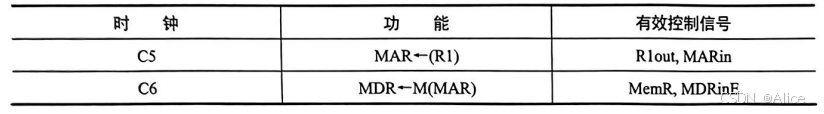

某计算机字长16位,采用16位定长指令字结构,部分数据通路结构如下图所示。

图中所有控制信号为 1 时表示有效,为 0 时表示无效。例如,控制信号MDRinE为1表示允许数据从DB打入MDR,MDRin为1表示允许数据从总线打入MDR。

假设 MAR的输出一直处于使能状态。加法指令“ADD(RI),R0”的功能为(R0)+((R1))→(R1),即将R0中的数据与R1的内容所指主存单元的数据相加,并将结果送入R1的内容所指主存单元中保存。

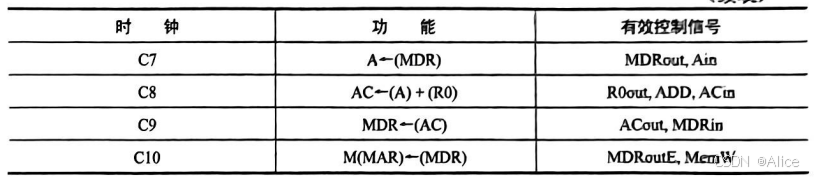

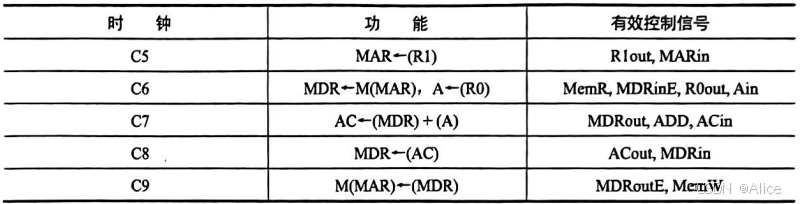

下表给出了上述指令取指和译码阶段每个节拍(时钟周期)的功能和有效控制信号,请按表中描述方式用表格列出指令执行阶段每个节拍的功能和有效控制信号。

解:取指令的功能是根据 PC的内容所指的主存地址,取出指令代码,经过MDR,最终送至IR。这部分和后面的指令执行阶段的取操作数、存运算结果的方法是相通的。

C1:(PC)→MAR 在读/写存储器前,必须先将地址(这里为(PC))送至MAR。

C2:M(MAR)→MDR,(PC)+1→PC 读/写的数据必须经过 MDR,指令取出后PC自增1。

C3:(MDR)→IR 然后将读到的 MDR 中的指令代码送至IR 进行后续操作。

指令“ADD(R1),R0”的操作数一个在主存中,一个在寄存器中,运算结果在主存中。根据指令功能,要读出R1的内容所指的主存单元,必须先将R1的内容送至MAR,即(R1)→MAR。而读出的数据必须经过 MDR, 即(MAR)→MDR。

因此,将R1的内容所指的主存单元的数据读出到MDR的节拍安排如下:

C5:(R1)→MAR

C6;M(MAR)→MDR

ALU一端是寄存器 A,MDR或R0中必须有一个先写入A中,如MDR。C7:(MDR)→A

然后执行加法操作,并将结果送入寄存器 AC。C8:(A)+(R0)→AC

之后将加法结果写回到R1的内容所指的主存单元,注意 MAR中的内容没有改变。

C9:(AC)→MDR

C10:(MDR)→M(MAR)

本题答案不唯一,若在C6执行M(MAR)→MDR的同时,完成(R0)→A(即选择将(R0)写入A),并不会发生总线冲突,这种方案可节省1个节拍,见下表。

2015

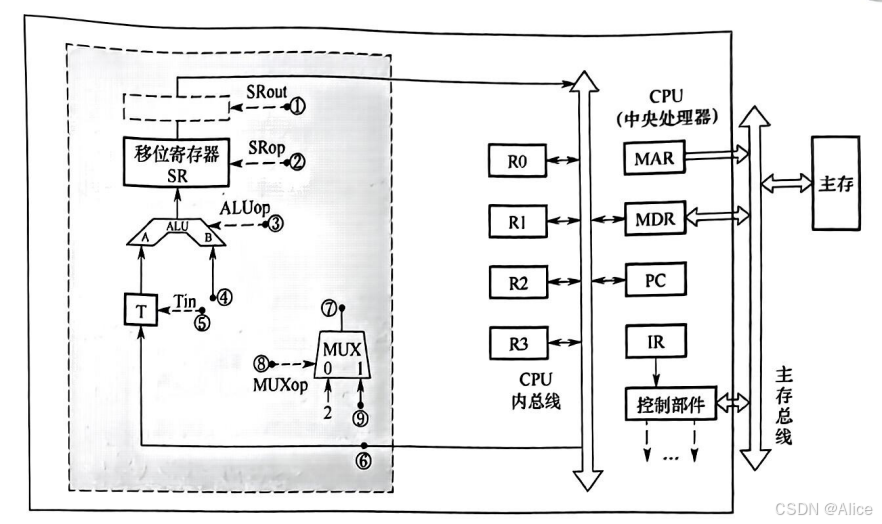

某16位计算机的主存按字节编码,存取单位为16位;采用16位定长指令字格式;

CPU采用单总线结构,主要部分如下图所示。图中R0~R3为通用寄存器;T为暂存器;

SR为移位寄存器,可实现直送(mov)、左移一位(left)和右移一位(right)三种操作,控制信号为SRop,SR的输出由信号SRout控制;

ALU可实现直送A(mova)、A加B(add)、A减B(sub)、A与B(and)、A或B(or)、非A(not)、A加1(inc)七种操作、控制信号为ALUop.

1)图中哪些寄存器是程序员可见的?

为何要设置暂存器T?

解:程序员可见寄存器为通用寄存器(R0~R3)和 PC。

因为采用了单总线结构,因此若无暂存器T, 则ALU的A、B端口会同时获得两个相同的数据,使数据通路不能正常工作。

2)控制信号ALUop和SRop的位数至少各是多少?

解:ALU 共有7种操作,其操作控制信号ALUop至少需要3位;

移位寄存器有3种操作,其操作控制信号 SRop至少需要2位。

3)控制信号 SRout所控制部件的名称或作用是什么?

解:信号 SRout 所控制的部件是一个三态门,用于控制移位器与总线之间数据通路的连接与断开。

4)端点①~⑨中,哪些端点须连接到控制部件的输出端?

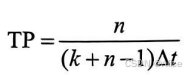

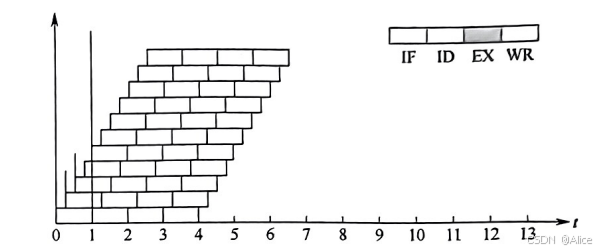

解:端口①、②、③、⑤、⑧须连接到控制部件输出端(即所有虚线)。

(即都是OP,OUT,IN等用于控制的信息,而不是计算器的输入数据等信息。)

5)为完善单总线数据通路,需要在端点①~⑨中相应的端点之间添加必要的连线。写出连线的起点和终点,以正确表示数据的流动方向。

解:连线1,⑥→⑨;连线2,⑦→④。WHY

6)为什么二路选择器 MUX的一个输入端是2?

解:因为每条指令的长度为16位,按字节编址,所以每条指令占用2个内存单元,顺序执行时,下条指令地址为(PC)+2。MUX的一个输入端为2,可便于执行(PC)+2 操作。

2022

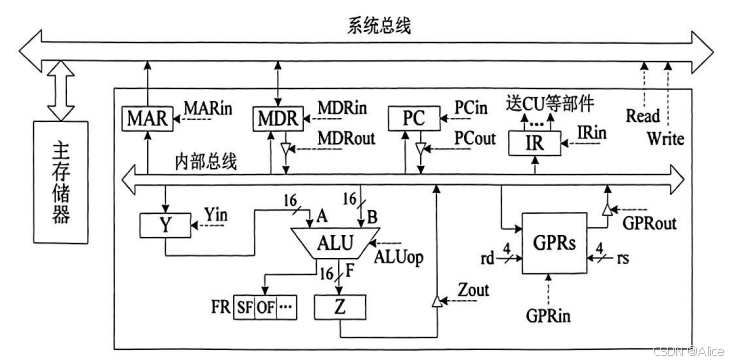

某CPU中部分数据通路如下图所示,其中,GPRs为通用寄存器组;FR为标志寄存器,用于存放ALU产生的标志信息;带箭头虚线表示控制信号,如控制信号Read、Write分别表示主存读、主存写,MDRin表示内部总线上的数据写入MDR,MDRout 表示MDR的内容送给内部总线。

请回答下列问题:

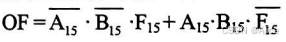

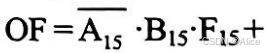

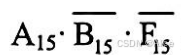

1)设 ALU的输入端 A、B及输出端F的最高位分别为A15、B15及F15,FR中的符号标志和溢出标志分别为SF和OF, 则SF的逻辑表达式是什么? A加B、A减B时OF的逻辑表达式分别是什么? 要求逻辑表达式的输入变量为A15、B15及F15。

解:符号标志 SF表示运算结果的正负性,因此 SF=F15(最高位)。

对于加法运算,当A、B为负且F为正,或A、B为正且F为负时,说明发生溢出。因此溢出标志为:

对于减法运算,当A为负、B为正,且F为正,或A为正、B为负,且F为负,说明发生溢出。因此溢出标志为:

2)为什么要设置暂存器Y和Z?

解:因为在单总线结构中,每一时刻总线上只有一个数据有效,而ALU有两个输入端和一个输出端。因此,当ALU 运算时,需要先用暂存器Y缓存其中一个输入端的数据,再通过总线传送另一个输入端的数据。

与此同时,ALU 的输出端产生运算结果,但由于总线正被占用,因此需要暂存器 Z,以缓存 ALU 的输出端数据。

3)若GPRs的输入端 rs、rd分别为所读、写的通用寄存器的编号,则 GPRs中最多有多少个通用寄存器?

rs和rd来自图中的哪个寄存器?

已知 GPRs内部有一个地址译码器和一个多路选择器,rd 应连接地址译码器还是多路选择器?

解:由图可知,rs和rd都是4bit,因此GPRs中最多有2^4=16个通用寄存器;

rs和rd来自指令寄存器IR;(是指令信息的一部分)

rd 表示寄存器编号,应连接地址译码器以解析收到的寄存器编号。

4)取指令阶段(不考虑PC增量操作)的控制信号序列是什么?

若从发出主存读指令到主存读出数据并传送到MDR共需5个时钟周期,则取指令阶段至少需要几个时钟周期?

解:取指阶段需要根据程序计数器PC取出主存中的指令,并将指令写入指令寄存器IR中。控制信号序列如下:

①PCout,MARin //将指令的地址写入MAR

②Read //读主存,并将读出的数据写入MDR

③MDRout,IRin 1/将MDR的内容写入指令寄存器 IR

步骤①需要1个时钟周期,步骤②需要5个时钟周期,步骤③需要1个时钟周期,因此取指令阶段至少需要7个时钟周期。

5)图中控制信号由什么部件产生?

图中哪些寄存器的输出信号会连到该部件的输入端?

解:图中控制信号由控制部件(CU)产生。

指令寄存器IR和标志寄存器FR的输出信号会连到控制部件的输入端。

5.4 控制器的功能和工作原理

2015-2023年共考察单选题6题,涉及大题5道。

取指周期 FE / 间址周期 IND / 执行周期 EX / 中断周期 INT

F - Fetch

5.4.1 控制器的结构和功能

1)运算器部件通过数据总线与内存储器、输入设备和输出设备传送数据。

2)输入设备和输出设备通过接口电路与总线相连接。

3)内存储器、输入设备和输出设备从地址总线接收地址信息,从控制总线得到控制信号,通过数据总线与其他部件传送数据。

4)控制器部件从数据总线接收指令信息,从运算器部件接收指令转移地址,送出指令地址到地址总线,还要向系统中的部件提供它们运行所需要的控制信号。

控制器的主要功能:

1)从主存中取出一条指令,并指出下一条指令在主存中的位置。

2)对指令进行译码或测试,产生相应的操作控制信号,以便启动规定的动作。

3)指挥并控制 CPU、主存、输入设备和输出设备之间的数据流动方向。

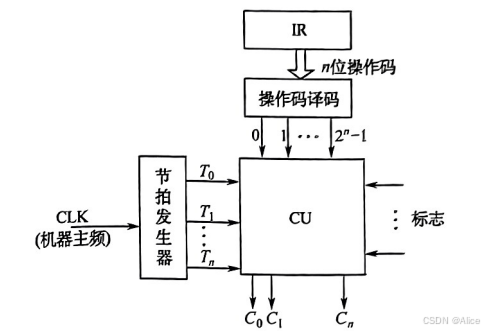

根据控制器产生微操作控制信号的方式的不同,控制器可分为硬布线控制器和微程序控制器,两类控制器中的PC和IR是相同的,但确定和表示指令执行步骤的办法及给出控制各部件运行所需要的控制信号的方案是不同的。

5.4.2 硬布线控制器

由复杂的组合逻辑门电路和触发器构成,也称组合逻辑控制器。

其原理是根据指令的要求、当前的时序及内外部的状态,按时间的顺序发送一系列微操作控制信号。

指令的操作码是决定控制单元(CU)发出不同控制信号的关键。

控制单元(CU)的输入信号来源如下:

1)经指令译码器译码产生的指令信息。现行指令的操作码决定了不同指令在执行周期所需完成的不同操作,它与时钟配合产生不同的控制信号。

2)时序系统产生的机器周期信号和节拍信号。为了使控制单元按一定的先后顺序、一定的节奏发出各个控制信号,控制单元必须受时钟控制。

3)来自执行单元的反馈信息即标志。控制单元有时需依赖CPU当前所处的状态产生控制信号,如 BAN指令,控制单元要根据上条指令的结果是否为负来产生不同的控制信号。

硬布线控制的功能由逻辑门组合实现,其速度主要取决于电路延迟,因此高速计算机中的关键核心部件 CPU 往往采用硬布线逻辑实现。因此,RISC一般都选用硬布线控制器。

硬布线控制器的控制信号先用逻辑式列出,经化简后用电路来实现,因此显得零乱复杂,当需要修改或增加指令时就必须重新设计电路,非常麻烦。

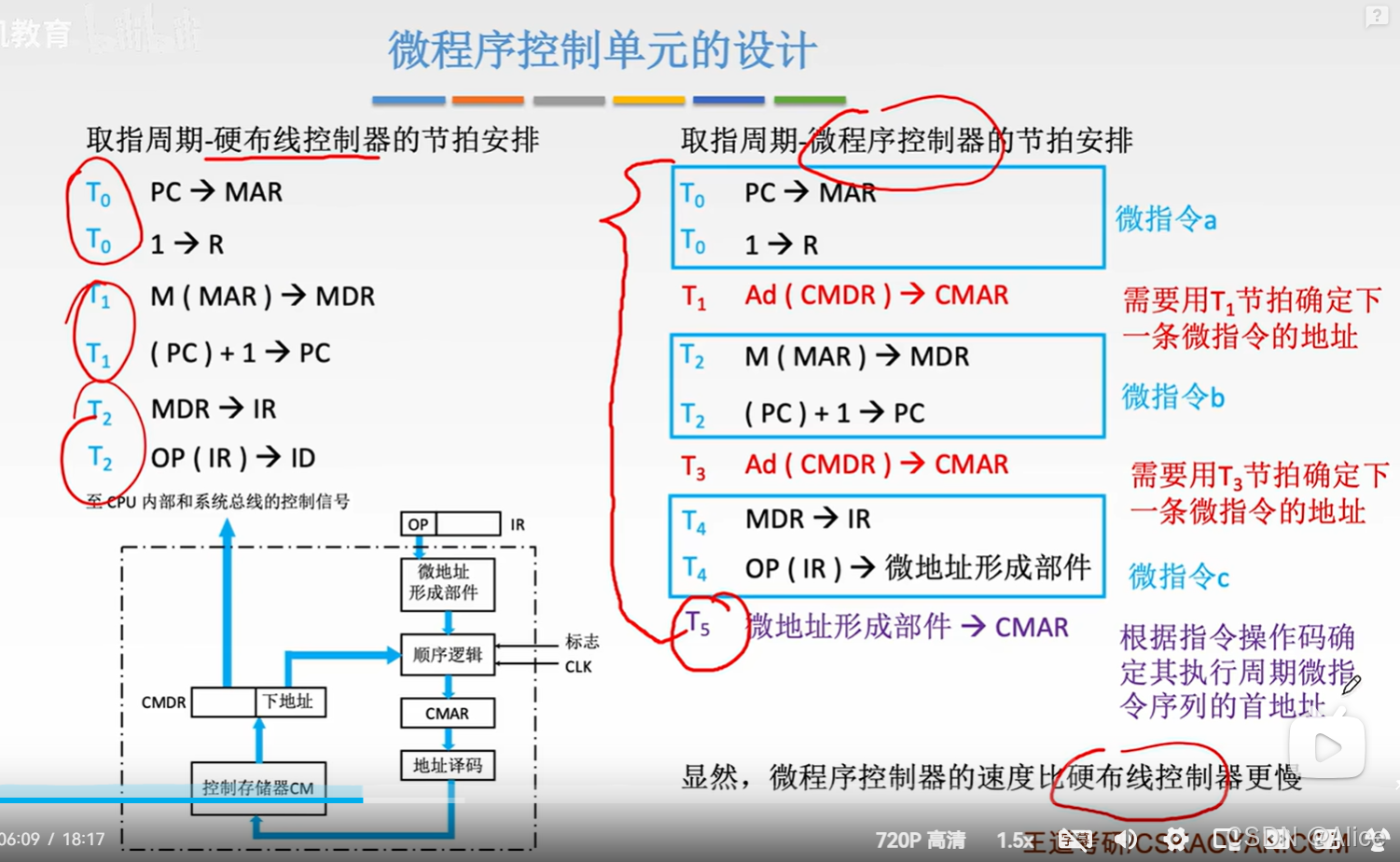

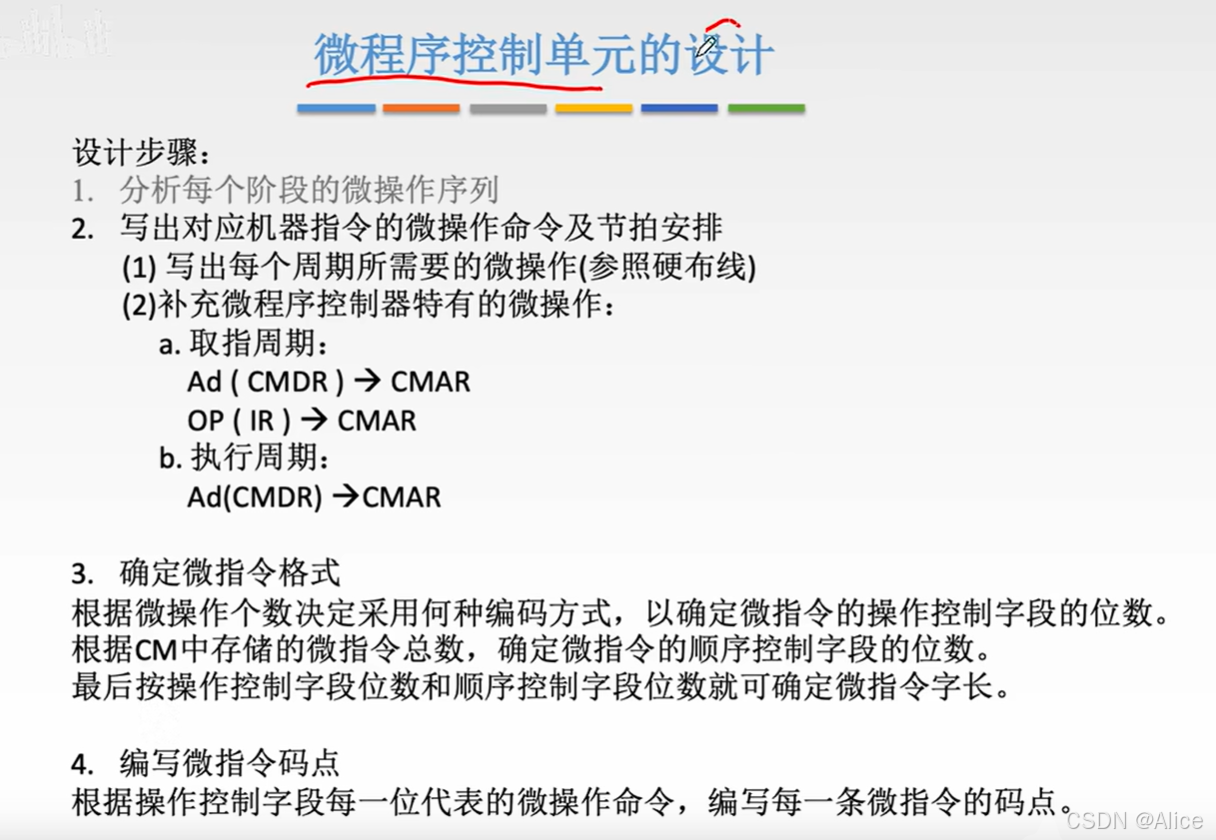

5.4.3微程序控制器

微程序控制器采用存储逻辑实现,也就是将微操作信号代码化,使每条机器指令转化成为一段微程序并存入一个专门的存储器(控制存储器)中,微操作控制信号由微指令产生。

5.4.3.1 微程序控制的基本概念

微程序的设计思想就是将每条机器指令编写成一个微程序,每个微程序包含若干微指令,每条微指令对应一个或几个微操作命令。

因此,执行一条指令的过程就是执行一个微程序的过程,这些微程序存储在一个控制存储器中。目前,大多数计算机都采用微程序设计技术。

微程序设计技术涉及的基本术语:

(1)微命令与微操作

微命令:在微程序控制的计算机中,控制部件向执行部件发出的各种控制命令称为微命令,它是构成控制序列的最小单位。

例如,打开或关闭某个控制门的电位信号、某个寄存器的打入脉冲等。执行部件收到微命令后所进行的操作称为微操作,微命令和微操作是一一对应的。

微命令有相容性和互斥性之分。相容性微命令是指那些可以同时出现、共同完成某一些微操作的微命令;而互斥性微命令是指在机器中不允许同时出现的微命令。

注意:硬布线控制器中也有微命令与微操作的概念,并非微程序控制器的专有概念。

(2)微指令与微周期

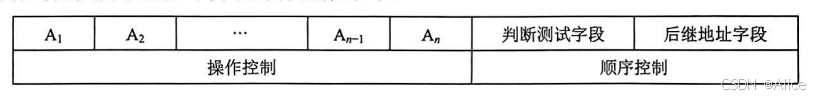

微指令:若干微命令的集合,一条微指令通常至少包含两大部分信息:

①操作控制字段,也称微操作码字段,用于产生某一步操作所需的各种操作控制信号。

② 顺序控制字段,也称微地址码字段,用于控制产生下一条要执行的微指令地址。

微周期:从控制存储器中取出并执行一条微指令所需的全部时间,通常为一个时钟周期。

(3)主存储器与控制存储器

主存储器用于存放程序和数据,在CPU外部,用RAM实现。

控制存储器(CM)用于存放微程序,在CPU内部,用ROM实现。存放微指令的控制存储器的单元地址称为微地址。

(4)程序与微程序

程序是指令的有序集合,用于完成特定的功能。

微程序是微指令的有序集合,用于描述机器指令,一条指令的功能由一段微程序来实现。微程序实际上是机器指令的实时解释器,是由计算机设计者事先编制好并存放在控制存储器中的,一般不提供给用户。

对于程序员来说,系统中微程序的结构和功能是透明的,无须知道。程序最终由机器指令组成,并且由软件设计人员事先编制好并存放在主存储器或者辅助存储器中。

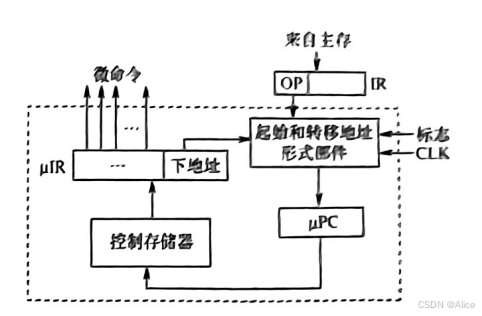

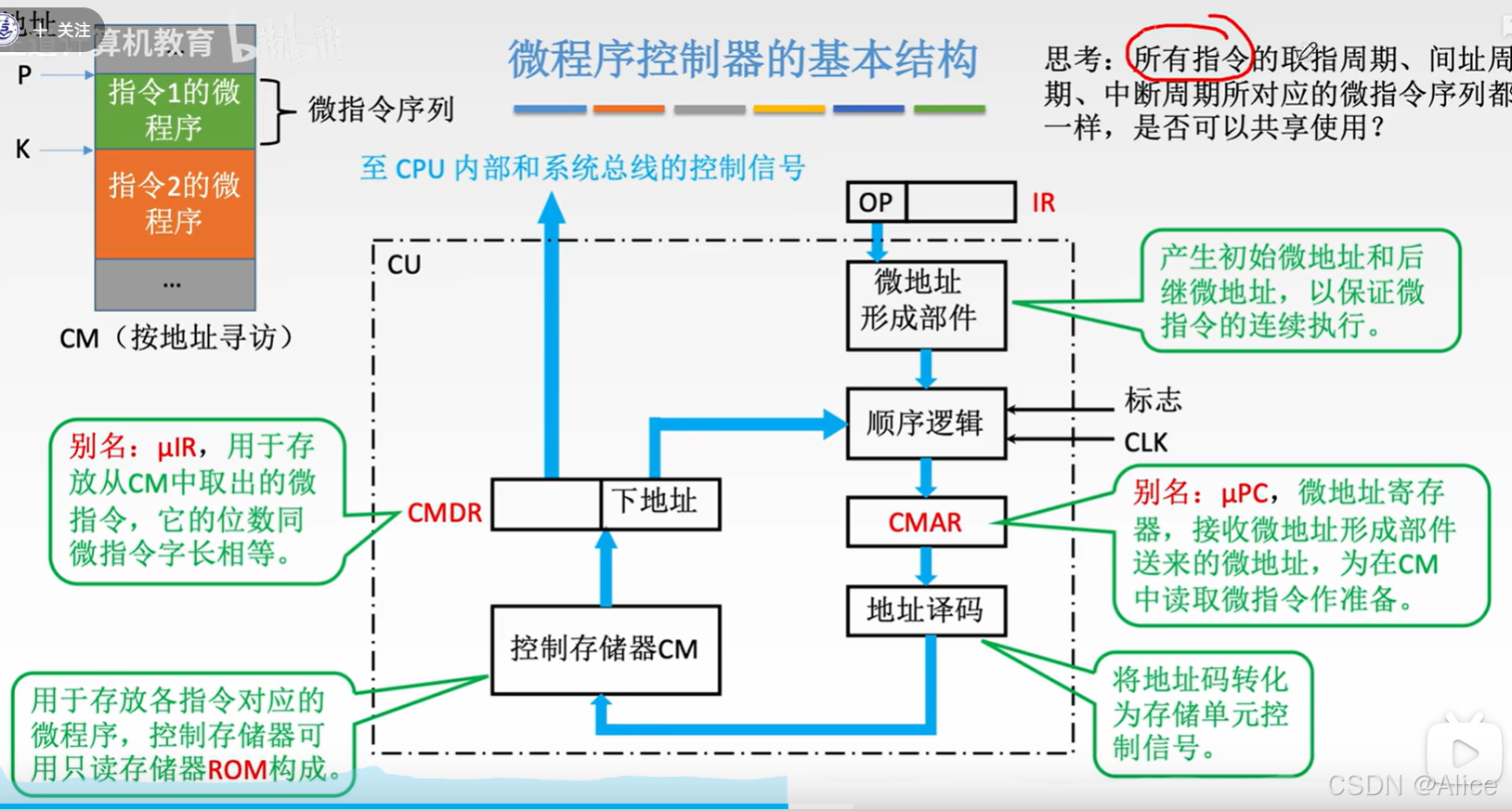

5.4.3.2 微程序控制器的组成和工作过程

(1)微程序控制器的基本组成

① 起始和转移地址形成部件(或简称微地址形成部件)。用于产生初始和后继微地址,以保证微指令的连续执行。

② 微指令地址寄存器。接收微地址形成部件送来的微地址,为读取微指令做准备。

③ 控制存储器。它是微程序控制器的核心部件,用于存放各指令对应的微程序。

④ 微指令寄存器。其位数等于微指令字长。

(2)微程序控制器的工作过程

在微程序控制器的控制下计算机执行机器指令的过程,可描述为:

① 执行取指令公共操作。在机器开始运行时,自动地将取指微程序的入口地址送入 μPC,并从 CM中读出相应的微指令并送入μlR。取指微程序的入口地址一般为 CM的0号单元,取指微程序执行完成后,从主存中取出的机器指令就已存入指令寄存器中。

② 由机器指令的操作码字段通过微地址形成部件产生该机器指令所对应的微程序的入口地址,并送入μPC。

③ 从CM中逐条取出对应的微指令并执行。

④执行完对应于一条机器指令的一个微程序后,又回到取指微程序的入口地址,继续第①步,以完成取下一条机器指令的公共操作。

(3)微程序和机器指令

通常,一条机器指令对应一个微程序。

由于任何机器指令的取指令操作都是相同的,因此可将取指令操作的微命令统一编成一个微程序,这个微程序只负责将指令从主存单元中取出并送至指令寄存器。此外,也可编写出对应间址周期的微程序和中断周期的微程序。

这样,控制存储器中的微程序个数应为机器指令数再加上对应取指、间址和中断周期等公共的微程序数。

5.4.3.3 微指令的编码方式

也称微指令的控制方式,是指如何对微指令的控制字段进行编码,以形成控制信号。编码的目标是在保证速度的情况下,尽量缩短微指令字长。

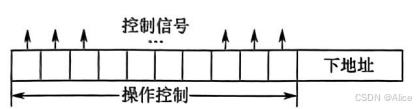

(1)直接编码(直接控制)方式

无须进行译码,微指令的操作控制字段中每一位都代表一个微命令。

选用或不选用某个微命令,只要将表示该微命令的对应位设置成1或0即可。每个微命令对应并控制数据通路中的一个微操作。

优点:简单、直观,执行速度快,操作并行性好;

缺点:微指令字长过长,n个微命令就要求微指令的操作字段有n位,造成控制存储器容量极大。

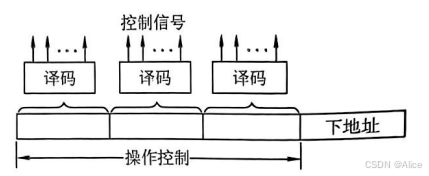

(2)字段直接编码方式

将微指令的操作控制字段分成若干小字段,把互斥性微命令放在同一字段中,把相容性微命令放在不同字段中;

每个字段独立编码,每种编码代表一个微命令且各字段编码含义单独定义,与其他字段无关。

可缩短微指令字长,但因为要通过译码电路后再发出微命令,因此比直接编码方式慢。

微命令字段分段的原则:

① 互斥性微命令分在同一段内,相容性微命令分在不同段内。

② 每个小段中包含的信息位不能太多,否则将增加译码电路的复杂性和译码时间。

③一般每个小段还要留出一个状态,表示本字段不发出任何微命令。因此,当某字段的长度为3位时,最多只能表示7个互斥的微命令,通常用000 表示不操作。

(3)字段间接编码方式

一个字段的某些微命令需由另一个字段中的某些微命令来解释,由于不是靠字段直接译码发出的微命令,因此称为字段间接编码,也称隐式编码。

进一步缩短了微指令字长,但因削弱了微指令的并行控制能力,因此通常作为字段直接编码方式的一种辅助手段。

5.4.3.4 微指令的地址形成方式

后继微地址的形成主要有以下几个基本类型:

1)由微指令的后继地址字段(也称下地址字段)指出。在微指令格式中设置一个后继地址字段,由微指令的后继地址字段直接指出后继微指令的地址,这种方式也称断定方式。

2)根据机器指令的操作码形成。当机器指令取自指令寄存器后,微指令的地址由操作码经微地址形成部件形成,该部件输出的是对应机器指令微程序的首地址。

3)增量计数器法,即(μPC)+1→μPC,适用于后继微指令地址是连续的情况。

4)根据各种标志决定下一条微指令分支转移的地址。

5)由硬件直接产生微程序入口地址。电源加电后,第一条微指令的地址可由专门的硬件电路产生,并送至μPC,这个地址即为取指周期微程序的入口地址。

5.4.3.5 微指令的格式

微指令格式与微指令的编码方式有关,通常分为水平型微指令和垂直型微指令两种。

(1)水平型微指令

直接编码、字段直接编码和字段间接编码都属于水平型微指令。

指令字中的一位对应一个控制信号,有输出时为1,否则为0。一条水平型微指令定义并执行多个并行操作的微命令。

优点:微程序短,并行能力强,执行速度快;

缺点:微指令长,编写微程序较麻烦。

(2)垂直型微指令

采用类似机器指令操作码的方式,在微指令字中设置微操作码字段。

一条垂直型微指令通常只能定义并执行一种微命令。

优点:微指令短、简单、规整,便于编写微程序;

缺点:微程序长,执行速度慢,效率低。

水平型微指令和垂直型微指令的比较如下:

① 水平型微指令并行操作能力强、效率高、灵活性强;垂直型微指令则较差。

② 水平型微指令执行一条指令的时间短;垂直型微指令执行的时间长。

③ 用水平型微指令编写的微程序,微指令字较长但微程序短;垂直型微指令正好相反。

④ 水平型微指令难以掌握;而垂直型微指令与机器指令比较相似,相对容易掌握。

5.4.3.6 硬布线和微程序控制器的特点

5.4.4 补充知识

5.5 异常和中断机制

CPU的数据通路中有相应的异常检测和响应逻辑;

外设接口中有相应的中断请求和控制逻辑;

操作系统中有相应的中断服务程序。

这些中断硬件电路和中断服务程序有机结合,共同完成异常和中断的处理过程。

5.5.1 异常和中断的基本概念

异常:由CPU 内部产生的意外事件被称为异常,有些教材中也称内中断。

中断:由来自 CPU外部的设备向CPU 发出的中断请求被称为中断,通常用于信息的输入和输出,有些教材中也称外中断。

异常是CPU执行一条指令时,由CPU在其内部检测到的、与正在执行的指令相关的同步事件;

中断是一种典型的由外部设备触发的、与当前正在执行的指令无关的异步事件。

异常和中断处理过程:

若 CPU在执行用户程序的第i条指令时检测到一个异常事件,或者执行第i条指令后发现一个中断请求信号,则 CPU 打断当前程序,然后转去执行相应的异常或中断处理程序。

若异常或中断处理程序能够解决相应的问题,则在异常或中断处理程序的最后,CPU 通过执行异常或中断返回指令,回到被打断的用户程序的第i条指令或第i+1条指令继续执行;

若异常或中断处理程序发现是不可恢复的致命错误,则终止用户程序。

通常情况下,对异常和中断的具体处理过程** 。

异常和中断的处理过程基本是相同的**,这也是有些教材将两者统称为中断的原因。

5.5.2 异常和中断的分类

1.异常的分类

分为硬故障中断和程序性异常。

硬故障中断是由硬连线出现异常引起的,如存储器校验错、总线错误等。

程序性异常也称软件中断,是指在 CPU 内部因执行指令而引起的异常事件。如整除 0、溢出、断点、单步跟踪、非法指令、栈溢出、地址越界、缺页等。

按异常发生原因和返回方式的不同,可分为故障、自陷和终止。

(1)故障(Fault)

指在引起故障的指令启动后、执行结束前被检测到的异常事件。

例如,指令译码时,出现“非法操作码”;取数据时,发生“缺段”或“缺页”;执行整数除法指令时,发现“除数为0”等。

对于“缺段”“缺页”等异常事件,经处理后,可将所需的段或页面从磁盘调入主存,回到发生故障的指令继续执行,断点为当前发生故障的指令;

对于“非法操作码”“除数为0”等,因为无法通过异常处理程序恢复故障,因此不能回到原断点执行,必须终止进程的执行。

(2)自陷(Trap)

自陷也称陷阱或陷入,它是预先安排的一种“异常”事件。

通常的做法是:事先在程序中用一条特殊指令或通过某种方式设定特殊控制标志来人为设置一个“陷阱”,当执行到被设置了“陷阱”的指令时,CPU在执行完自陷指令后,自动根据不同“陷阱”类型进行相应的处理,然后返回到自陷指令的下一条指令执行。注意,当自陷指令是转移指令时,并不是返回到下一条指令执行,而是返回到转移目标指令执行。

在x86机器中,用于程序调试**“断点设置”和单步跟踪的功能就是通过陷阱机制实现的。此外,系统调用指令、条件自陷指令(如 MIPS中的 teq、teqi、tme、tnei 等)等都属于陷阱指令,执行到这些指令时,无条件或有条件地自动调出操作系统内核程序进行执行**。

故障异常和自陷异常属于程序性异常(软件中断)。

(3)终止(Abort)

如果在执行指令的过程中发生了使计算机无法继续执行的硬件故障,如控制器出错、存储器校验错、总线错误等,那么程序将无法继续执行,只能终止,此时,调出异常服务程序来重启系统。这种异常与故障和自陷不同,不是由特定指令产生的,而是随机发生的。

终止异常和外中断属于硬件中断。

2.中断的分类

中断包括I/O 设备发出的 I/O中断(如键盘输入、打印机缺纸等),或发生某种特殊事件(如用户按 Esc 键、定时器计数时间到)等。

外部 /O 设备通过特定的中断请求信号线向 CPU 提出中断请求,CPU 每执行完一条指令就检查中断请求信号线,如果检测到中断请求,则进入中断响应周期。

(1)可屏蔽中断

指通过可屏蔽中断请求线 INTR 向 CPU 发出的中断请求。CPU 可以通过在中断控制器中设置相应的屏蔽字来屏蔽它或不屏蔽它,被屏蔽的中断请求将不被送到CPU。

(2)不可屏蔽中断

指通过专门的不可屏蔽中断请求线 NMI向CPU 发出的中断请求,通常是非常紧急的硬件故障,如电源掉电等。这类中断请求信号不可被屏蔽,以让CPU快速处理这类紧急事件。

中断和异常在本质上是一样的,但它们之间有以下两个重要的不同点:

1)“缺页”或“溢出”等异常事件是由特定指令在执行过程中产生的,而中断不和任何指令相关联,也不阻止任何指令的完成。

2)异常的检测由 CPU 自身完成,不必通过外部的某个信号通知 CPU。对于中断,CPU 必须通过中断请求线获取中断源的信息,才能知道哪个设备发生了何种中断。

注意:所有的异常和中断事件都是由硬件检测发现的。

此外,根据识别中断服务程序地址的方式,可分为向量中断和非向量中断;

根据中断处理过程是否允许被打断,还可分为单重中断和多重中断。

5.5.3 异常和中断响应过程

CPU执行指令时,如果发生了异常或中断请求,必须进行相应的处理。

从 CPU 检测到异常或中断事件,到调出相应的处理程序,整个过程称为异常和中断响应。CPU 对异常和中断响应的过程可分为:

(1)关中断

在保存断点和程序状态期间,不能被新的中断打断,因此要禁止响应新的中断,即关中断。

通常通过设置“中断允许”(IF)触发器来实现,若IF置为1,则为开中断,表示允许响应中断:若IF置为0,则表示关中断,表示不允许响应中断。

(2)保存断点和程序状态

为了能在异常和中断处理后正确返回到被中断的程序继续执行,必须将程序的断点(返回地址)送到栈或特定寄存器中。通常保存在栈中,这是为了支持异常或中断的联套。

异常和中断处理后可能还要回到被中断的程序继续执行,被中断时的程序状态字寄存器 PSW的内容也需要保存在栈或特定寄存器中,在异常和中断返回时恢复到 PSW中。

(3)识别异常和中断并转到相应的处理程序

异常和中断源的识别有软件识别和硬件识别两种方式。

异常大多采用软件识别方式,而中断可以采用软件识别方式或硬件识别方式。

软件识别方式是指 CPU 设置一个异常状态寄存器,用于记录异常原因。操作系统使用一个统一的异常或中断查询程序,按优先级顺序查询异常状态寄存器,以检测异常和中断类型,先查询到的先被处理,然后转到内核中相应的处理程序。

硬件识别方式也称向量中断,异常或中断处理程序的首地址称为中断向量,所有中断向量都存放在中断向量表中。每个异常或中断都被指定一个中断类型号。在中断向量表中,类型号和中断向量一一对应,因而可以根据类型号快速找到对应的处理程序。

整个响应过程是不可被打断的。中断响应过程结束后,CPU就从 PC中取出对应中断服务程序的第一条指令开始执行,直至中断返回,这部分任务是由CPU通过执行中断服务程序完成的,整个中断处理过程是由软/硬件协同实现的。

5.6 指令流水线

2015-2023年共考察单选题10题,涉及大题2道。

5.6.1 指令流水线的基本概念

可从两方面提高处理机的并行性:

①时间上的并行技术,将一个任务分解为几个不同的子阶段,每个子阶段在不同的功能部件上并行执行,以便在同一时刻能够同时执行多个任务,进而提升系统性能,这种方法被称为流水线技术。

②空间上的并行技术,在一个处理机内设置多个执行相同任务的功能部件,并让这些功能部件并行工作,这样的处理机被称为超标量处理机。

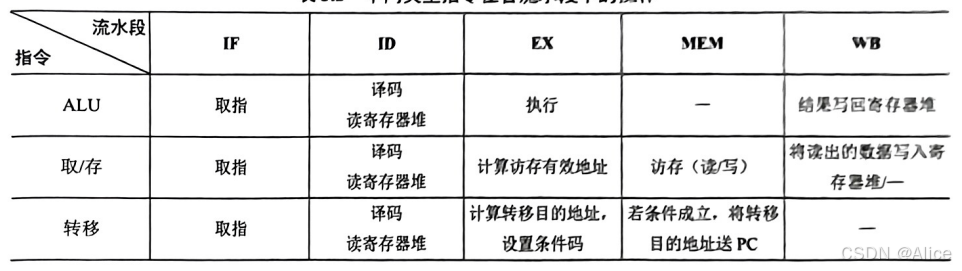

假设一条指令的执行过程分为如下5个阶段(也称功能段或流水段):

●取指(IF):从指令存储器或 Cache 中取指令。

●译码/读寄存器(ID):操作控制器对指令进行译码,同时从寄存器堆中取操作数。

●执行/计算地址(EX):执行运算操作或计算地址。

●访存(MEM):对存储器进行读/写操作。

●写回(WB):将指令执行结果写回寄存器堆。

把k+1条指令的取指阶段提前到第k条指令的译码阶段,从而将第k+1条指令的译码阶段与第k条指令的执行阶段同时进行,理想情况下,每个时钟周期都有一条指令进入流水线,每个时钟周期都有一条指令完成,每条指令的时钟周期数(即 CPI)都为1。

为了利于实现指令流水线,指令集应具有如下特征:

1)指令长度应尽量一致,有利于简化取指令和指令译码操作。否则,取指令所花的时间长短不一,使得取指部件极其复杂,并且也不利于指令译码。

2)指令格式应尽量规整,尽量保证源寄存器的位置相同,有利于在指令未知时就可取寄存器操作数,否则须译码后才能确定指令中各寄存器编号的位置。

3)采用LOAD/STORE型指令,其他指令都不能访问存储器,这样可把LOAD/STORE指令的地址计算和运算指令的执行步骤规整在同一个周期中,有利于减少操作步骤。

4)数据和指令在存储器中“按边界对齐”存放。这样,有利于减少访存次数,使所需数据在一个流水段内就能从存储器中得到。

5.6.2流水线的基本实现

1.流水线设计的原则

①指令流水段个数以最复杂指令所用的功能段个数为准;

②流水段的长度以最复杂的操作所花的时间为准。

注意:流水线方式并不能缩短单条指令的执行时间,但对于整个程序来说,执行效率得到了大幅提高。

2.流水线的逻辑结构

每个流水段后面都要增加一个流水段寄存器,用于锁存本段处理完的所有数据,以保证本段的执行结果能在下个时钟周期给下一流水段使用。

各种寄存器和数据存储器均采用统一时钟 CLK 进行同步,每来一个时钟,各段处理完的数据都将锁存到段尾的流水段寄存器中,作为后段的输入。同时,当前段也会收到前段通过流水段寄存器传递过来的数据。

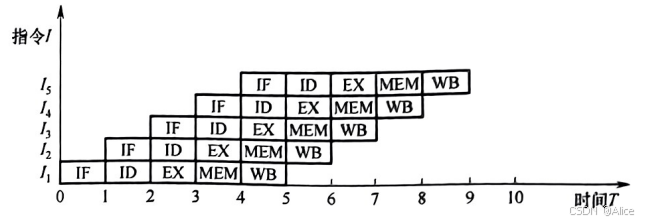

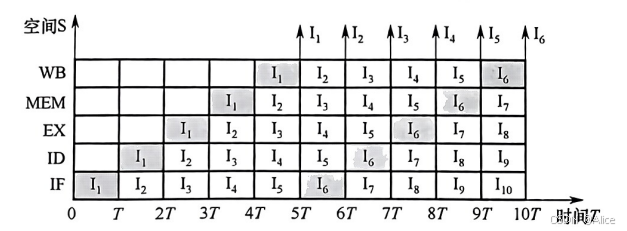

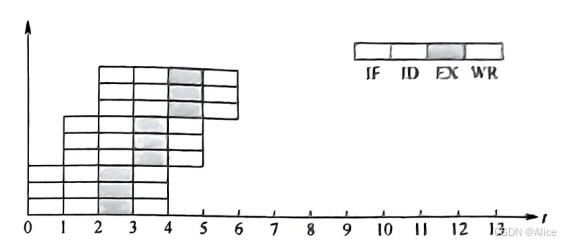

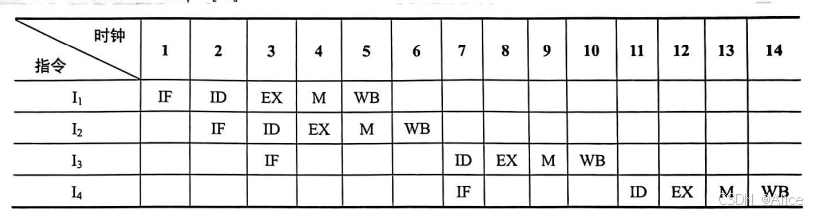

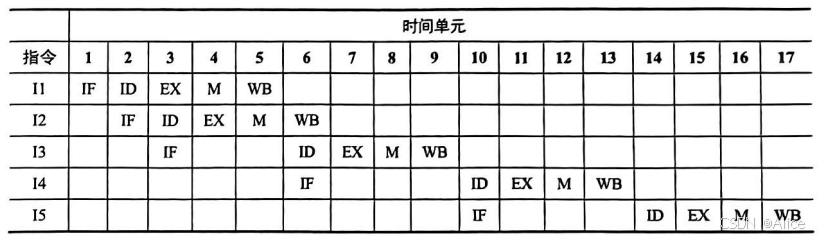

3.流水线的时空图表示

横坐标表示时间,它被分割成长度相等的时间段T;

纵坐标为空间,表示当前指令所处的功能部件。

只有大量连续任务不断输入流水线,才能充分发挥流水线的性能,而指令的执行正好是连续不断的,非常适合采用流水线技术。

对于其他部件级流水线,如浮点运算流水线,同样也仅适合于提升浮点运算密集型应用的性能,对于单个运算是无法提升性能的。

5.6.3 流水线的冒险与处理

指后续指令无法正确执行而引起流水线阻塞。

根据导致冒险的原因不同分为结构冒险、数据冒险和控制冒险3种。

1.结构冒险

由不同指令在同一时刻争用同一功能部件而形成的冲突,也称资源冲突,即由硬件资源竞争造成的冲突。

解决办法:

1)前一指令访存时,使后一条相关指令(及其后续指令)暂停一个时钟周期。

2)设置多个独立的部件。例如,对于寄存器访问冲突,可将寄存器的读口和写口独立开来;对于访存冲突,单独设置数据存储器和指令存储器。在现代 Cache 机制中,L1 级 Cache通常采用数据 Cache 和指令Cache分离的方式,从而也就避免了资源冲突的发生。

2.数据冒险

也称数据相关。即后面指令用到前面指令的结果时,前面指令的结果还没有产生。

在以非乱序执行的流水线中,所有数据冒险都是由于前面指令写结果之前,后面指令就需要读取而造成的,这种数据冒险称为写后读(Read After Write,RAW)冲突。

解决办法:

(1)延迟执行相关指令

把遇到数据相关的指令及其后续指令都暂停一至几个时钟周期,直到数据相关问题消失后再继续执行,可分为**软件插入空操作“nop”指令和硬件阻塞(stall)**两种方法。

某些情况下还可以通过将寄存器的写口和读口分别控制在前、后半个时钟周期内操作,使前半周期写入R1的值在后半周期马上被读出,在一个周期内读/写寄存器不会产生冲突。

(2)采用转发(旁路)技术

设置相关转发通路,不等前一条指令把计算结果写回寄存器,下一条指令也不再从寄存器读,而将数据通路中生成的中间数据直接转发到ALU 的输入端。

(3)load-use 数据冒险的处理

如果 load 指令与其后紧邻的运算类指令存在数据相关问题,则无法通过转发技术来解决,通常把这种情况称为load-use数据冒险。

解决方法:由编译器在第二条指令前插入一条 nop 指令,最好的办法是在程序编译时进行优化,通过调整指令顺序以避免出现 load-use 现象。

3.控制冒险

指令通常是顺序执行的,但当遇到改变指令执行顺序的情况,例如执行转移或返回指令、发生中断或异常时,会改变PC值,从而造成断流,也称控制冲突。

对于由转移指令引起的冲突,最简单的处理方法就是推迟后续指令的执行。通常把因流水线阻塞带来的延迟时钟周期数称为延迟损失时间片C。

解决方法:

1)对于由转移指令引起的冲突,可采用和解决数据冲突相同的软件插入“nop”指令和硬件阻塞(stall)的方法。比如,延迟损失多少时间片,就插入多少条nop指令。