1、为什么会出现互补的CMOS反相器?

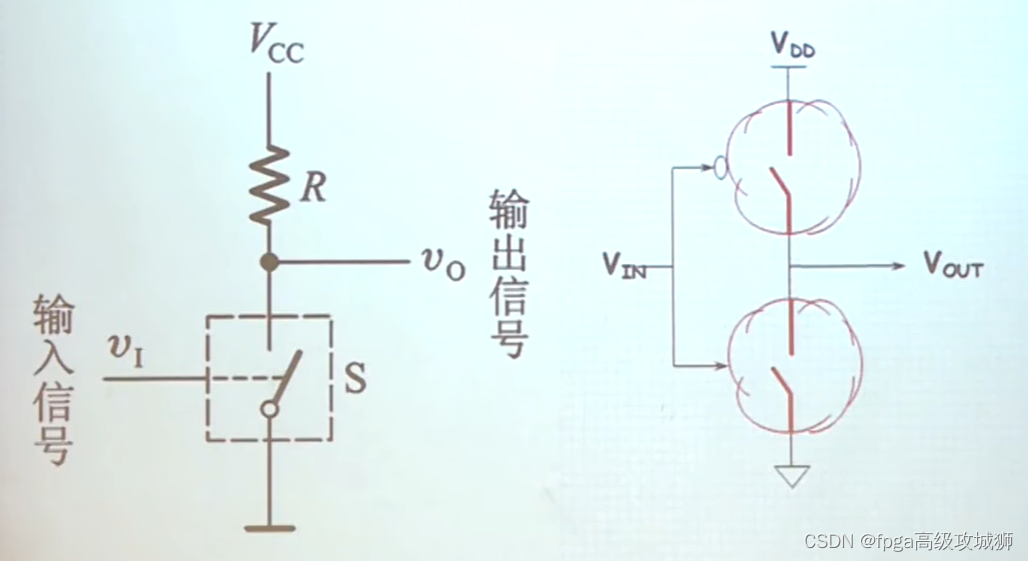

图一是得到输出低电平 0 和高电平 1 的基础电路:

当输出0时,希望R无穷大,减少功耗;

当输出1时,希望R适当小,提高带负载能力。但是电阻R是一个限流电阻,必须要有。

这就要求R在输出高低电平时是一个可变的(仅仅是一个电阻不可行)

图二是最理想的电路,当需要0时,拉到地;当需要1时,拉到电源

这就需要两个反向的开关,一个P沟道和一个N沟道的MOSFET正好符合其条件

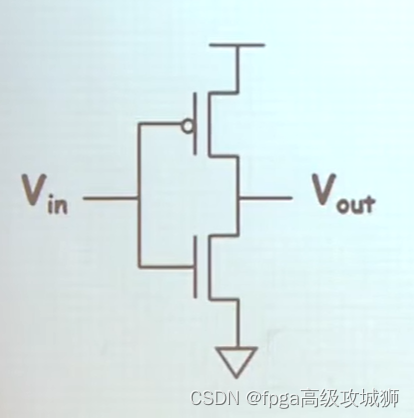

这种结构保证了输出是最高质量的0或1

当Vin为0时,上边的管子导通,下边的截至(等效电阻非常大),Vout输出高电平

当Vin为1时,下边的管子导通,上边的截至(等效电阻非常大),Vout输出低电平

文章详细解释了互补CMOS反相器如何通过可变电阻和MOSFET实现高质量的逻辑输出,强调了CMOS电路的低功耗特性、输入噪声容限、静态和动态功耗,以及输出特性和扇出的概念。

文章详细解释了互补CMOS反相器如何通过可变电阻和MOSFET实现高质量的逻辑输出,强调了CMOS电路的低功耗特性、输入噪声容限、静态和动态功耗,以及输出特性和扇出的概念。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

8663

8663

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?