3.1.3 Arithmetic Circuits

3.1.3.1 Half adder

问题陈述:

创建一个半加器。半加器将两位相加(没有进位)并产生和和进位。

Verilog代码:

module top_module(

input a, b,

output cout, sum );

assign cout=a&b;

assign sum=a^b;

endmodule

3.1.3.2 Full adder

问题陈述:

创建一个全加器。全加器将三位相加(包括进位)并产生和和进位。

Verilog代码:

module top_module(

input a, b, cin,

output cout, sum );

assign {cout,sum}=a+b+cin;

endmodule

3.1.3.3 3-bit binary adder

问题陈述:

现在您已经知道如何构建一个全加器,创建 3 个实例来创建一个 3 位二进制波纹进位加法器。加法器将两个 3 位数字和一个进位相加以产生一个 3 位和并进位。为了鼓励您实际实例化全加器,还要输出纹波进位加法器中每个全加器的进位。cout[2] 是最后一个全加器的最终进位,也是您通常看到的进位。

Verilog代码:

module top_module(

input [2:0] a, b,

input cin,

output [2:0] cout,

output [2:0] sum );

mode_fadd d1 (.a(a[0]),.b(b[0]),.cin(cin),.cout(cout[0]),.sum(sum[0]));

mode_fadd d2 (.a(a[1]),.b(b[1]),.cin(cout[0]),.cout(cout[1]),.sum(sum[1]));

mode_fadd d3 (.a(a[2]),.b(b[2]),.cin(cout[1]),.cout(cout[2]),.sum(sum[2]));

endmodule

module

mode_fadd (input a,input b,

input cin,

output cout,

output sum);

assign {cout,sum}=a+b+cin;

endmodule

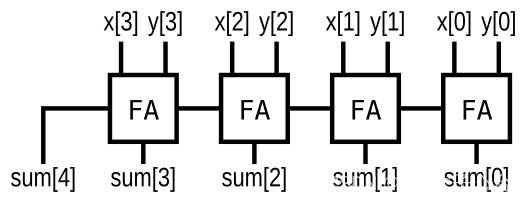

3.1.3.4 Adder

问题陈述:

实现以下电路:

Verilog代码:

module top_module (

input [3:0] x,

input [3:0] y,

output [4:0] sum);

assign sum=x+y;

endmodule

3.1.3.5 Signed addition overflow

问题陈述:

假设您有两个 8 位 2 的补码,a[7:0] 和 b[7:0]。这些数字相加产生 s[7:0]。还要计算是否发生了(有符号的)溢出。

Verilog代码:

module top_module (

input [7:0] a,

input [7:0] b,

output [7:0] s,

output overflow

); //

assign s=a+b;

assign overflow=~a[7]&&~b[7]&&s[7]||a[7]&&b[7]&&~s[7];

endmodule

两个正数会产生或两个负数相加时,会产生有符号的溢出。

~a[7]&& ~b[7] && s[7]:验证正正相加的符号溢出;

a[7]&& b[7] &&~s[7]:验证负负相加的符号溢出。

3.1.3.6 100-bit binary adder

问题陈述:

创建一个 100 位二进制加法器。加法器将两个 100 位数字和一个进位相加,产生一个 100 位和并执行。

Verilog代码:

module top_module(

input [99:0] a, b,

input cin,

output cout,

output [99:0] sum );

assign {cout,sum}=a+b+cin;

endmodule

3.1.3.7 4-digit BCD adder

问题陈述:

为您提供了一个名为bcd_fadd的 BCD(二进制编码的十进制)一位加法器,它将两个 BCD 数字和进位相加,并产生一个和和进位。

module bcd_fadd (

input [3:0] a,

input [3:0] b,

input cin,

output cout,

output [3:0] sum ); 实例化 4 个bcd_fadd副本以创建一个 4 位 BCD 波纹进位加法器。您的加法器应该将两个 4 位 BCD 数字(打包成 16 位向量)和一个进位相加,以产生一个 4 位和并执行。

Verilog代码:

module top_module (

input [15:0] a, b,

input cin,

output cout,

output [15:0] sum );

wire w1,w2,w3;

bcd_fadd di(a[3:0],b[3:0],cin,w1,sum[3:0]);

bcd_fadd d2(a[7:4],b[7:4],w1,w2,sum[7:4]);

bcd_fadd d3(a[11:8],b[11:8],w2,w3,sum[11:8]);

bcd_fadd d4(a[15:12],b[15:12],w3,cout,sum[15:12]);

endmodule

2503

2503

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?