目录

(1)定义

在FPGA设计当中,计数器与状态机是必备的技能,几乎在所有的时序逻辑设计当中,处处有它们两个的身影。可以这样说,掌握了计数器与状态机,你就具备了自己查看技术文档编码的能力。

状态机,即为数字电路技术基础课程里的状态图。因为时序电路的本质我们可以转化为状态之间的转换,因此FPGA当中的状态机设计也是我们需要掌握的技能之一。

(2)分类

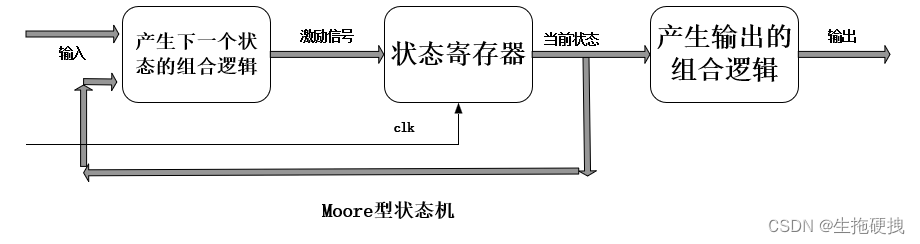

Moore型状态机

Moore型状态机的特点是输出仅与当前状态有关,与当前输入无关。这意味着在Moore型状态机中,输出会在一个完整的时钟周期内保持稳定,即使输入信号在该周期内有变化,输出也不会改变,输入对输出的影响要到下一个时钟周期才能反映出来。Moore型状态机通常响应较慢,但是在某些情况下可以避免由于输入信号的瞬时变化导致的误触发,因此它在设计上更为稳定。

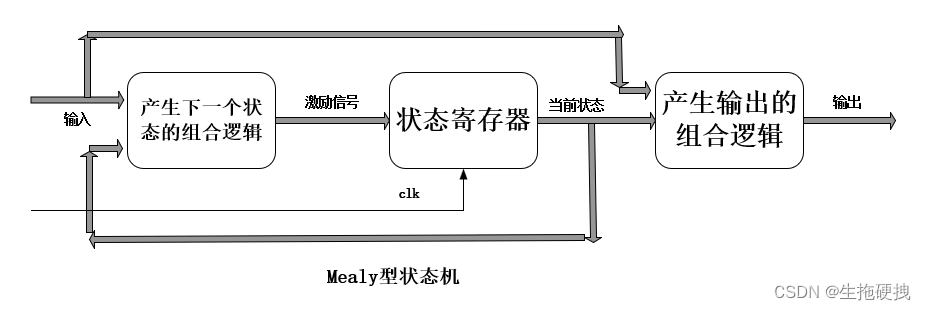

Mealy型状态机

与Moore型状态机不同,Mealy型状态机的输出不仅与当前状态有关,还取决于当前的输入信号。这意味着Mealy型状态机的输出可以在输入信号变化以后立刻发生变化,且输入变化可能出现在任何状态的时钟周期内。因此,同种逻辑下,Mealy型状态机输出对输入的响应会比Moore型状态机早一个时钟周期。由于Mealy型状态机对输入信号的即时响应,它通常用于对响应时间要求较高的场合。

(3)代码

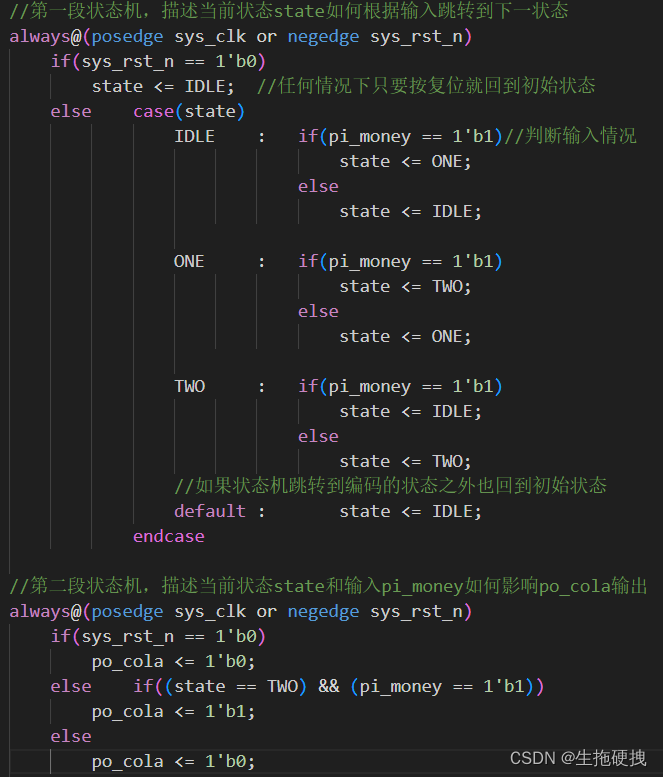

在FPGA设计当中,状态机分为mealy型与moore型两类,而状态机的编码风格有一段式、二段式、三段式三类。但在FPGA设计中状态机大多为mealy状态机,同时使用二段式编码较多,因此,我们选择6种方式中的mealy型二段式编码风格的状态机。

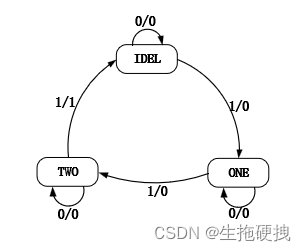

状态转换图

对应的状态转换图的状态机代码

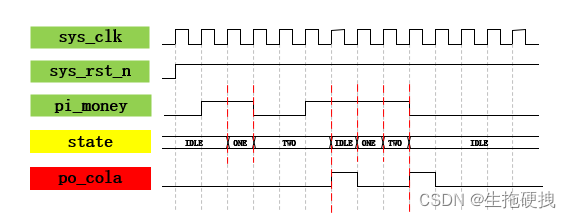

状态机波形图

(4)分析

由(3)可知,状态机代码符合第一幅的状态图,同时第三幅图为其对应的波形图。其中,state的初始状态为IDLE,当pi_money为1时,状态由IDLE转向ONE;若pi_money再为1,状态由ONE进入到TWO;pi_money再为1,状态回到IDLE;其他情况的话,状态保持原状态不变(注意:不一定是保持不变,该处保持不变是依据题目实际才保持不变的,对于其他情况,可能会发生变化)。当然,大家最好去具体了解下所有种类的状态机的区别。

最后,FPGA必备基础部分到此就结束了,初学者理论上只要搞懂这9个基础知识,就能进行FPGA的自我设计。愿诸君武运昌隆。

本文介绍了FPGA设计中的基本概念,包括计数器和状态机,重点区分了Moore型和Mealy型状态机的工作原理及特点。通过实例展示了状态转换图、代码和波形图,强调了理解和掌握状态机编码风格对FPGA设计的重要性。

本文介绍了FPGA设计中的基本概念,包括计数器和状态机,重点区分了Moore型和Mealy型状态机的工作原理及特点。通过实例展示了状态转换图、代码和波形图,强调了理解和掌握状态机编码风格对FPGA设计的重要性。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?