目录

该部分就是将前面所讲的非阻塞赋值、阻塞赋值与always块联系起来,为什么要这么做?是因为我们在编写FPGA代码时,它们之间的关系及对应的波形图是最最基础的,你不理解它,那么很不幸,你还是转换赛道,去干其他专业吧。

always块与阻塞赋值的关系

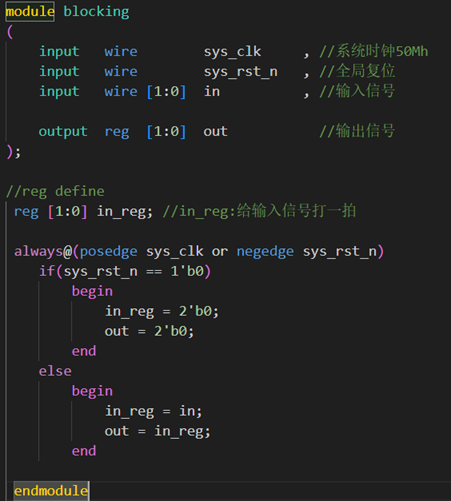

(1)代码见下图。

always块与阻塞赋值的关系代码

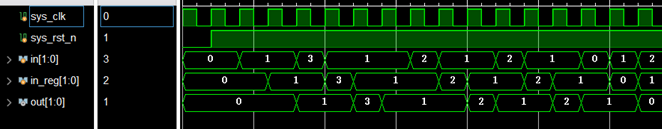

always块与阻塞赋值的关系代码波形图

(2)详细分析

2.1 中间信号in_reg

在系统时钟下,这里的in_reg信号用于接收in信号的值。同理,in_reg是上文reg型的寄存器,导致in_reg信号会“打一拍”,在第二个时钟上升沿才会更新,即in_reg信号比in信号晚一个时钟周期。

2.2 输出信号out

在系统时钟下,这里的out信号用于接收in_reg信号的值。但是,由于是阻塞赋值(其会立即更新值,而且在这里“打一拍”在in_reg信号已经发生作用了,因此不用考虑,但也要注意要out信号要接的是in信号的中间信号才行,其他信号的中间变量不行,具体看前面的文章),因此out信号会紧随in_reg信号更新,体现为out与in_reg信号波形图对齐,也是在第二个时钟上升沿更新。

always块与非阻塞赋值的关系

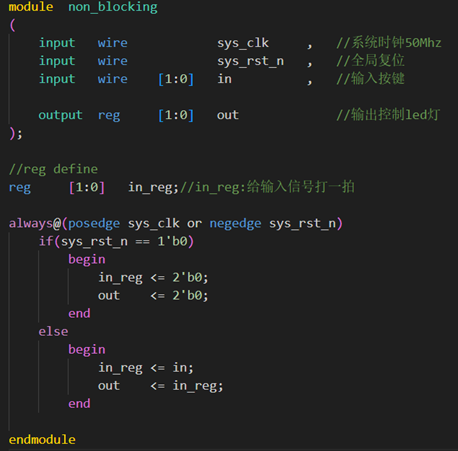

(1)代码见下图。

always块与非阻塞赋值的关系代码

always块与非阻塞赋值的关系代码波形图

(2)详细分析

2.1 中间信号in_reg

在系统时钟下,这里的in_reg信号用于接收in信号的值。同理,in_reg是上文reg型的寄存器,导致in_reg信号会“打一拍”,在第二个时钟上升沿才会更新,即in_reg信号比in信号晚一个时钟周期。

2.2 输出信号out

在系统时钟下,这里的out信号用于接收in_reg信号的值。但是,由于是非阻塞赋值(其不会立即更新值,而且在这里“打一拍”在in_reg信号已经发生作用了,因此不用考虑,但也要注意要out信号要接的是in信号的中间信号才行,其他信号的中间变量不行,具体看前面的文章),因此out信号会延迟in_reg信号一个时钟周期更新,体现为out比in_reg信号波形图晚一个时钟周期,即在第三个时钟上升沿更新。

补充

即在上面in_reg、out两个变量中,由in信号传给in_reg信号的第一步只考虑前文寄存器的作用(不论赋值符号是阻塞还是非阻塞),第二步的in_reg信号传给out信号才考虑阻塞与非阻塞赋值的特性。

同时,在上面只是列出了always敏感列表中为边沿触发的情况,并没有电平触发的情况,电平触发大家就自己去敲一下就知道了。

本文详细分析了always块中阻塞赋值与非阻塞赋值的区别,以及它们如何影响中间信号in_reg和输出信号out。阻塞赋值使out紧跟in_reg更新,而非阻塞则延迟一个时钟周期。这对于理解和编写FPGA代码至关重要。

本文详细分析了always块中阻塞赋值与非阻塞赋值的区别,以及它们如何影响中间信号in_reg和输出信号out。阻塞赋值使out紧跟in_reg更新,而非阻塞则延迟一个时钟周期。这对于理解和编写FPGA代码至关重要。

1290

1290

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?