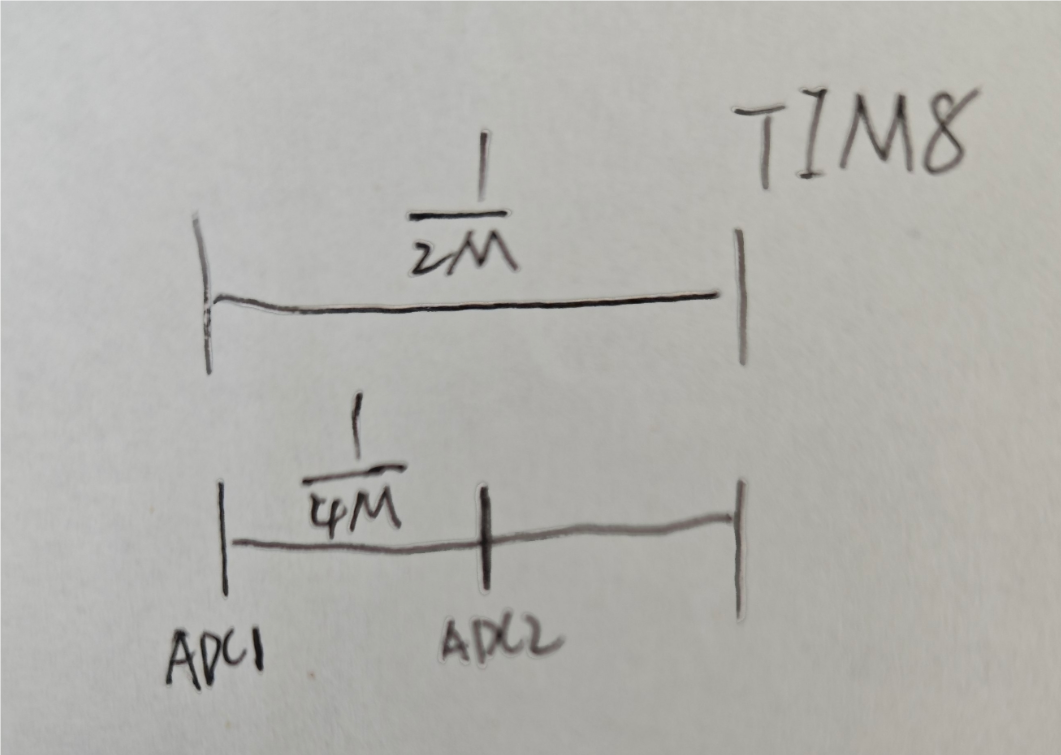

STM32G474 CubeMX + CLion双重ADC交替采样实现2M+2M = 4M采样率

文章目录

前言

并非所有通道都有三重ADC的采样,笔者之前配过G474RET6,找了半天最多只有双重,没有三重。

换了H750发现也只有引脚支持三重ADC ,而F407有不知道多少引脚能够三重。怪不得那么多人买F407。

1.cube配置

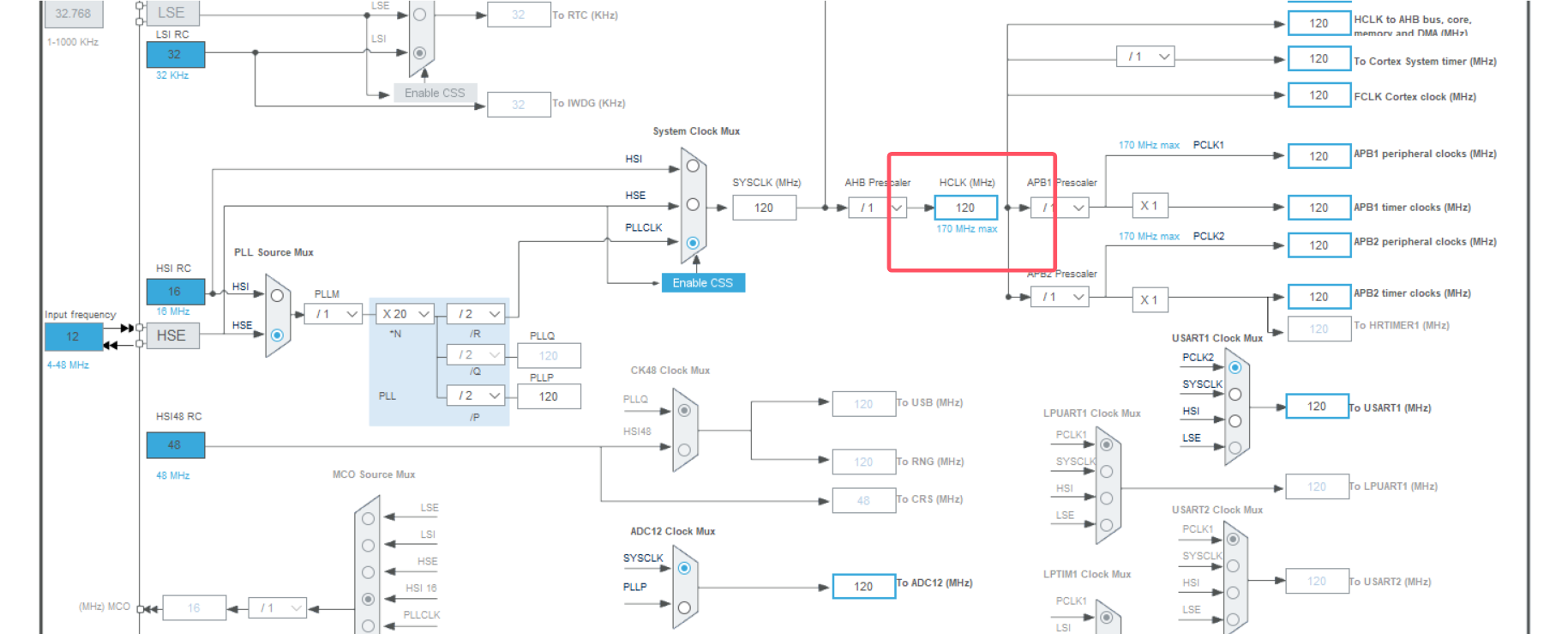

都用上交替采样了,时钟就配成120M,方便后面的ADC2分频

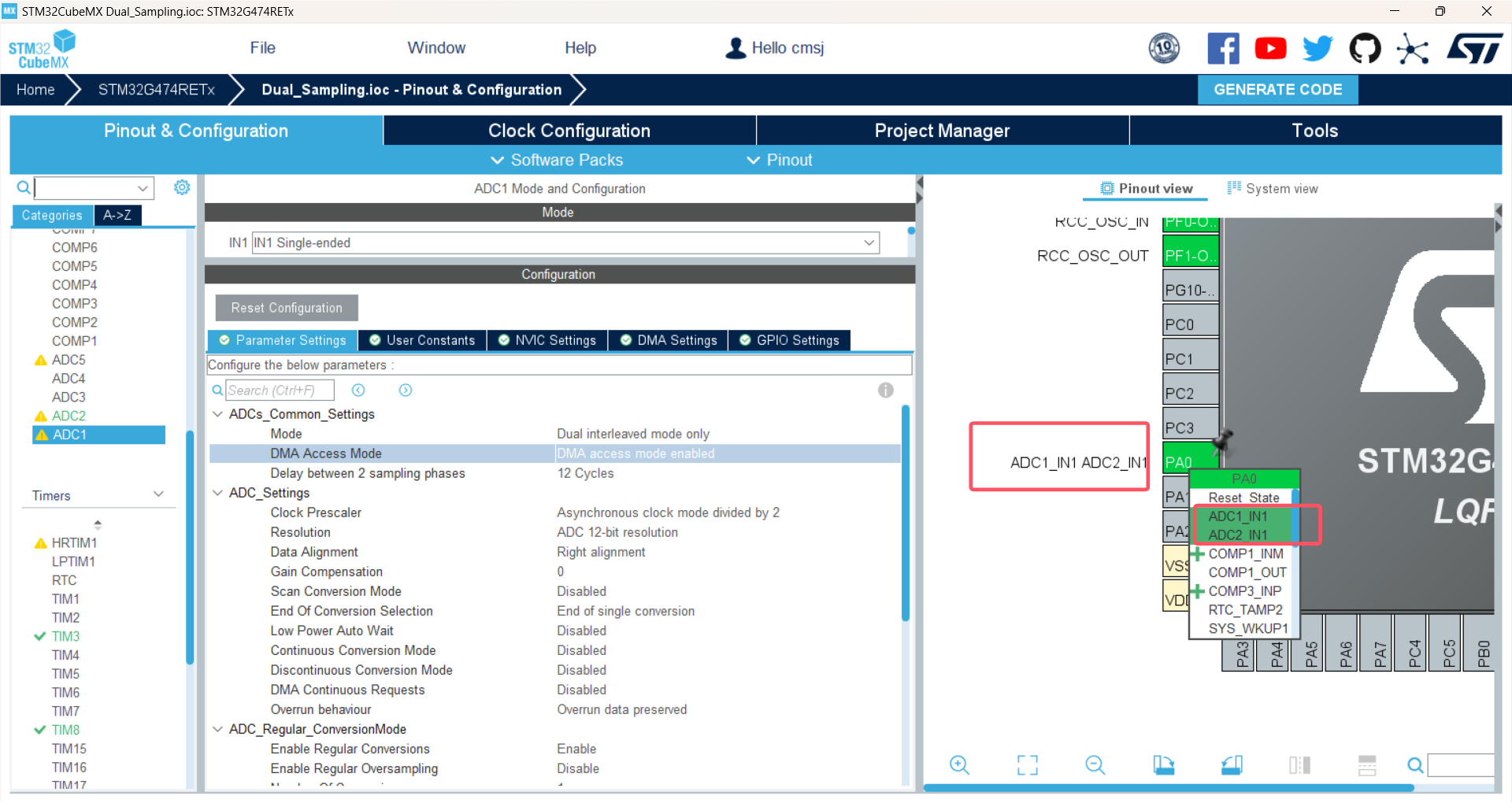

然后引脚这边加上ADC1和ADC2

也可以不选A0做双重,选其他引脚也可以。

记得选完在左边的ADC中使能这个通道。

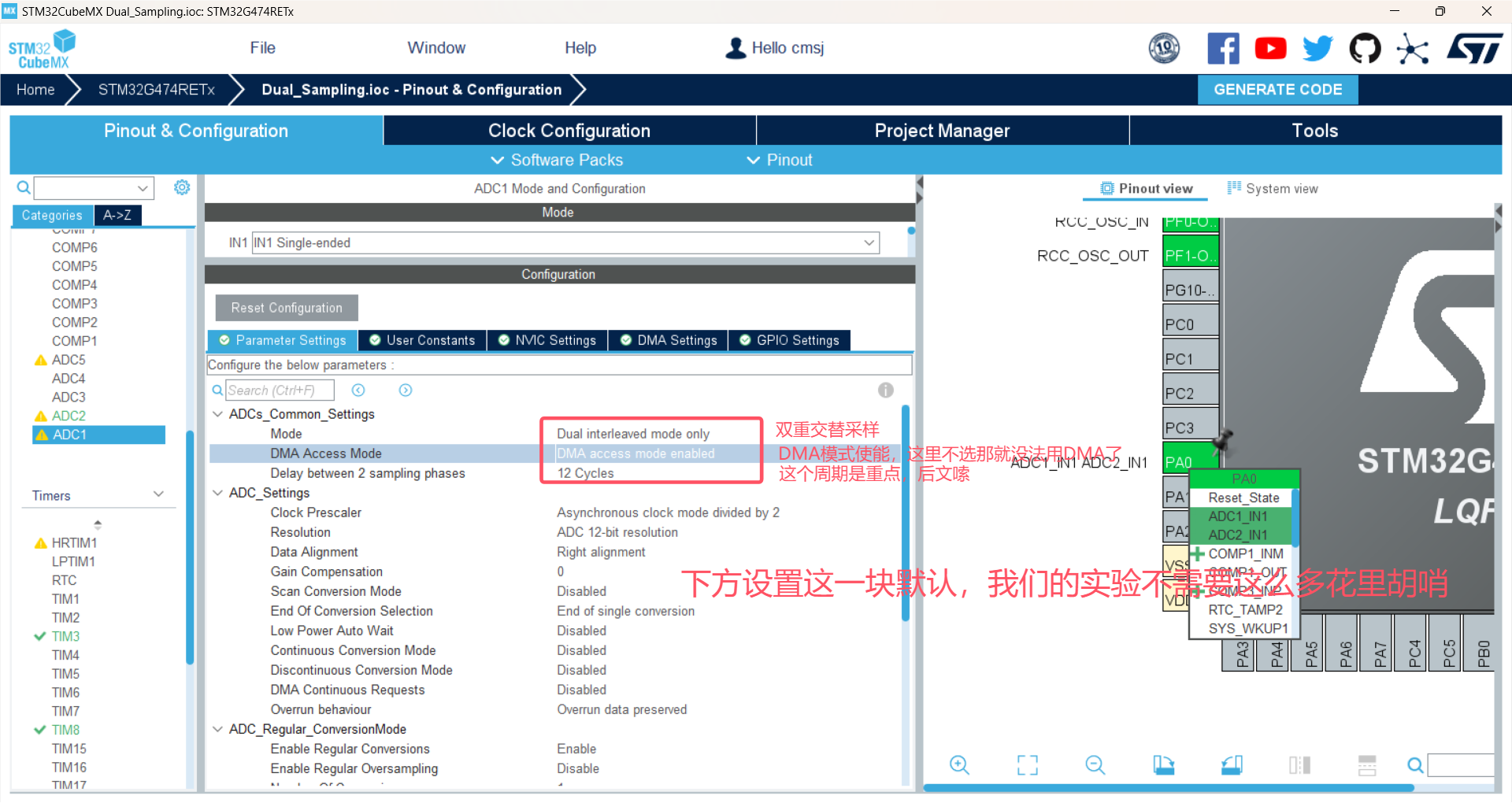

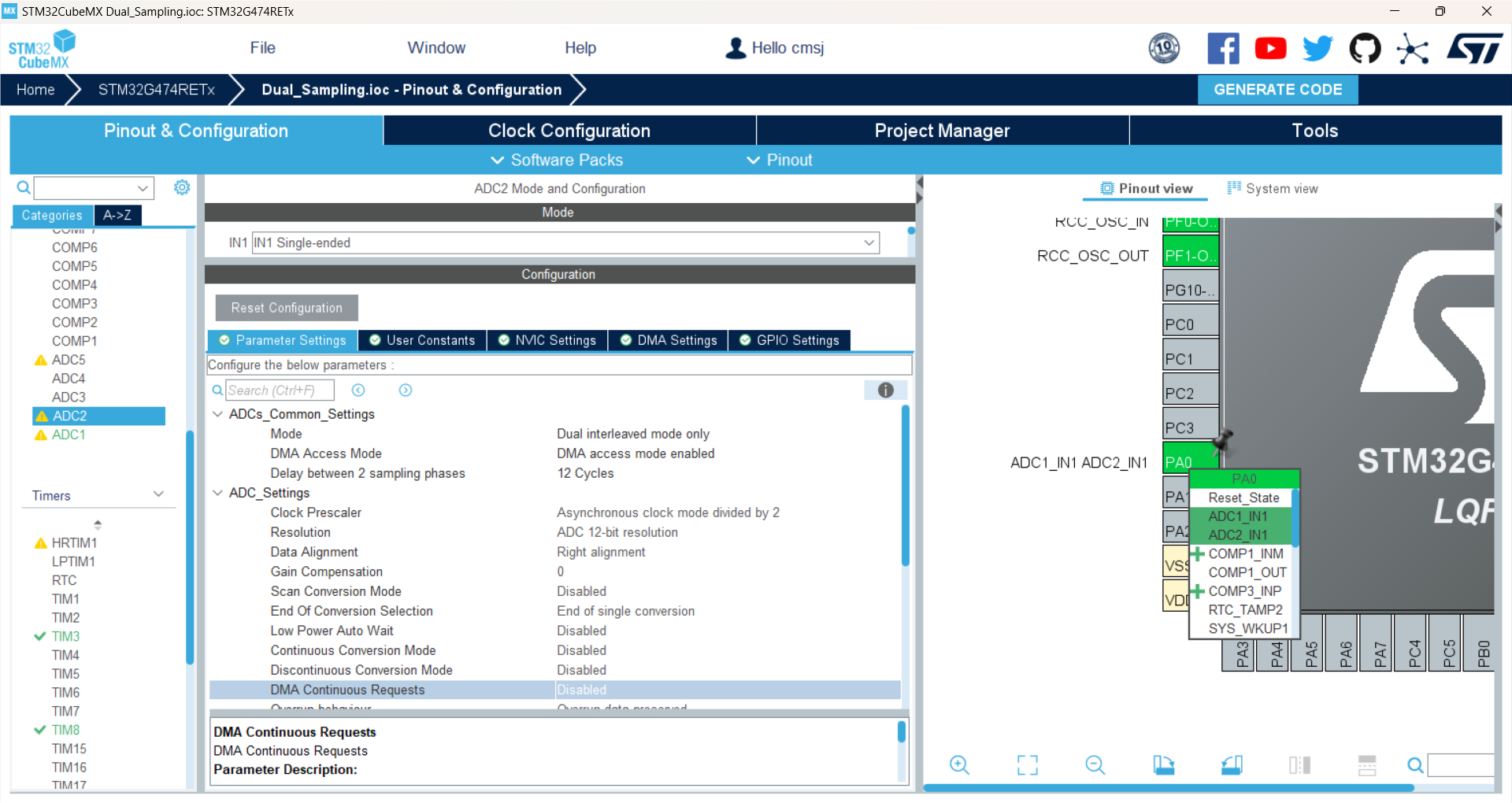

1.1配置下ADC

注意到这里用的定时器8,因为手头这块板子似乎TIM3有问题,没法用来做触发ADC

ADC2不用配,已经帮你同步成跟ADC1一样了

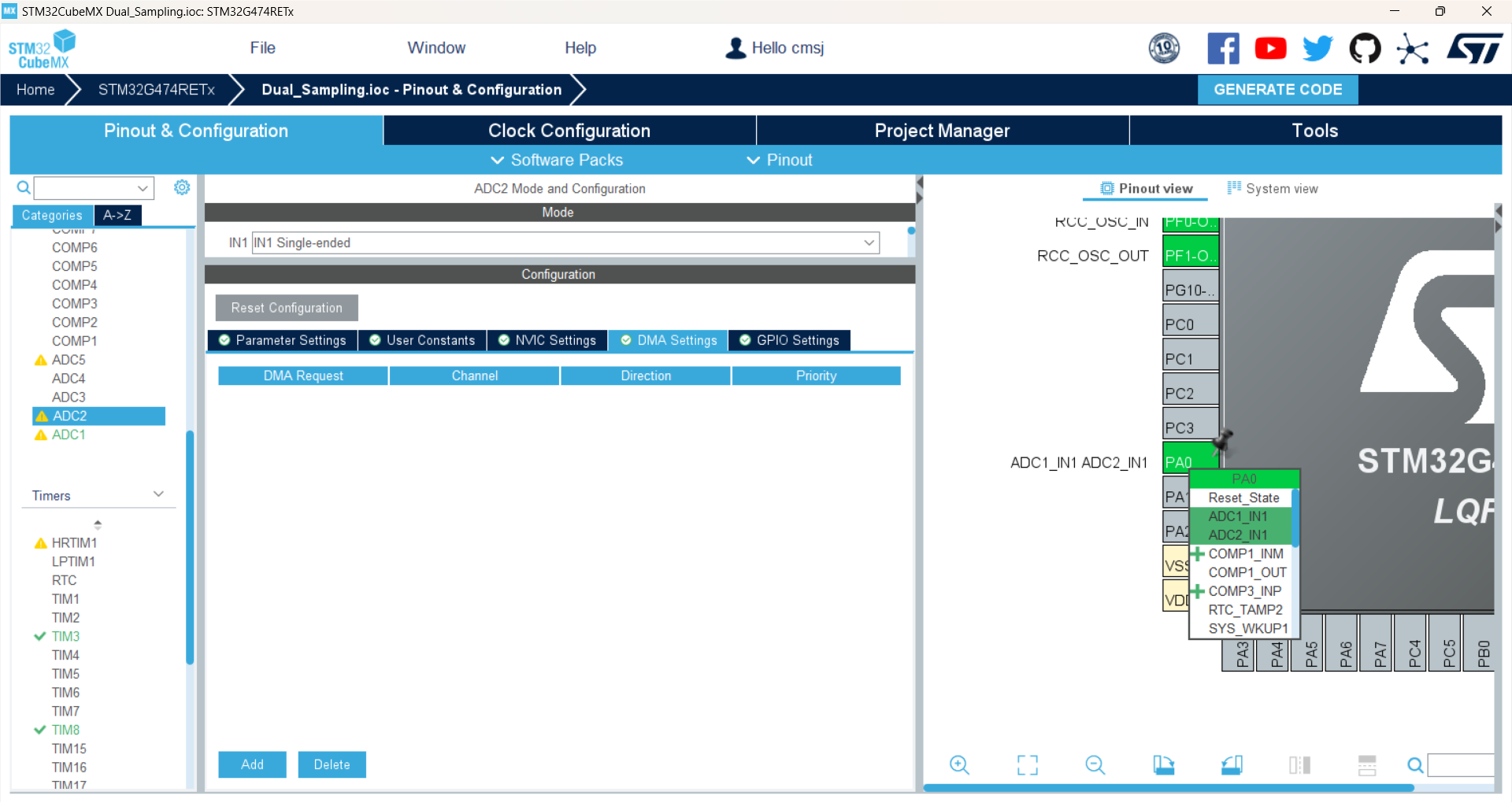

1.2接下来配置DMA

注意选全字,交替模式DMA的数据存在一个32位数组中,其中低16位是ADC1,高16位是ADC2。就随便试验下,DMA配成NOMAL。channel随便选一个。

ADC2的DMA不用配,一个DMA搬运完ADC1的就去搬运ADC2的,如果配置了那么对不起,高16位就没数据了。

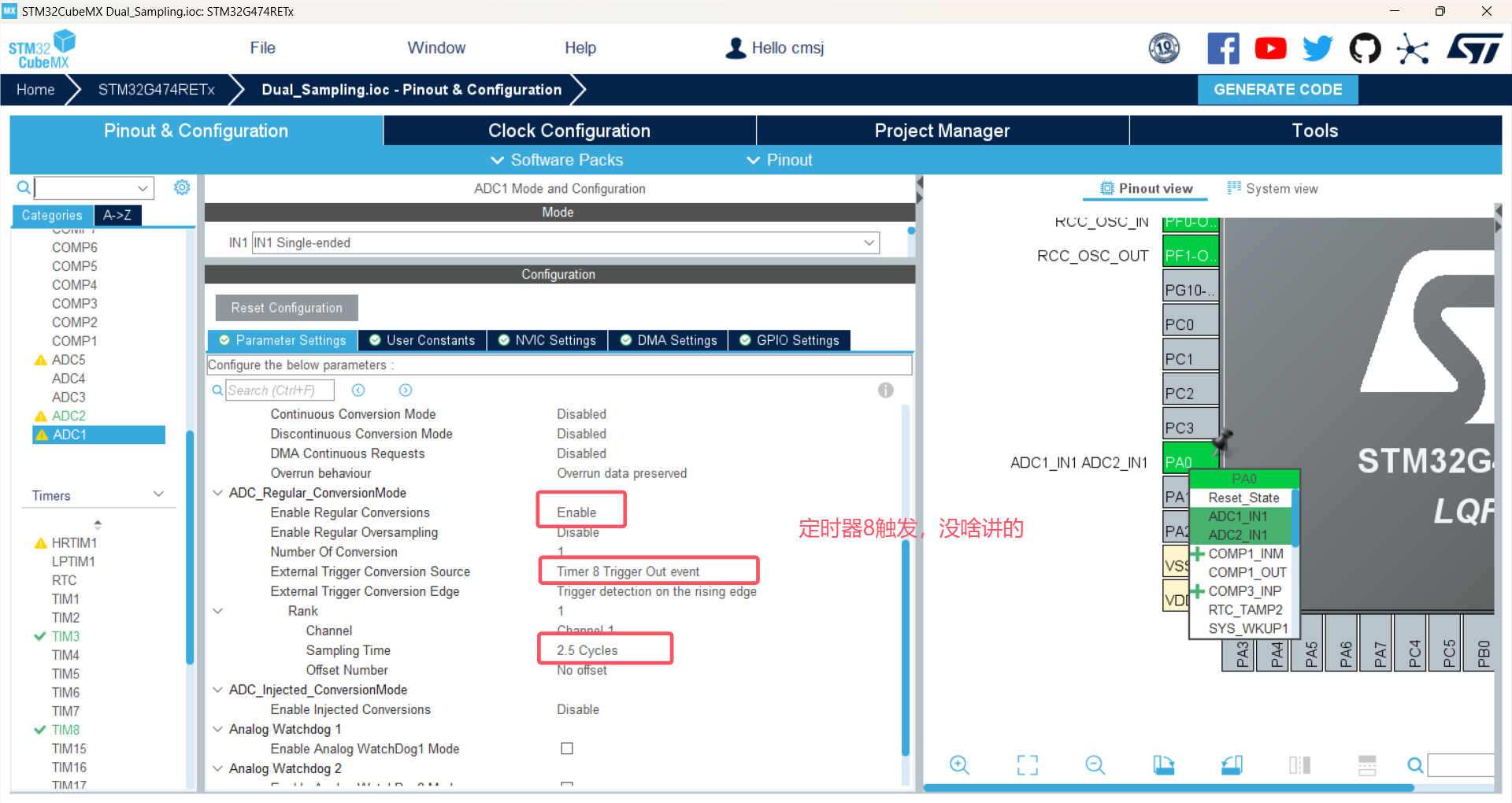

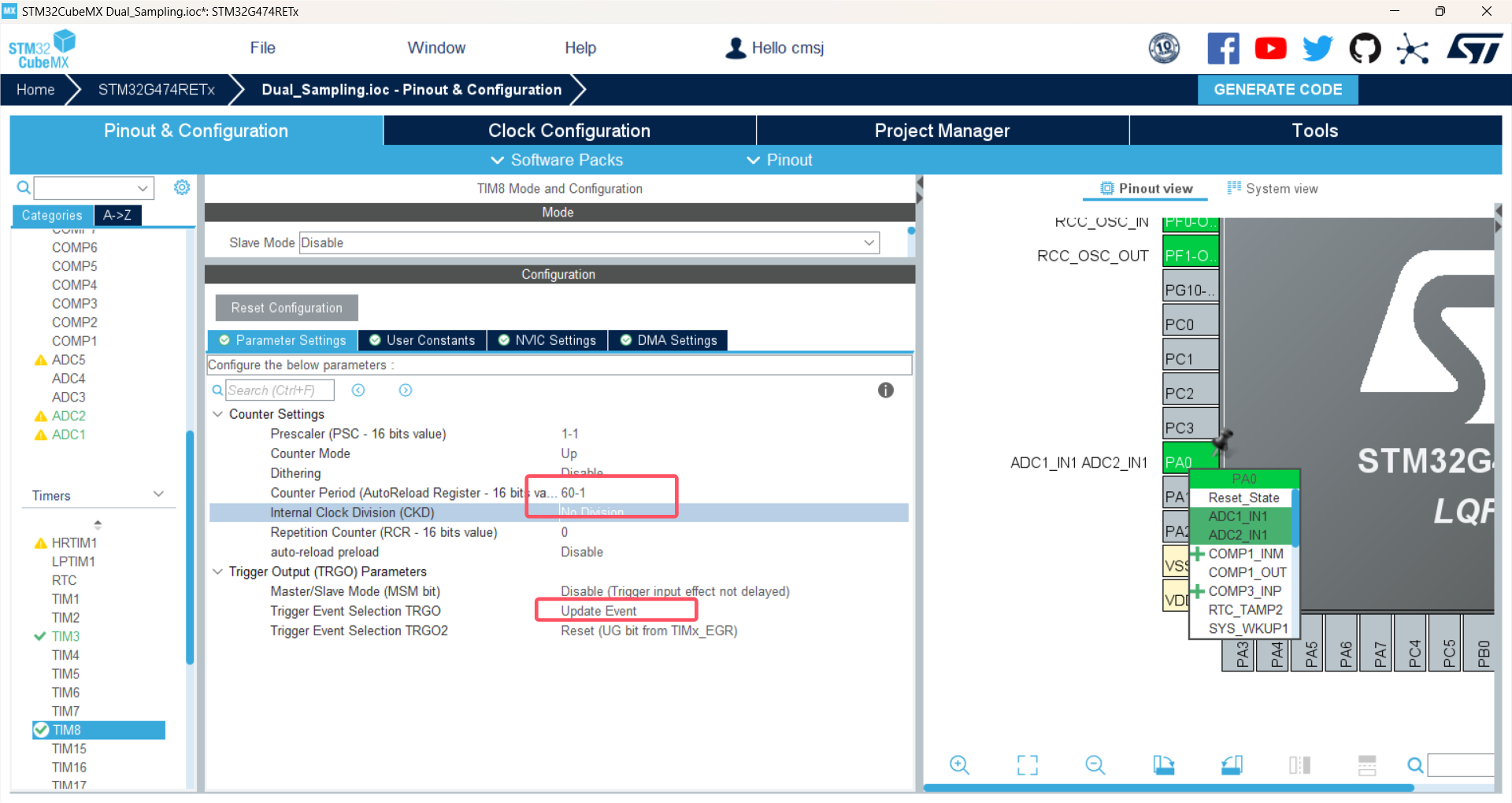

1.3定时器(重要)

这边配置上2M频率,然后我们讲下之前为什么要配成12cycle。

首先明确下,cycle就是ADC时钟经过分频后的数值,也就是说,我们120M经过二分频,60M就是者的cycle。

同时,ADC双重采样,是ADC1先采样,经历了采样时间与等待时间后,再经历这个Delay between 2 sampling phases,然后轮到ADC2采样,ADC2经历采样时间与等待时间,然后就是等待下一次TIM8的上升沿到来。

所以我们知道了,这里的 Delay between 2 sampling phases 最好正好是定时器频率的两倍,也就是说

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

3110

3110

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?