实验一 运算器组成实验

- 实验目的

⑴熟悉逻辑测试笔的使用方法。

⑵熟悉 TEC-8 模型计算机的节拍脉冲 T1、T2、T3;

⑶熟悉双端口通用寄存器组的读写操作;

⑷熟悉运算器的数据传送通路;

⑸验证 74LS181 的加、减、与、或功能;

⑹按给定的数据,完成几种指定的算术、逻辑运算运算。

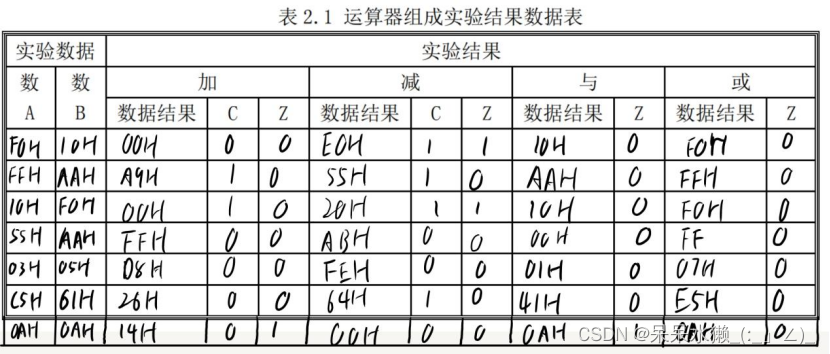

- 实验结果

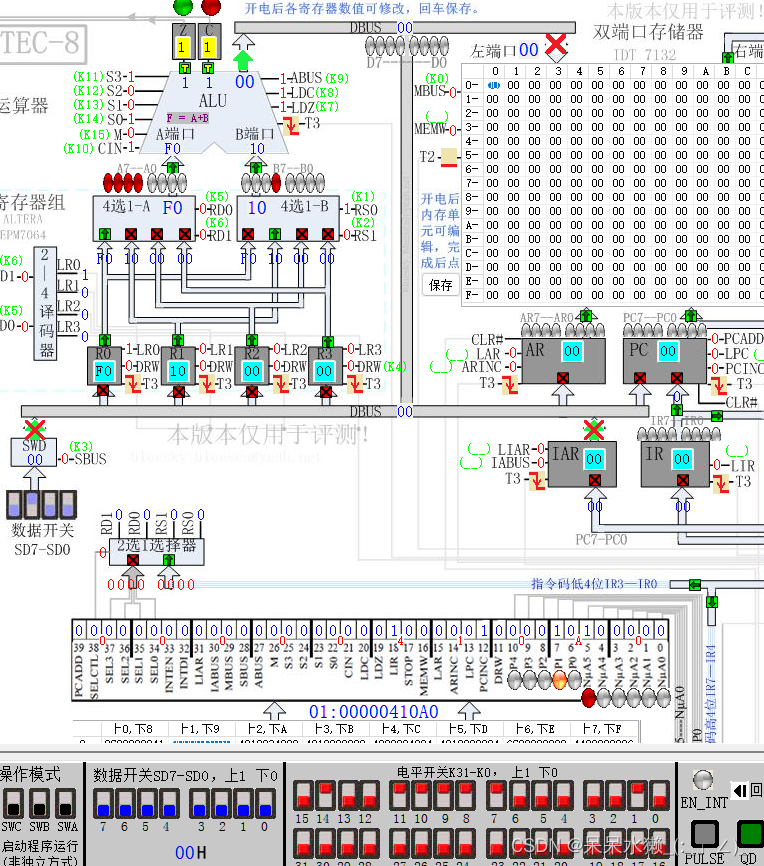

设置初始值后,进行加法运算

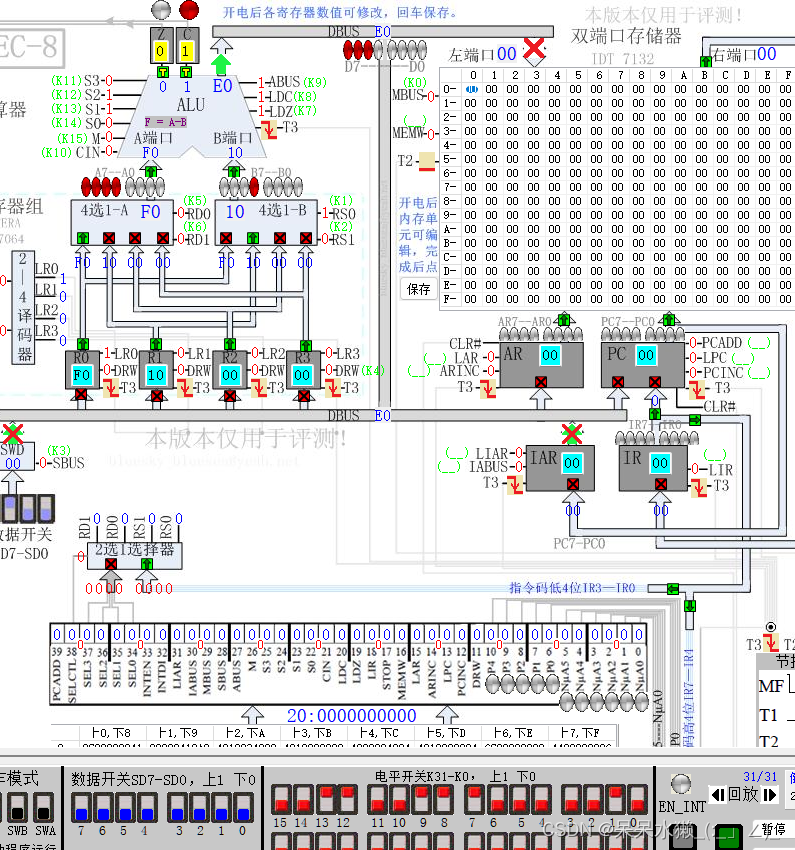

进行减法运算

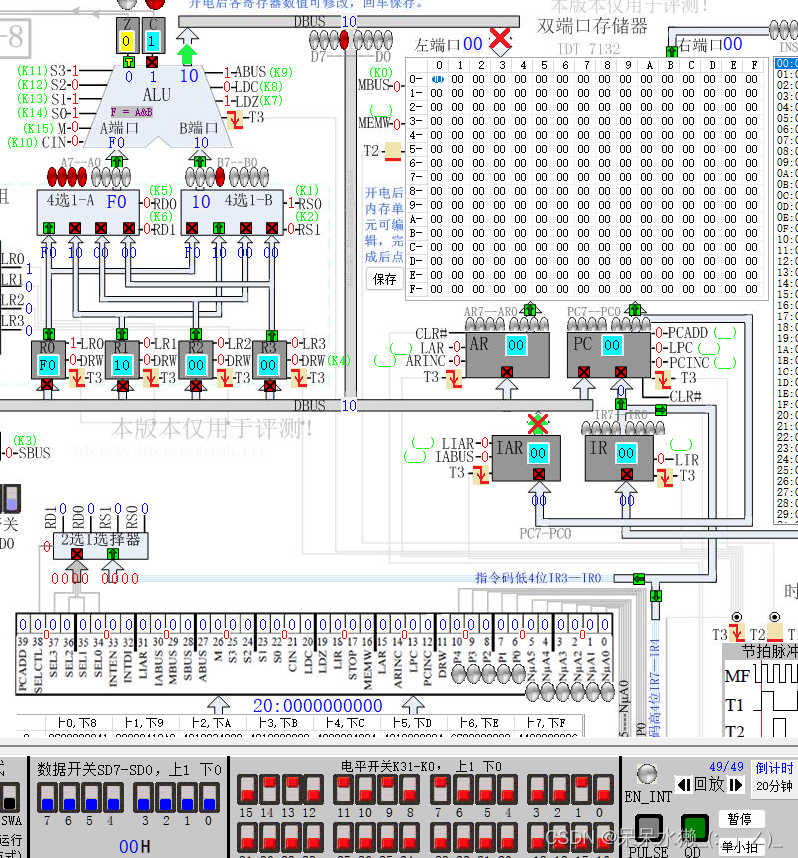

进行与运算

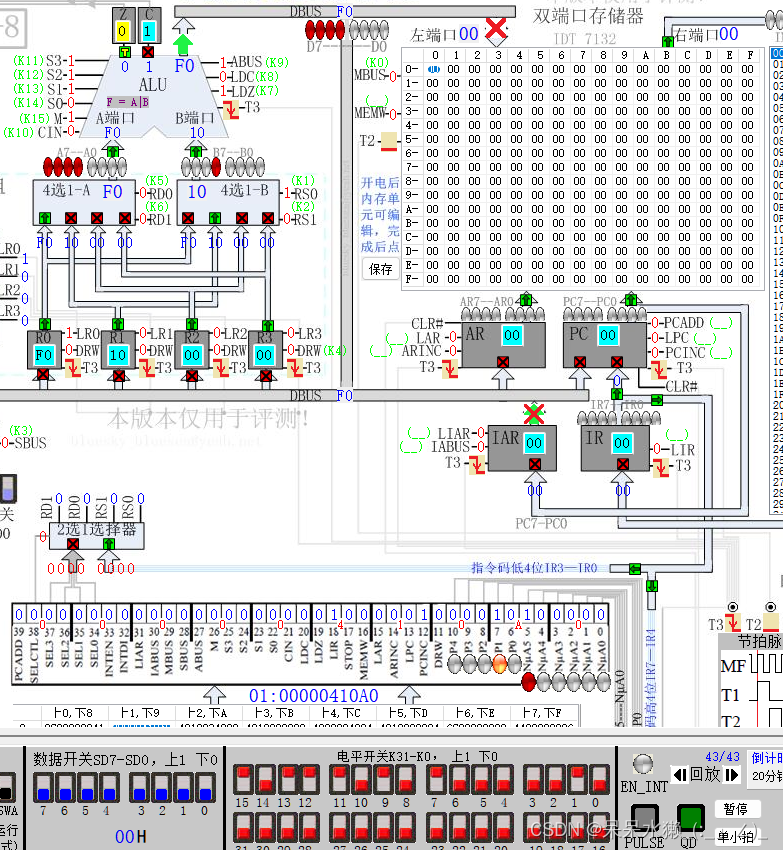

进行或运算

- 解释

结合实验现象,每一实验步骤中,对下述信号在所起的作用进行解释:M、S0、S1、S2、S3、CIN、ABUS、LDC、LDZ、SEL3、SEL2、SEL1、SEL0、DRW、SBUS。并说明在该步骤中,哪些信号是必需的,哪些信号不是必需的,哪些信号必需采用实验中使用的值,哪些信号可以不采用实验中使用的值

M:控制运算模式,加减法时M=0 为算术运算;与或运算时M=1为逻辑运算;

S0、S1、 S2、S3:控制 74LS181 的运算类型 实现加减与或的运算控制。

CIN:低位 74LS181 的进位输入

ABUS:控制信号输出=1 时,将运算结果送数据总线 DBUS

LDC:控制输出端C的值是否送到寄存器。=1 时,在 T3 的上升沿将运算得到的进位保存到 C 标志寄存器。

LDZ:控制输出端Z的值是否送到寄存器。=1 时,如果运算结果为 0,在 T3 的上升沿,将 1 写入到 Z 标志寄存器;如果运算结果不为 0,将 0 保存到 Z 标志寄存器。

SEL3、SEL2:选择送 ALU 的 A 端口的寄存器

SEL1、SEL0:选择送 ALU 的 B 端口的寄存器

DRW:控制信号是否写入寄存器。=1 时,在 T3 上升沿对 RD1、RD0 选中的寄存器进

行写操作,将数据总线 DBUS 上的数 D7~D0 写入选定的寄存器

SBUS:控制是否写入DBUS。=1 时,将运算结果送数据总线 DBUS =0 时,禁止运算结果送数据总线 DBUS

| M | S0~S3 | CIN | LDC | LDZ | SEL3~SEL0 | DRW | SBUS | ABUS | |

| 写入数据到R0 | 为0,也可为其他值 | 为0000B也可为其他值 | 为0,也可为其他值 | 为0,也可为其他值 | 为0,也可为其他值 | 为0001B | 为1,读取总线数值并写入数据 | 为1,用以设定初始值并导入总线 | 必需为0 |

| 写入数据到R1 | 为0,也可为其他值 | 为0000B也可为其他值 | 为0,也可为其他值 | 为0,也可为其他值 | 为0,也可为其他值 | 为0001B | 为1,读取总线数值并写入数据 | 为1,用以设定初始值并导入总线 | 必需为0 |

| 加法运算 | 必需为0 | 为1001B,控制运算器为加法 | 必需为1 | 为1,输出C | 为1,输出Z | 为0001B | 必需为0,终止输入 | 必需为0,终止输入 | 为1,输出结果到总线 |

| 减法运算 | 必需为0 | 为0110B,控制运算器为减法 | 必需为0 | 为1,输出C | 为1,输出Z | 为0001B | 必需为0,终止输入 | 必需为0,终止输入 | 为1,输出结果到总线 |

| 与运算 | 必需为1 | 为1011B,控制运算器为与运算 | 必需为0 | 为0,不用输出 | 为1,输出Z | 为0001B | 必需为0,终止输入 | 必需为0,终止输入 | 为1,输出结果到总线 |

| 或运算 | 必需为1 | 为1110B,控制运算器为或运算 | 必需为0 | 为0,不用输出 | 为1,输出Z | 为0001B | 必需为0,终止输入 | 必需为0,终止输入 | 为1,输出结果到总线 |

四、思考探究

1.ALU 具有记忆功能吗?如果有,如何设计?

2.为什么在 ALU 的 A 端口和 B 端口的数据确定后,在数据总线 DBUS 上能够直接观测运算的 数据结果,而标志结果却在下一步才能观测到?

答:

具有,通过ABUS信号关闭输出端,将数据暂存在ALU中,实现记忆功能。

在ALU的输出端,C和Z的输出受LDC和LDZ的控制,在每次输出前会进行信号判断,所以要在下一步才能观测到。

五、独立方式

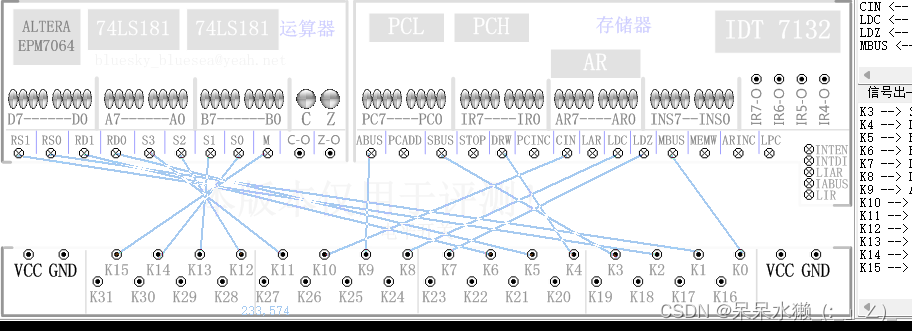

连线

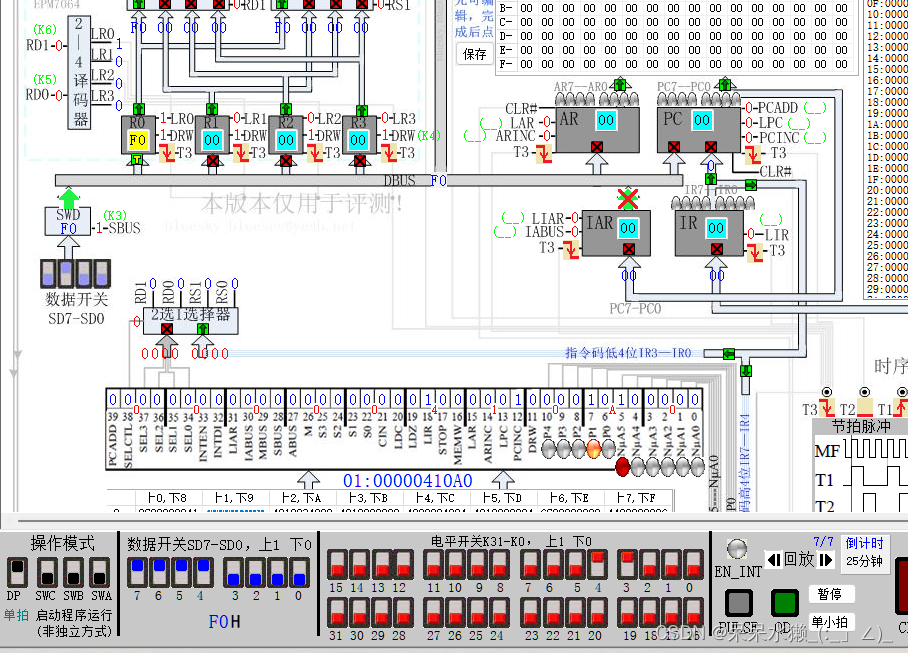

为R0设置初始值

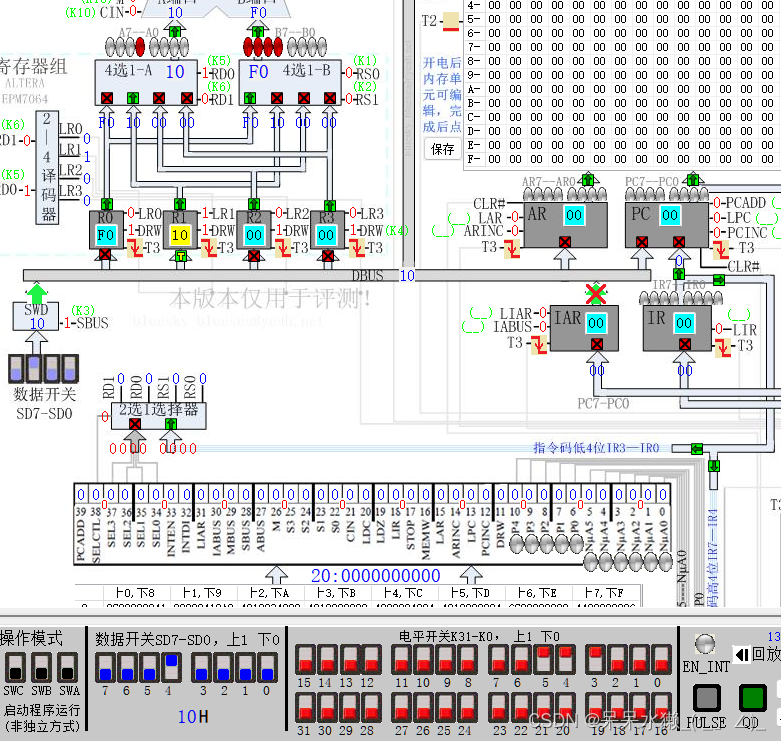

为R1设初始值

加法运算

减法运算

与运算

或运算

本文详细介绍了运算器组成实验的目的及过程,包括逻辑测试笔的使用、TEC-8模型计算机的节拍脉冲理解、双端口通用寄存器组的读写操作等,并深入分析了74LS181的加、减、与、或功能验证及其信号控制作用。

本文详细介绍了运算器组成实验的目的及过程,包括逻辑测试笔的使用、TEC-8模型计算机的节拍脉冲理解、双端口通用寄存器组的读写操作等,并深入分析了74LS181的加、减、与、或功能验证及其信号控制作用。

4万+

4万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?